一、概述

LUT中文名字叫查找表。以7系列的FPGA為例,每一個Slice里面有四個LUT。FPGA就是通過LUT實現大量的組合邏輯,以及SLICEM里面的LUT還可以構成RAM,Shift Register,以及Multiplexers。這篇文章我們一起來學習LUT如何構成組合邏輯。

二、LUT實現原理

LUT,中文名字叫做查找表,其原理其實也就是一個一個查找表,根據輸入去找到相應位置的信號,然后做輸出。說白了就好像一個小容量的ROM,把輸入當作地址信號,對LUT里面預存的內容進行尋址。

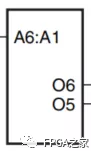

7系列的FPGA的LUT有6個輸入端口(A1-6),然后有兩個輸出端口(O5,O6)。下圖是SLICEL里面的LUT。

其可以實現6輸入的布爾組合邏輯函數,輸入信號為A1,A2,A3,A4,A5,A6,輸出端口為O6。如下

O6=f(A1,A2,A3,A4,A5,A6)

其實現方式就是將輸入(A1,A2...A6)對應的輸出在LUT里面預存好(這一步在我們用bit文件配置FPGA時實現),然后把輸入信號當作地址信號去把對應的輸出信號調出來。

同樣其還可以構成兩個5輸入的布爾組合邏輯函數,其中這兩個函數共用5個輸入信號(A1,A2,A3,A4,A5),A6被拉高,O5,O6分別是兩個布爾邏輯的輸出。

O5=f(A1,A2,A3,A4,A5)

O6=f(A1,A2,A3,A4,A5)

故這也相當于實現的是一個5輸入2輸出的邏輯函數。

[O5,O6]=f(A1,A2,A3,A4,A5)

三、總結與提升

總結一下,就好比單個LUT里面可以預存 2^6=64個結果。那么單個LUT可以實現

(1)輸入信號最多為6bit,輸出信號為1bit的的布爾邏輯函數;

(2)輸入信號最多為5bit,輸出信號為2bit的邏輯。

一個SLICE里面有四個LUT故最多可以預存的輸出信號個數為 2^6*4=2^8。

因此在一個SLICE里面,借助選擇器將多個LUT進行互連,可以實現輸入數,輸出數最多為如下所示的邏輯。

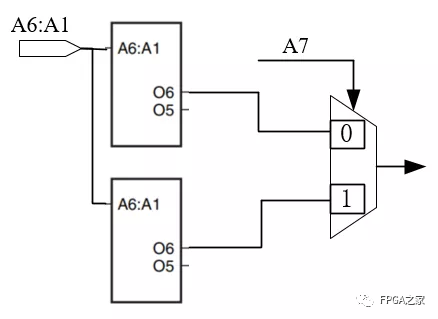

(1)2個LUT通過互連可以構成7bit輸入,單bit輸出的邏輯。實現方式為兩個LUT的輸入信號A1,A2,A3,A4,A5,A6接到一起,輸出信號經過選擇器選擇輸出,選擇器的選擇信號也是邏輯函數的一個輸入信號。

將邏輯函數的輸出送到Storage Element便可以形成同步時序邏輯。

(2)4個LUT通過互連可以構成8bit輸入,單bit輸出的邏輯。實現方式大家可以根據上面的實現方式自行推理。

(3)2個LUT通過互連可以構成6bit輸入,2bit輸出的邏輯。實現方式自行推理。

(4)4個LUT通過互連可以構成7bit輸入,2bit輸出的邏輯。實現方式自行推理。

超過8輸入的布爾邏輯就需要多個SLICE來實現。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1643文章

21974瀏覽量

614342 -

邏輯函數

+關注

關注

1文章

23瀏覽量

9593 -

組合邏輯

+關注

關注

0文章

48瀏覽量

10177 -

LUT

+關注

關注

0文章

50瀏覽量

12777 -

CLB

+關注

關注

0文章

29瀏覽量

6099

原文標題:初識FPGA CLB之LUT實現邏輯函數

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA從0到1學習資料集錦

MIMXRT1176如何在MBDT中正確實現自定義LUT?

fpga和cpu的區別 芯片是gpu還是CPU

XILINX FPGA CLB單元之移位寄存器

初識FPGA CLB之LUT實現邏輯函數

初識FPGA CLB之LUT實現邏輯函數

評論