FPGA 通過查找表 (LUT) 實現(xiàn)邏輯功能。這些 LUT 類似于真值表或卡諾圖 (Karnaugh map),F(xiàn)PGA 可以通過組合多個 LUT ,來實現(xiàn)幾乎任何你所需的邏輯功能。

通常情況下,LUT 由其可處理的輸入數(shù)來指定。例如,一個 4 輸入 LUT 需要 16 位來存儲這 4 個輸入所有可能組合對應(yīng)的輸出值。而對于需要 4 個以上輸入的邏輯,則需要進(jìn)行 LUT 級聯(lián),但 LUT 級聯(lián)會造成傳播時延。

使用較大的 LUT 可以減少所需的 LUT 層數(shù),從而提高性能,但對于簡單的邏輯功能來說,LUT 過大同樣可能會造成浪費(fèi)。為了盡量減少浪費(fèi),可以對這些 LUT 進(jìn)行拆分,如何拆分 LUT 會對設(shè)備的整體利用率產(chǎn)生重要影響。

接下來就跟隨小編一起,來探討幾種權(quán)衡取舍的方案。

查找表的實現(xiàn)

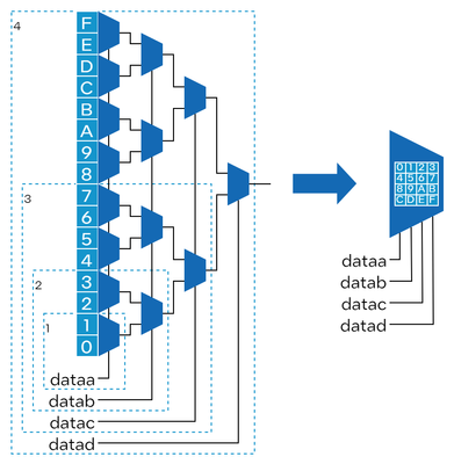

首先,讓我們來看看通用 n 輸入查找表的結(jié)構(gòu)。查找表是一系列多路復(fù)用器,它們根據(jù)輸入選擇特定的存儲位置,就像 1 位存儲器。所需的存儲位置數(shù)是 2 的輸入數(shù)次冪,就像有 n 根地址引腳的存儲器。

下圖是一個 4 輸入 LUT 的示例,其中較小的 LUT 用虛線邊框表示。在下文中,我們將使用 4 輸入 LUT 的簡化表示法來繼續(xù)進(jìn)行探討。

圖 1. n 輸入 LUT

增加輸入位可以實現(xiàn)更加復(fù)雜的邏輯,但每增加一個輸入位,所需的存儲位和多路復(fù)用器的數(shù)量就會翻倍。在實現(xiàn)較為簡單的邏輯時,這些額外的資源就會被浪費(fèi)。為了盡量減少輸入位的浪費(fèi),可以為中間多路復(fù)用器提供抽頭 (tap)。

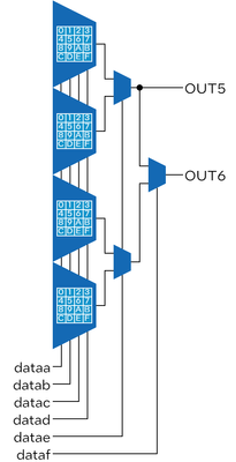

下圖展示的是具有兩個 5 輸入 LUT 輸出的 6 輸入 LUT。通過這種簡單的方法可以實現(xiàn)兩個 5 輸入 LUT,但局限性在于,兩個 LUT 均由相同的 5 個輸入控制。

圖 2. 基本 6 輸入 LUT

更優(yōu)的方法

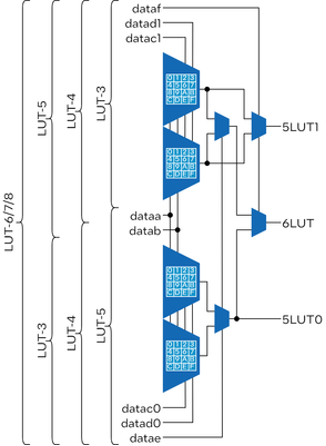

Agilex FPGA 采用了一種不同的方法,可以提高設(shè)備的利用率。如下圖所示,Agilex FPGA 采用全新的 6 輸入 LUT 結(jié)構(gòu),具有 8 個輸入,稱為自適應(yīng)邏輯模塊 (ALM)。部分較小 LUT 的輸入被獨(dú)立出來,以提供更高的靈活性。借助這些額外輸入,就可將依賴于不同信號的較小邏輯功能進(jìn)行組合。

下圖展示了一些不同的 LUT 組合方式。

圖 3. Agilex FPGA ALM

當(dāng) datac0 和 datad0 分別連接到與 datac1 和 datad1 相同的信號時,這一模塊就實現(xiàn)了傳統(tǒng)的 6 輸入 LUT,但將其進(jìn)行單獨(dú)使用時,還能實現(xiàn)一些 7 輸入和 8 輸入邏輯功能。

這些額外的 7 輸入和 8 輸入配置,再加上所有的 3 輸入、4 輸入和 5 輸入 LUT 配置,使得這種實現(xiàn)方式更加靈活,也提高了設(shè)備利用率。

對設(shè)備利用率的影響

這些優(yōu)勢究竟有何重要作用呢?要回答這個問題,我們需要一個指標(biāo)來反映所實現(xiàn)的邏輯數(shù)。理想的情況是使用一個常見的函數(shù)作為參考,比如處理器內(nèi)核,而且最好是一個大家熟悉并可以自由使用的處理器,例如 RISC-V 處理器。單個內(nèi)核通常不足以將 FPGA 填滿,因此需要一系列此類處理器,而且處理器應(yīng)足夠小,以便進(jìn)行細(xì)粒度比較。此外,還需要一個腳本將其進(jìn)行綜合。然而,由于所需條件較多,專業(yè)難度較高,這很難實現(xiàn)。

CoreScore 是專為 FPGA 及其綜合/布局布線工具設(shè)計的基準(zhǔn)評測體系。它能夠測試特定 FPGA 中可以容納的 SERV 內(nèi)核數(shù)。SERV 是一種屢獲殊榮的位串行 RISC-V 內(nèi)核,外形非常小巧。這就提供了一個獨(dú)立于供應(yīng)商的衡量指標(biāo),用于體現(xiàn) FPGA 的邏輯容量。

既然我們已經(jīng)確定了一個用于比較的指標(biāo),那就讓我們更深入地看看每種實現(xiàn)方式的邏輯容量。

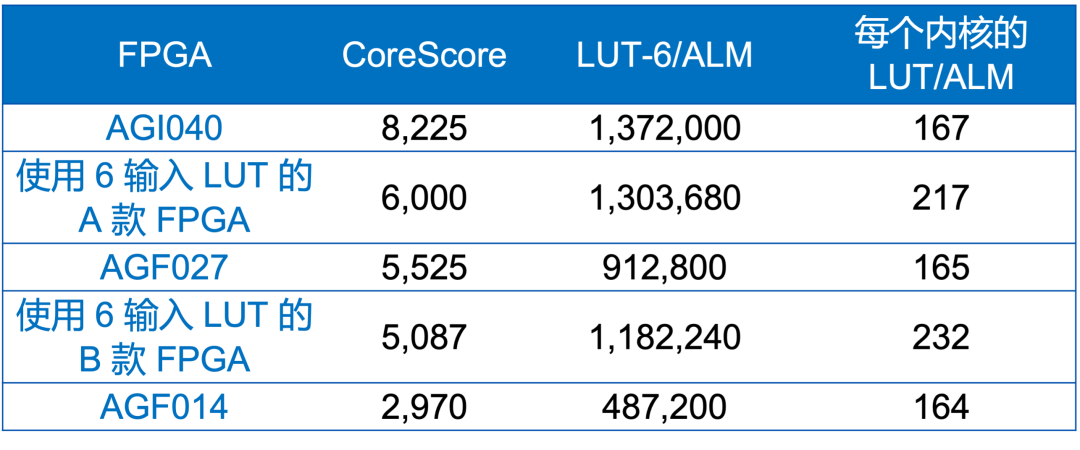

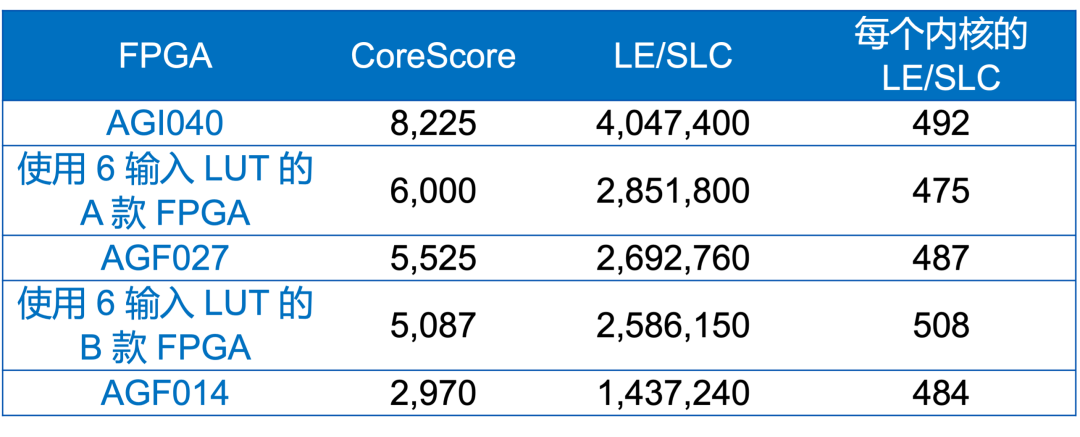

我們選擇了A、B 兩款使用基本 6 輸入 LUT 和提供可選 5 輸入 LUT 輸出的 FPGA 產(chǎn)品與使用上文所述的 8 輸入 ALM 配置的 Agilex 7 設(shè)備進(jìn)行了對比。

根據(jù) CoreScore.store 的結(jié)果可見,每個內(nèi)核需要超過 210 個基本可拆分 6 輸入 LUT,而 Agilex ALM 使用的 8 輸入配置只需要不到 170 個。

如果我們比較邏輯單元 (LE)/系統(tǒng)邏輯單元 (SLC) 的用量,情況則會不同。所有設(shè)備都需要約 490 LE/SLC +/-5%。這并非偶然,而是因為這些 FPGA 產(chǎn)品均針對其邏輯使用了比例因子,以便更準(zhǔn)確地反映其邏輯容量。

這些數(shù)據(jù)表明,邏輯單元和系統(tǒng)邏輯單元是衡量FPGA容量的有效指標(biāo)。數(shù)據(jù)還顯示,與傳統(tǒng)的 6 輸入結(jié)構(gòu)相比,盡管查找表位數(shù)相同,Agilex FPGA 中使用的 8 輸入 ALM 能夠以更少的實例實現(xiàn)更多的邏輯。

這表明,6 輸入結(jié)構(gòu)浪費(fèi)了更多的位數(shù),因此需要更多的實例才能實現(xiàn)相同的功能。這些額外的實例將在芯片上占用更多面積,并在系統(tǒng)中增加功耗,這是您在為新設(shè)計選擇 FPGA 時需要考慮的因素。Agilex ALM 還可支持特定的 7 輸入和 8 輸入功能,在 6 輸入 LUT 配置中則需要兩層邏輯來實現(xiàn)這種功能,這不但會消耗額外的 LUT,還會造成嚴(yán)重的時序損失。

FPGA 設(shè)備非常復(fù)雜,針對您的應(yīng)用找到合適的設(shè)備并非易事。邏輯單元和系統(tǒng)邏輯單元等指標(biāo)非常有參考價值,但也需要考慮設(shè)備附帶的其他功能和工具,以及所采用的邏輯結(jié)構(gòu)的底層架構(gòu)。

ALM 是 Agilex FPGA 的基本構(gòu)建模塊,旨在以更少的資源實現(xiàn)更多的功能,從而實現(xiàn)更好的系統(tǒng)優(yōu)化。本文提供了一些其他資源的鏈接,以便您參考。此后,如您需尋找合適的 FPGA,請務(wù)必查看 CoreScore。

-

FPGA

+關(guān)注

關(guān)注

1644文章

21993瀏覽量

615439 -

英特爾

+關(guān)注

關(guān)注

61文章

10183瀏覽量

174167 -

復(fù)用器

+關(guān)注

關(guān)注

1文章

753瀏覽量

28900 -

LUT

+關(guān)注

關(guān)注

0文章

50瀏覽量

12792

原文標(biāo)題:解密邏輯單元與 CoreScore 得分的關(guān)系

文章出處:【微信號:英特爾FPGA,微信公眾號:英特爾FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Cyclone IV 器件的邏輯單元和邏輯陣列模塊

如何在LUT和邏輯元件之間以及邏輯元件和邏輯單元之間進(jìn)行交換

請問“邏輯單元”的意思是什么?

是否可以使用邏輯單元的verilog代碼?

數(shù)字邏輯功能單元

集成算術(shù)/邏輯單元舉例

多功能算術(shù)/邏輯運(yùn)算單元(ALU) ,什么是多功能算術(shù)/邏輯

Cyclone_IV器件的邏輯單元

基于單元相鄰關(guān)系的重構(gòu)區(qū)域構(gòu)造方法

可配置邏輯單元(CLC)

詳解邏輯單元的內(nèi)部結(jié)構(gòu)

表達(dá)式與邏輯門之間的關(guān)系

解密邏輯單元與CoreScore得分的關(guān)系

解密邏輯單元與CoreScore得分的關(guān)系

評論