概述

在進行FPGA硬件設計時,引腳分配是非常重要的一個環節,特別是在硬件電路上需要與其他芯片通行的引腳。Xilinx FPGA從上電之后到正常工作整個過程中各個階段引腳的狀態,會對硬件設計、引腳分配產生非常重要的影響。這篇專題就針對FPGA從上電開始 ,配置程序,到正常工作整個過程中所有IO的狀態進行分析。

從時間階段可以分為兩部分,第一階段是從FPGA上電開始直到配置(Configuration)完成之前。第二個階段是配置完成之后,FPGA開始正常工作開始。

從引腳類型上分,可以分為三大類:第一類是普通的IO,其中又分為程序設計中使用到的IO和程序設計中沒有使用的IO(即在ucf或者XDC文件中沒有進行約束的IO);第二類是專用下載配置引腳(Dedicated Pins),這類引腳只用于專用的功能,包括有M[2:0]、TCK、TMS、PROGRAM_B、INIT_B等。第三類為功能復用引腳,這類引腳在使用特定的功能時使用,例如在使用BPI配置模式時,D[00-31]和A[00-28]需要使用。如果使用SYSMON時,I2C_SDA和I2C_SCL需要使用。但在當前沒有使用該功能的情況下,功能復用引腳可以看成普通IO。

FPGA IO的基本結構

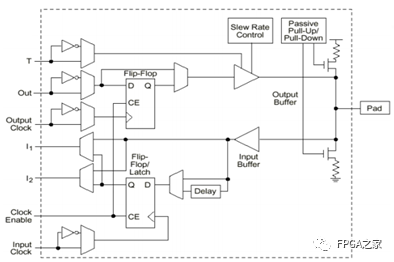

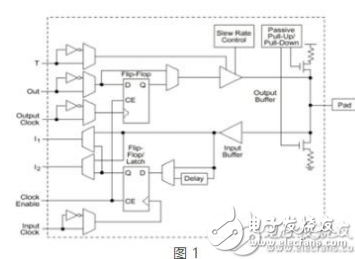

在《IO輸入輸出的各種模式》介紹了處理器IO的各種輸入輸出模式以及原理,那么FPGA的IO是什么樣的結構和原理?圖 1為Xilinx文檔中提供的IOB的內部結構,可以看出:

在FPGA IOB內部,Pad輸出之前,內置上下拉電阻。且可以通過Passive Pull-up/Pull-down模塊控制兩個MOS管的導通與否來控制是否使能上下拉電阻。

內部連接Pad的分別有一個Input Buffer和Output Buffer。其中Input Buffer對外應該始終呈現高阻狀態,同時可以將Pad上的電平通過Input Buffer傳到I1和I2,或者是下部的FF。Output Buffer有兩個控制信號,分別是Slew Rate Control,用來控制輸出信號的Slew Rate;另一個是三態控制信號T,可以控制Output Buffer輸出高阻。

內部輸出信號Out,可以通過上半部分的FF,經Output Clock同步后打出,也可以直接連接到Output buffer的輸入端,直接輸出。

同樣Input Buffer的輸出,可以直接連接到I1和I2,也可以經過下半部分的FF,經過input clock的同步之后輸出到內部總線上。

上下兩個MOS并不是推挽輸出的兩個MOS管,因為并不受到互補信號的控制,并不一定一個導通另一個閉合。

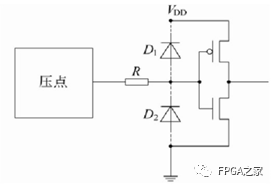

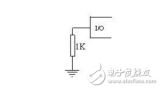

這里介紹一下輸入緩存器的結構和原理,其結構如圖 2所示,其原理與推挽輸出電路非常類似,只是輸入端信號作為了兩個互補MOS管的控制端,控制著輸出端的電平。由于輸入緩沖器有自己的供電電壓,所以輸入電平必須與緩沖器的電源電壓相匹配。D1和D2兩個鉗位二極管用于防治輸入電壓過低或者過高,損壞輸入緩沖器。

普通IO

配置完成之前

在FPGA上電到配置完成之前,由于當前FPGA還沒有下載程序,無法區分哪些引腳被設計所使用,哪些引腳沒有被使用。此時的普通IO包括兩部分:

該封裝中所有的通用IO引腳。

當前所選擇的模式下沒有使用到的所有功能復用管腳。

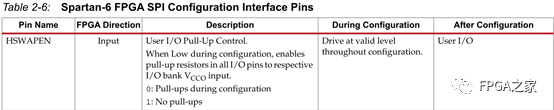

在Spartan6系列以及之前的器件中這些引腳的狀態是根據HSWAPEN的狀態決定的。

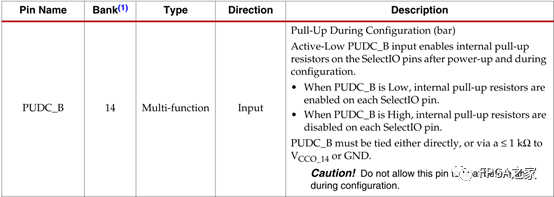

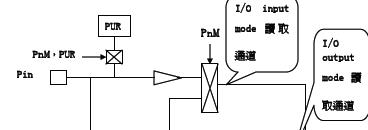

在7系列以后的器件,包括Ultrascale器件中,這些引腳的狀態是根據PUDC_B(Pull-Up During Configuration)引腳

這兩個引腳的功能是相似的,都是用來控制在Configuration完成之前,所有普通IO的上拉電阻是否使能的。對應到圖 1中,即Output Buffer輸出高阻,Input Buffer對外始終為高阻,此時選擇是否連接上拉電阻。

配置完成之后

在配置完成之后,FPGA就進入正常工作的模式了。在配置完成之后,普通引腳可以分為以下兩種:

工程設計中使用的IO,即在UCF或者XDC中有明確約束的IO。

其余沒有使用,也沒有約束的IO。(稱為Unassigned Pins)

首先,對于第一種情況,由于已經在設計中明確設定了這些引腳的設置,包括方向、電平、驅動能力等等,所以在配置完成之后,這些引腳的狀態已經被設置為了預設的狀態。

對于沒有約束的IO,又復雜一些了。在ISE開發環境下,工程完成Implement之后,在Processà Process properties àConfiguration Options中有"-g UnusedPin Unused IOB Pins"屬性,可以選擇Pull Down、Pull Up或者Floating。默認狀態是Pull-Down。對應到圖 1中,是高阻輸出,導通下拉電阻。另兩個設置就是高阻加上上拉電阻或者只是上下拉電阻均不導通。

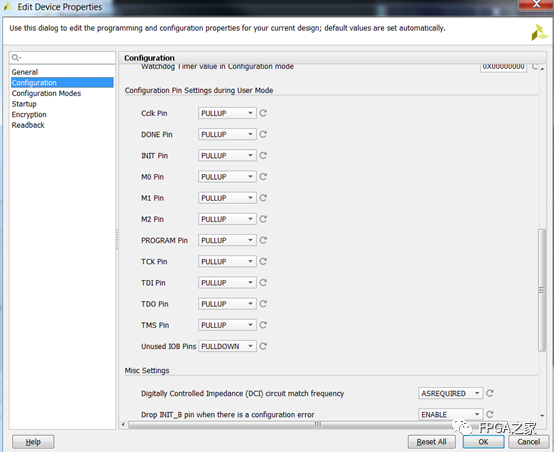

在Vivado中也有相同的設置,必須在實現完成之后,打開Implementation Design之后選擇bitstream Settings,其中在"Configure additional bitstream settings"中的Configuration欄中,有如下屬性選擇項。

專用IO

所有的專用配置引腳全部位于Bank0,包括CFGBVS、M[2:0]、TCK、TMS、TDI、TDO、PRORAM_B、INIT_B、DONE以及CCLK。專用引腳的含義就是無論在配置過程中還是配置完成之后,這些引腳無論在什么階段都只用于配置。

所以對于這些引腳考慮相對比較簡單,分為輸入信號和輸出信號。輸入信號的狀態始終保持LVCMOS電平標準,電壓值為VCCO(輸入信號為什么也有電平標準要求,需要與Input buffer的供電電壓相匹配,見圖 2)。輸出信號的狀態始終保持LVCMOS電平標準,電壓為VCCO,12mA drive,fast slew rate。

功能復用IO

相比于其他引腳,功能復用引腳的情況是最復雜的,這些管腳包括與配置相關的PUDC_B、EMCCLK、CSI_B、CSO_B、DOUT、RDWR_B、D00_MOSI、D01_DIN、D[00-31]、A[00-28]、FCS_B、FOE_B、FEW_B、ADV_B、RS0以及RS1;以及與System Monitor相關的AD0P至AD15P、AD0N至AD15N,I2C_SDA以及I2C_SCLK。

為了說清楚功能復用管腳在不同階段的狀態,將復用管腳分為以下幾類:

在當前所選擇的功能中使用到的功能復用管腳,例如在選擇BPI配置時的D[00-31]和A[00-28]。

在當前所選擇的功能中沒有使用到的功能復用管腳。例如在選擇SPI配置時的D[00-31]和A[00-28]。

在完成配置之前需要作為輸出或者雙向,總之有可能向外輸出信號的管腳,例如I2C_SDA和I2C_SCLK。

配置完成之前

在FPGA上電至配置完成之前的這段時間內,前面列出的第一類引腳,即在當前所選擇的功能中使用到的功能復用管腳,狀態等同于專用配置IO管腳。輸入信號的狀態始終保持LVCMOS電平標準,電壓值為VCCO。輸出信號的狀態始終保持LVCMOS電平標準,電壓為VCCO,12mA drive,fast slew rate。

前面列出的第二類引腳,即在當前所選擇的功能中沒有使用到的功能復用管腳,視同于普通IO,其狀態受到HSWAPEN或者PUDC_B信號的控制,決定是高阻還是連接弱上拉電阻。

第三類引腳的情況比較復雜,目前所知的只有I2C_SDA和I2C_SCLK,這兩個信號會在配置完成前出現一些不確定的狀態。所以如果FPGA的IO還有富余,并且要求所有連接到外部的引腳有確定的狀態,那么最好不要使用這兩個引腳作為連接外設的IO。

配置完成之后

在FPGA配置完成之后,前面提到的三種引腳會被分成另外三類:

第一類是在用戶設計中明確配置了需要保留的功能引腳,例如對于配置相關的引腳設置了Persist option屬性,這種情況下這些引腳會繼續保持之前與配置相關的功能,其狀態為輸入信號的狀態始終保持LVCMOS電平標準,電壓值為VCCO。輸出信號的狀態始終保持LVCMOS電平標準,電壓為VCCO,12mA drive,slow slew rate。再例如設計中使用了SYSMON,I2C_SDA和I2C_SCLK引腳則繼續保持DRP I2C的功能。

第二類是在用戶設計配置中沒有要求保留其特殊功能,這些引腳在配置完成之后會變成普通IO,且在用戶設計中沒有使用到的IO。這些IO相當于Unassigned IO,如前所述,這些IO在配置完成之后的狀態受到相應設置的影響,可以是上拉、下拉或者Floating。

第三類是在用戶設計配置中沒有要求保留其特殊功能,這些引腳在配置完成之后會變成普通IO,并且在用戶設計中使用到的IO。這些IO的狀態由用戶設計控制,會在XDC或者UCF中設定。如果沒有設定就會按照默認的狀態,輸入端口默認狀態為LVCMOS電平標準,電壓值為VCCO;輸出信號默認狀態為保持LVCMOS電平標準,電壓為VCCO,12mA drive,slow slew rate。

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614648 -

Xilinx

+關注

關注

73文章

2183瀏覽量

124475

原文標題:FPGA上電后IO的默認狀態

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

fpga內部主要結構及其功能分析(Kintex-7FPGA內部結構)

stm32沒有配置任何IO口功能的情況下,默認的IO口是什么狀態?

FPGA IO設計

如何拉低我的FPGA的所有io引腳狀態?

請問DSP2812的IO口定義成輸出不指定狀態情況下的默認電平?

FPGA所有IO的狀態進行分析

一文詳解Spartan-6系列IO Tile結構

改變單片機IO口默認電平

FPGA上電后IO的默認狀態

LPC單片機IO口默認狀態、復位狀態、未初始化時輸出高電平處理

FPGA IO的基本結構及默認狀態

FPGA IO的基本結構及默認狀態

評論