晶圓代工龍頭臺(tái)積電針對(duì)先進(jìn)封裝打造的晶圓級(jí)系統(tǒng)整合技術(shù)(WLSI)平臺(tái),透過(guò)導(dǎo)線互連間距密度和系統(tǒng)尺寸上持續(xù)升級(jí),發(fā)展出創(chuàng)新的晶圓級(jí)封裝技術(shù)系統(tǒng)整合芯片(TSMC-SoIC),除了延續(xù)及整合現(xiàn)有整合型扇出(InFO)及基板上晶圓上芯片封裝(CoWoS)技術(shù),提供延續(xù)摩爾定律機(jī)會(huì),并且在系統(tǒng)單芯片(SoC)效能上取得顯著的突破。

臺(tái)積電說(shuō)明,因?yàn)閾碛凶钕冗M(jìn)制程的晶圓或芯片,以及混合匹配的前段3D和后段3D系統(tǒng)整合,客戶可以利用臺(tái)積電獨(dú)特的從晶圓到封裝的整合式服務(wù),來(lái)打造具差異化的產(chǎn)品。

臺(tái)積電打造以3D IC為架構(gòu)的TSMC-SoIC先進(jìn)晶圓級(jí)封裝技術(shù),能將多個(gè)小芯片(Chiplet)整合成一個(gè)面積更小與輪廓更薄的SoC,透過(guò)此項(xiàng)技術(shù),7納米、5納米、甚至3納米的先進(jìn)SoC能夠與多階層、多功能芯片整合,可實(shí)現(xiàn)高速、高頻寬、低功耗、高間距密度、最小占用空間的異質(zhì)3D IC產(chǎn)品。

有別于傳統(tǒng)的封裝技術(shù),TSMC-SoIC是以關(guān)鍵的銅到銅接合結(jié)構(gòu),搭配直通矽晶穿孔(TSV)以實(shí)現(xiàn)最先進(jìn)的3D IC技術(shù)。目前臺(tái)積電已完成TSMC-SoIC制程認(rèn)證,開(kāi)發(fā)出微米級(jí)接合間距(bonding pitch)制程,并獲得極高的電性良率與可靠度數(shù)據(jù),展現(xiàn)了臺(tái)積電已準(zhǔn)備就緒,具備為任何潛在客戶用TSMC -SoIC生產(chǎn)的能力。臺(tái)積電強(qiáng)調(diào),TSMC-SoIC技術(shù)不僅提供延續(xù)摩爾定律的機(jī)會(huì),并且在SoC效能上取得顯著的突破。

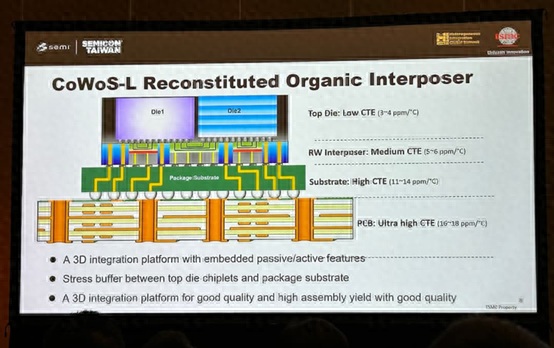

臺(tái)積電持續(xù)加強(qiáng)矽中介層(Si Interposer)與CoWoS布局,以因應(yīng)人工智慧及高效能運(yùn)算市場(chǎng)快速成長(zhǎng)。臺(tái)積電第四代CoWoS技術(shù)已可容納單個(gè)全光罩(full-reticle)尺寸的SoC和多達(dá)6個(gè)3D高頻寬記憶體(HBM)堆疊,第五代CoWoS與博通等客戶合作推出2倍光罩尺寸,并將小芯片、SoIC、HBM3等新芯片結(jié)構(gòu)整合。

臺(tái)積電已完成第五代InFO_PoP(整合型扇出層疊封裝)及第二代InFO_oS(整合型扇出暨基板封裝)技術(shù)并通過(guò)認(rèn)證,支援行動(dòng)應(yīng)用和HPC應(yīng)用。臺(tái)積電亦開(kāi)發(fā)出新世代整合式被動(dòng)元件技術(shù)(IPD),提供高密度電容器和低有效串聯(lián)電感(ESL)以增強(qiáng)電性,并已通過(guò)InFO_PoP認(rèn)證。AI與5G行動(dòng)應(yīng)用將受惠于強(qiáng)化的InFO_PoP技術(shù),新世代IPD預(yù)計(jì)于今年開(kāi)始進(jìn)入大量生產(chǎn)。

5G封裝先出擊

5G智能手機(jī)同步支援Sub-6GHz及mmWave(毫米波)等多頻段,數(shù)據(jù)機(jī)基頻芯片或系統(tǒng)單芯片(SoC)的設(shè)計(jì)及功能更為複雜,晶圓代工龍頭臺(tái)積電除了提供7納米及5納米等先進(jìn)製程晶圓代工,也進(jìn)一步完成5G手機(jī)芯片先進(jìn)封裝供應(yīng)鏈布局。其中,臺(tái)積電針對(duì)數(shù)據(jù)機(jī)基頻芯片推出可整合記憶體的多芯片堆疊(MUlti-STacking,MUST)封裝技術(shù),整合型扇出天線封裝(InFO_AiP)下半年將採(cǎi)用。

由于5G同步支援多頻段、高速資料傳輸速率、大容量資料上下載等特性,加上5G終端裝置亦加入了邊緣運(yùn)算功能,所以5G智能手機(jī)搭載的應(yīng)用處理器、數(shù)據(jù)機(jī)或SoC等5G手機(jī)芯片,都需要導(dǎo)入7納米或5納米等先進(jìn)製程,才能在提升運(yùn)算效能的同時(shí)也能有效降低芯片功耗。因此,包括蘋(píng)果、高通、聯(lián)發(fā)科等都已採(cǎi)用臺(tái)積電7納米或5納米量產(chǎn)。

但在5G芯片運(yùn)算效能大躍進(jìn)的同時(shí),核心邏輯芯片需要更大容量及更高頻寬的記憶體支援,射頻前端模組(RF FEM)也需要搭載更多功率放大器(PA)或低噪放大器(LNA)元件,可以解決芯片整合問(wèn)題的先進(jìn)封裝技術(shù)因此成為市場(chǎng)顯學(xué)。

包括蘋(píng)果、三星等一線大廠今年所打造的5G智能手機(jī),均大量導(dǎo)入系統(tǒng)級(jí)封裝(SiP)設(shè)計(jì)來(lái)降低功耗及達(dá)到輕薄短小目標(biāo),臺(tái)積電因此推出5G智能手機(jī)內(nèi)建芯片的先進(jìn)封裝技術(shù),以期在爭(zhēng)取晶圓代工訂單之際,也能透過(guò)搭載先進(jìn)封裝製程而提高客戶訂單的黏著度。

針對(duì)5G手機(jī)中的應(yīng)用處理器,臺(tái)積電已推出InFO_PoP製程并將處理器及Mobile DRAM封裝成單一芯片。而5G數(shù)據(jù)機(jī)基頻芯片因?yàn)橘Y料傳輸量大增,臺(tái)積電開(kāi)發(fā)出採(cǎi)用InFO製程的多芯片堆疊MUST封裝技術(shù),同樣能將基頻芯片及記憶體整合封裝成單一芯片,而臺(tái)積電也由此開(kāi)發(fā)出3D MiM(MUST in MUST)的多芯片堆疊封裝技術(shù),除了能應(yīng)用在超高資料量傳輸?shù)幕l芯片,亦能應(yīng)用在高效能運(yùn)算(HPC)相關(guān)芯片封裝,將單顆SoC與16顆記憶體整合堆疊在同一芯片。

再者,臺(tái)積電InFO製程可提供射頻元件或射頻收發(fā)器的晶圓級(jí)封裝,但在mmWave所採(cǎi)用的RF FEM模組封裝技術(shù)上,臺(tái)積電推出基于InFO製程的InFO_AiP天線封裝技術(shù),相較于覆晶AiP封裝可明顯縮小芯片尺寸及減少厚度。蘋(píng)果iPhone 12搭載天線雖然沒(méi)有採(cǎi)用臺(tái)積電InFO_AiP製程,但華為海思有機(jī)會(huì)在下半年出首款採(cǎi)用臺(tái)積電InFO_AiP技術(shù)的天線模組并搭載在新一代5G旗艦手機(jī)中。

-

臺(tái)積電

+關(guān)注

關(guān)注

44文章

5741瀏覽量

169059 -

晶圓

+關(guān)注

關(guān)注

52文章

5129瀏覽量

129238 -

芯片封裝

+關(guān)注

關(guān)注

11文章

574瀏覽量

31286

原文標(biāo)題:臺(tái)積電最新封裝技術(shù)升級(jí)進(jìn)展

文章出處:【微信號(hào):mwrfnet,微信公眾號(hào):微波射頻網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

臺(tái)積電進(jìn)入“晶圓代工2.0”,市場(chǎng)規(guī)模翻倍,押注先進(jìn)封測(cè)技術(shù)

ArkUI-X平臺(tái)差異化

臺(tái)積電先進(jìn)制程漲價(jià),最高或達(dá)30%!

EM儲(chǔ)能網(wǎng)關(guān) ZWS智慧儲(chǔ)能云應(yīng)用(8) — 電站差異化支持

愛(ài)立信借助差異化連接提升5G網(wǎng)絡(luò)體驗(yàn)

消息稱臺(tái)積電完成CPO與先進(jìn)封裝技術(shù)整合,預(yù)計(jì)明年有望送樣

易飛揚(yáng)走過(guò)2024——避開(kāi)紅海 專注差異化

西門(mén)子擴(kuò)大與臺(tái)積電合作推動(dòng)IC和系統(tǒng)設(shè)計(jì)

快速整數(shù)除法C2000產(chǎn)品系列的差異化產(chǎn)品

臺(tái)積電封裝,新規(guī)劃

消息稱臺(tái)積電有望9月啟動(dòng)2nm MPW服務(wù)

「騰訊IoT Video+微信小程序」覓感貓眼方案助力鎖廠打造差異化產(chǎn)品優(yōu)勢(shì)

利用臺(tái)積電獨(dú)特的從晶圓到封裝的整合式服務(wù),來(lái)打造具差異化的產(chǎn)品

利用臺(tái)積電獨(dú)特的從晶圓到封裝的整合式服務(wù),來(lái)打造具差異化的產(chǎn)品

評(píng)論