模數(shù)轉(zhuǎn)換器(ADC),是現(xiàn)實(shí)世界模擬信號(hào)與能被MCU處理與存儲(chǔ)的數(shù)字信號(hào)之間的橋梁,是電子技術(shù)發(fā)展的不可或缺的組成部分,在不同的環(huán)境下需使用不同的結(jié)構(gòu)類型的ADC,以使功耗、速率、分辨率、芯片面積等實(shí)現(xiàn)最優(yōu)化。表1對(duì)比了幾種常見(jiàn)結(jié)構(gòu)ADC的速度、分辨率和功耗情況以及各自的應(yīng)用領(lǐng)域。

其中,流水線型模數(shù)轉(zhuǎn)換器能在較低的功耗和較小的面積下實(shí)現(xiàn)較高的速度、較高分辨精度,同時(shí)便于系統(tǒng)集成。流水線模數(shù)轉(zhuǎn)換器的轉(zhuǎn)換速率可以達(dá)到200MSPs以上,分辨率可以達(dá)到14bit,在視頻領(lǐng)域應(yīng)用非常廣泛。

什么是流水線ADC?

流水線ADC,英文釋義為pipeline ADC,就是利用流水線信號(hào)處理的思路發(fā)展起來(lái)的,流水線是快速大量處理某項(xiàng)任務(wù)的一種方法,當(dāng)采用流水線的概念流程完成一項(xiàng)任務(wù)時(shí),該任務(wù)被分成若干個(gè)步驟,每一步驟需要大約相等的時(shí)間來(lái)執(zhí)行,每一步需要一個(gè)執(zhí)行器來(lái)完成。這若干個(gè)步驟組成一個(gè)隊(duì)列,對(duì)于每一個(gè)要生產(chǎn)的產(chǎn)品或者要處理的采樣數(shù)據(jù),這些步驟都要按順序來(lái)執(zhí)行。當(dāng)執(zhí)行器1完成了步驟1后,它把產(chǎn)品或者采樣數(shù)據(jù)送到流水線中的執(zhí)行器2來(lái)進(jìn)行步驟2,此時(shí)執(zhí)行器1開始對(duì)下一個(gè)產(chǎn)品或者采樣數(shù)據(jù)執(zhí)行步驟1;這樣各個(gè)不同的處理步驟可以同時(shí)進(jìn)行,這在信號(hào)處理系統(tǒng)中,極大地提高了采樣處理的速率。

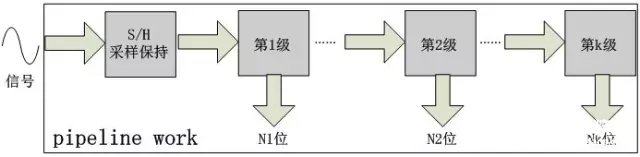

流水線結(jié)構(gòu)ADC的工作示意圖如圖1所示,在流水線ADC中,輸入信號(hào)經(jīng)過(guò)采樣之后,順序地沿著流水線移動(dòng),一步一步地進(jìn)行數(shù)字轉(zhuǎn)換,每一步轉(zhuǎn)換得到一定數(shù)量的數(shù)字輸出位,最高有效位最先得到,最低有效位最后得到。

圖1 流水線結(jié)構(gòu)ADC工作示意圖

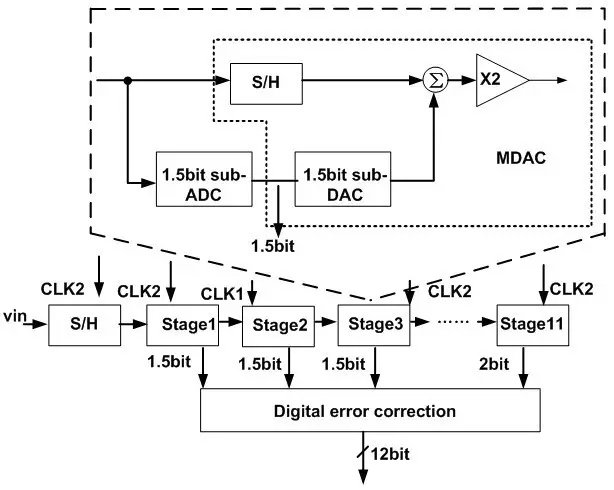

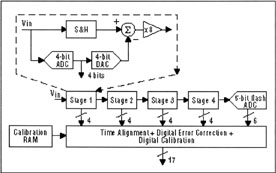

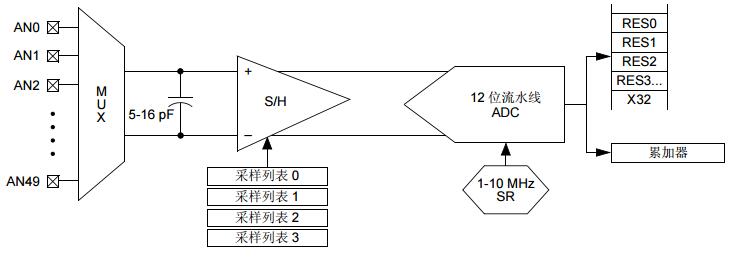

它實(shí)質(zhì)上是一個(gè)多級(jí)幅值量化器,它的數(shù)字化過(guò)程由級(jí)聯(lián)的多個(gè)結(jié)構(gòu)相似的低精度模數(shù)轉(zhuǎn)換器完成。它的主要優(yōu)點(diǎn)在于:第一,流水線結(jié)構(gòu)中各級(jí)處于并行工作狀態(tài),提高了轉(zhuǎn)換速率;第二,與全并行結(jié)構(gòu)ADC相比極大地節(jié)約了芯片面積并降低了功耗,例如一個(gè)N-bit的并行結(jié)構(gòu)的ADC,需2的N次方減1個(gè)比較器,若為10bit的全并行ADC,則需要高達(dá)1023個(gè)比較器,而以1.5bit每級(jí)的流水線結(jié)構(gòu)為例,僅需21個(gè)比較器,一種1.5bit每級(jí)的12bit高速pipeline ADC的結(jié)構(gòu)如圖2所示。

圖2 12bit高速流水線ADC原理圖

-

adc

+關(guān)注

關(guān)注

99文章

6533瀏覽量

545759 -

流水線結(jié)構(gòu)

+關(guān)注

關(guān)注

0文章

4瀏覽量

7609

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

流水線ADC結(jié)構(gòu)解析 流水線ADC和其它ADC的比較

如何設(shè)計(jì)一種適用于流水線ADC的運(yùn)算放大器?

流水線ADC

流水線ADC的行為級(jí)仿真

基于VHDL_AMS的流水線ADC結(jié)構(gòu)式建模方法與仿真

一種改進(jìn)運(yùn)放共享結(jié)構(gòu)的11位流水線ADC設(shè)計(jì)

各種流水線特點(diǎn)及常見(jiàn)流水線設(shè)計(jì)方式

了解流水線型ADC

什么是流水線 Jenkins的流水線詳解

流水線ADC的內(nèi)部結(jié)構(gòu)和工作原理是什么

什么是流水線ADC_流水線結(jié)構(gòu)ADC工作原理圖

什么是流水線ADC_流水線結(jié)構(gòu)ADC工作原理圖

評(píng)論