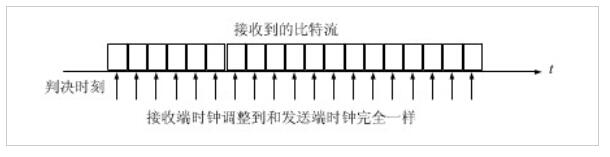

在數據通訊中最根柢的同步辦法即是“位同步”(bit synchronization)或比特同步。比特是數據傳輸的最小單位。位同步(比特同步)是指接納端時鐘現已調整到和發送端時鐘徹底相同,因而接納端收到比特流后,就能夠在每一位的根柢方位進行斷定(如下圖所示)。位同步(比特同步)的意圖是為了將發送端發送的每一個比特都準確地接納下來。這就要在準確的時刻(通常即是在每一位的根柢方位)對收到的電平依據事前已約好好的規矩進行斷定。例如,電平若跨過必定數值則為1,不然為0。

但只是有位同步還不行。由于數據要以幀為單位進行發送。若某一個幀有過錯,往后就重傳這個犯錯的幀。因而一個幀應當有了解的間隔,也即是說,要有幀定界符。接納端在收到比特流后,有必要能夠準確地找出幀定界符,以便知道哪些比特構成一個幀。接納端找到了幀定界符并斷定幀的準確方位,即是結束了“幀同步”(frame synchronization)。

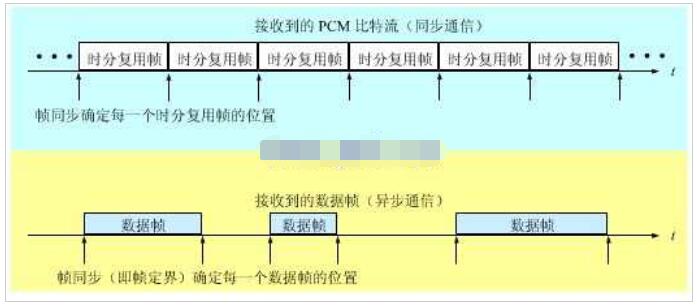

在運用PCM的時分復用通訊中(這種通訊都選用同步通訊辦法),接納端只是能夠準確接納比特流是不行的。接納端還有必要準確地將一個個時分復用幀差異出來。因而要運用分外的時隙(包富含一些分外的比特組合),使接納端能夠把每一個時分復用幀的方位斷定出來。這也叫做幀同步。下圖給出了這兩種紛歧樣的幀同步的暗示圖。

圖中上面有些的同步通訊辦法在電信網中運用得十分廣泛,其間的一個首要特征是在發送端接連不斷地發送比特流中,即便有的時隙沒有被用戶運用,但用于同步的時隙也要保留在時分復用幀中的相應方位上。在同步通訊中幀同步的使命即是使接納端能夠從收到的接連比特流接連定出每一個時分復用幀的方位。

圖中下面有些的異步通訊辦法在核算機網絡中運用得較多。咱們能夠留神到,數據幀在接納端呈現的時刻是不規矩的。因而在接納端有必要進行幀定界。但幀定界也常稱為幀同步。因而,當咱們看到“幀同步”時,應當澄清這是同步通訊中的幀同步,仍是異步通訊中的幀定界。

這兒咱們要偏重一下,在異步通訊時,接納端即便找到了數據幀的開端處,也還有必要將數據幀中的悉數比特逐一接納下來。因而,接納端有必要和數據幀中的各個比特進行比特同步(這即是異步通訊中的同步疑問)。試想:假定接納端不知道每一個比特要繼續多長時刻,那怎么能將一個個比特接納下來呢?因而,不管是同步通訊仍是異步通訊,要想接納比特塊中的每一個比特,就有必要和比特塊中的比特進行位同步(比特同步)。可是在異步通訊中,位同步(比特同步)的辦法和同步通訊時并不徹底相同。

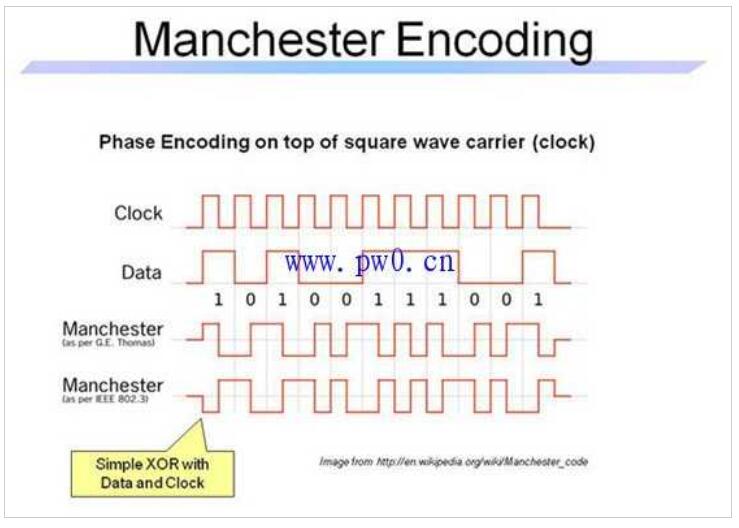

在同步通訊中,最準確的同步辦法是使全網時鐘準確同步。全網的主時鐘的長時刻精度央求抵達 ± 1.0 ? 1011,因而有必要選用原子鐘(例如,銫原子鐘),但這么的同步網絡的報價很高(如SDH/SONET網絡)。實習上,在同步通訊中,也能夠選用比照經濟的辦法結束同步。這種辦法即是在接納端設法從收到的比特流中將位同步的時鐘信息獲取出來(發送端在發送比特流時,發送時鐘的信息就現已在所發送的比特流傍邊了)。這種同步辦法常稱為準同步(plesiochronous)。在教材中的圖3-16中介紹的曼徹斯特編碼就能夠使接納端很便本地從收到的比特流中將時鐘信息獲取出來,這么就能夠很簡略地結束位同步。在以幀為傳送單位的異步通訊中,接納端通常也是選用從收到的比特流中獲取時鐘信息的辦法來結束位同步。

在以字符為單位的異步通訊中,由于每一個字符只需8個比特,因而只需收發兩頭的時鐘頻率相差不太大,在開端位的觸發下,這8個比特的位同步很簡略做到,因而不需求選用別的辦法來結束位同步(但不等于說能夠不要位同步)。

何為曼徹斯特編碼?

自同步法是指能從數據信號波形中獲取同步信號的辦法。典型比便當是出名的曼徹斯特編碼,常用于局域網傳輸。在曼徹斯特編碼中,每一位的基地有一跳變,位基地的跳變既作時鐘信號,又作數據信號;從高到低跳變標明“1”,從低到高跳變標明“0”。還有一種是差分曼徹斯特編碼,每位基地的跳變僅供應時鐘守時,而用每位開端時有無跳變標明“0”或“1”,有跳變為“0”,無跳變為“1”。

兩種曼徹斯特編碼是將時鐘和數據包括在數據流中,在傳輸代碼信息的一同,也將時鐘同步信號一同傳輸到對方,每位編碼中有一跳變,不存在直流重量,因而具有自同步才諧和超卓的抗煩擾功用。但每一個碼元都被調成兩個電平,所以數據傳輸速率只需調制速率的1/2。

即是說首要用在數據同步傳輸的一種編碼辦法

-

幀同步

+關注

關注

0文章

13瀏覽量

9420 -

位同步

+關注

關注

0文章

8瀏覽量

7702

發布評論請先 登錄

相關推薦

【CAN總線知識】CAN總線信號傳輸的位定時與位同步理論

基于FPGA的快速位同步系統設計

位同步,位同步是什么意思

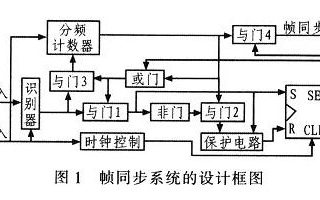

采用FPGA實現同步、幀同步系統的設計

基于DSP Builder的幀同步檢出模型

位同步是什么_位同步和幀同步有什么區別

位同步是什么_位同步和幀同步有什么區別

評論