?在前面的章節中,我們用了很多Tcl的指令,但有些指令并沒有把所有的參數多列出來解釋,這一節,我們就把約束中的Tcl指令詳細講一下。

我們前面講到過get_pins和get_ports的區別,而且我們也用過get_cells、get_clocks和get_nets這幾個指令,下面就通過一張圖直觀展現它們的區別。

get_clocks后面的對象是我們之前通過create_clocks或者create_generated_clocks創建的時鐘,不在硬件上直接映射。

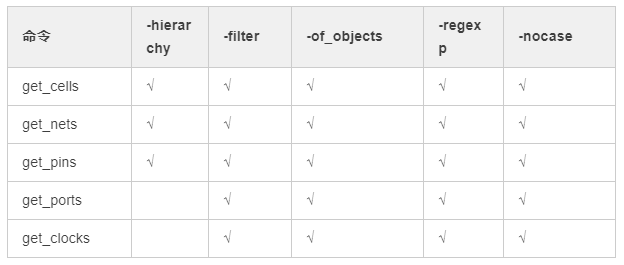

我們再來看下各個命令的屬性。

1. port

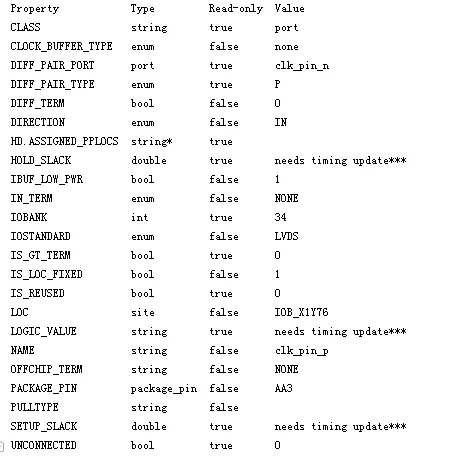

我們可以通過Tcl腳本查看port的所有屬性,比如上面的wave_gen工程中,有一個port是clk_pin_p,采用如下腳本:

set inst [get_ports clk_pin_p] report_property $inst

顯示如下:

get_ports的使用方法如下:

# 獲取所有端口 get_ports * # 獲取名稱中包含data的端口 get_ports *data* # 獲取所有輸出端口 get_ports -filter {DIRECTION == OUT} # 獲取所有輸入端口 all_inputs # 獲取輸入端口中名字包含data的端口 get_ports -filter {DIRECTION == IN} *data* # 獲取總線端口 get_ports -filter {BUS_NAME != ""}

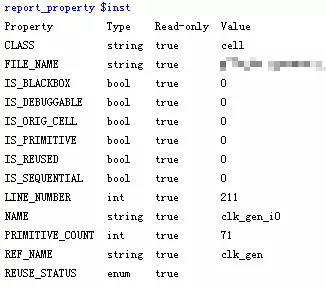

2. cell

按照上面的同樣的方式,獲取cell的property,如下:

get_cells的使用方法如下:

# 獲取頂層模塊

get_cells *

# 獲取名稱中包含字符gen的模塊

get_cells *gen*

# 獲取clk_gen_i0下的所有模塊

get_cells clk_gen_i0/*

# 獲取觸發器為FDRE類型且名稱中包含字符samp

get_cells -hier filter {REF_NAME == FDRE} *samp*

# 獲取所有的時序單元邏輯

get_cells -hier -filter {IS_SEQUENTIAL == 1}

# 獲取模塊uart_rx_i0下兩層的LUT3

get_cells -filter {REF_NAME == LUT3} *uart_tx_i0/*/*

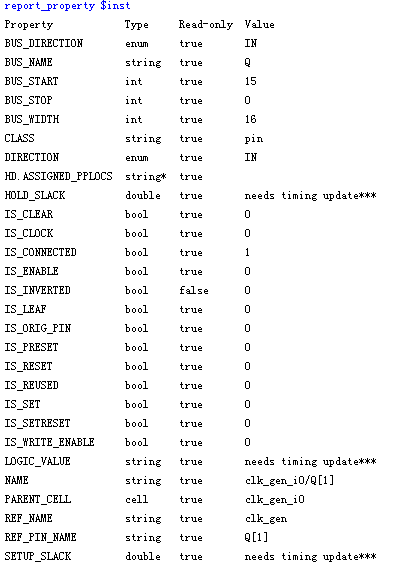

3. pin

獲取pin的property,如下:

get_pins的使用方法如下:

# 獲取所有pins get_pins * # 獲取名稱中包含字符led的引腳 get_pins -hier -filter {NAME =~ *led*} # 獲取REF_PIN_NAME為led的引腳 get_pins -hier -filter {REF_PIN_NAME == led} # 獲取時鐘引腳 get_pins -hier -filter {IS_CLOCK == 1} # 獲取名稱中包含cmd_parse_i0的使能引腳 get_pins -filter {IS_ENABLE == 1} cmd_parse_i0/*/* # 獲取名稱中包含字符cmd_parse_i0且為輸入的引腳 get_pins -filter {DIRECTION == IN} cmd_parse_i0/*/*

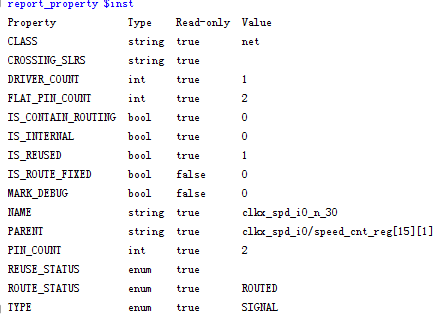

4. net

獲取pin的property,如下:

get_nets的使用方法如下:

# 獲取所有nets

get_nets *

# 獲取名稱中包含字符send_resp_val的網線

get_nets -hier *send_resp_val*

get_nets -filter {NAME =~ *send_resp_val*} -hier

# 獲取穿過邊界的同一網線的所有部分

get_nets {resp_gen_i0/data4[0]} -segments

# 獲取模塊cmd_parse_i0下的所有網線

get_nets -filter {PARENT_CELL == cmd_parse_i0} -hier

# 獲取模塊cmd_parse_i0下的名稱中包含字符arg_cnt[]的網線

get_nets -filter {PARENT_CELL == cmd_parse_i0} -hier *arg_cnt[*]

這5個tcl指令的常用選項如下表:

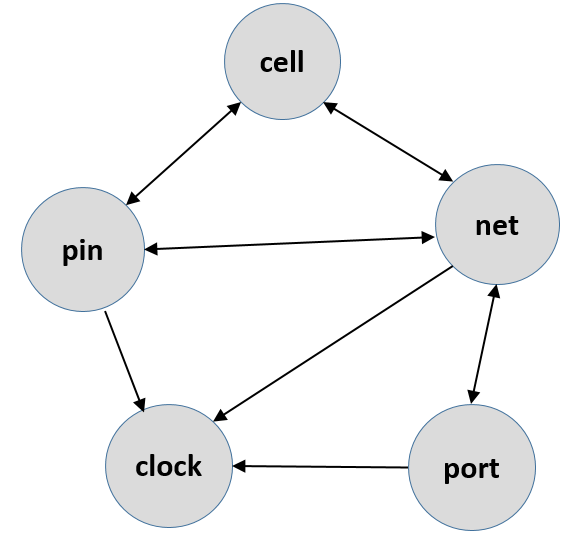

?這5個Tcl命令對應的5個對象之間也有著密切的關系,下圖所示的箭頭的方向表示已知箭頭末端對象可獲取箭頭指向的對象。

以wave_gen中的clk_gen_i0模塊為例來說明上面的操作:

# 獲取模塊的輸入引腳

get_pins -of [get_cells {clk_gen_i0/clk_core_i0}] -filter {DIRECTION == IN}

# 已知引腳名獲取所在模塊

get_cells -of [get_pins clk_gen_i0/clk_core_i0/clk_in1_n]

# 已知模塊名獲取與該模塊相連的網線

get_nets -of [get_cells {clk_gen_i0/clk_core_i0}]

# 已知引腳名獲取與該引腳相連的網線

get_nets -of [get_pins clk_gen_i0/clk_core_i0/clk_rx]

# 已知時鐘引腳獲取時鐘引腳對應的時鐘

get_clocks -of [get_pins clk_gen_i0/clk_core_i0/clk_rx]

需要注意的是:

1. -hier不能和層次分隔符“/”同時使用,但“/”可出現在-filter中

2. 可根據屬性過濾查找目標對象

3. -filter中的屬性為:“==”(相等)、“!=”(不相等)、"=~"(匹配)、"!~"(不匹配),若有多個表達式,其返回值為bool類型時,支持邏輯操作(&& ||)

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614710 -

TCL

+關注

關注

11文章

1775瀏覽量

89666 -

時序約束

+關注

關注

1文章

118瀏覽量

13635

發布評論請先 登錄

電機繞組滾動烘干爐防爆安全技術探討

FPGA時序約束之設置時鐘組

TCL發布萬象分區技術,重塑Mini LED技術巔峰

時序約束一主時鐘與生成時鐘

FPGA約束中的Tcl指令技術探討

FPGA約束中的Tcl指令技術探討

評論