1. 介紹

Vitis是Xilinx新推出的統(tǒng)一軟件平臺(tái),可實(shí)現(xiàn)在 Xilinx 所有芯片(包括 FPGA、SoC 和 Versal ACAP)上開發(fā)嵌入式軟件和加速應(yīng)用。Xilinx主要宣傳Vitis可以為異構(gòu)平臺(tái)的應(yīng)用實(shí)現(xiàn)加速。其實(shí),Vitis也能完美的支持嵌入式軟件開發(fā)。下面以MicroZed單板為例,介紹在Vitis里如何創(chuàng)建嵌入式軟件工程,并且編譯和調(diào)試,直到啟動(dòng)。

2. 測(cè)試環(huán)境

1). Windows 10

2). Vitis 2019.2

3). MicroZed

3. Vivado工程導(dǎo)出XSA文件

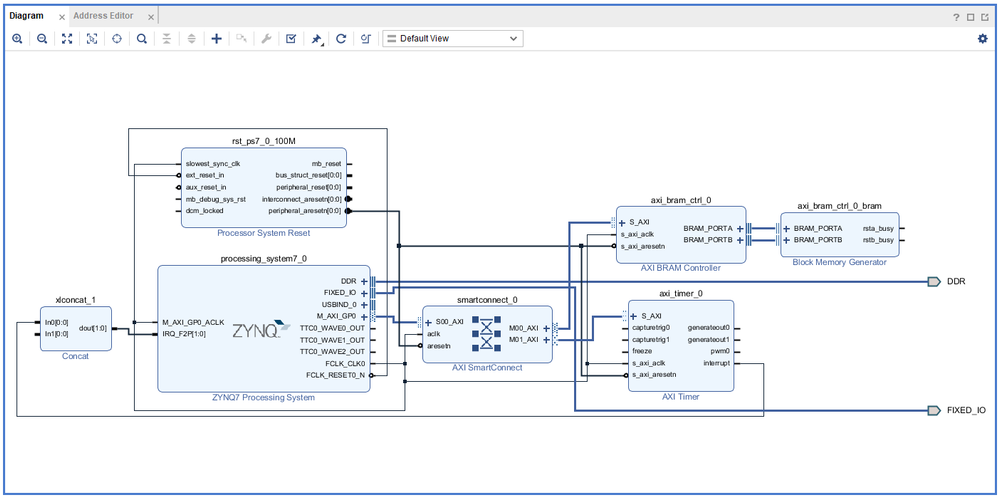

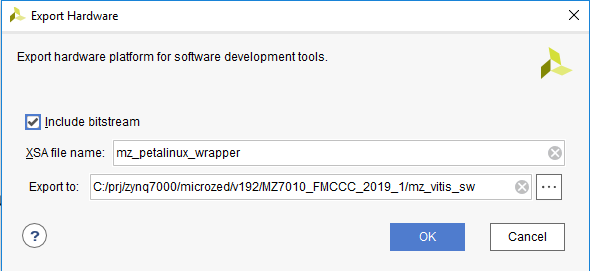

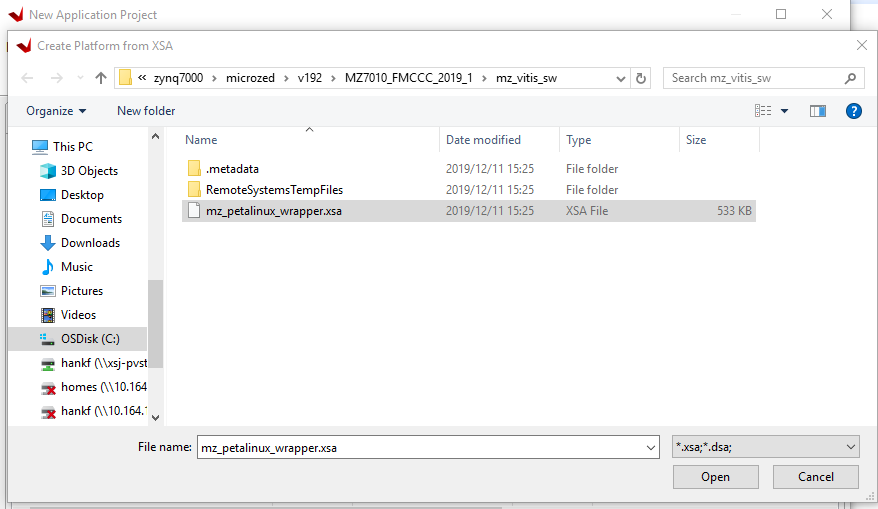

在MicroZed 2019.1 BSP下載MicroZed的Petalinux BSP。解壓后,使用Vivado 2019.2 打開其中的硬件工程,升級(jí)所有IP,然后編譯工程。為了測(cè)試,也可以在BD設(shè)計(jì)中,添加AXI timer,AXI BRAM等IP。成功編譯工程后,導(dǎo)出硬件設(shè)計(jì)文件mz_petalinux_wrapper.xsa。在2019.2使用了新的硬件設(shè)計(jì)文件格式,也就是XSA文件。

3.1. BD設(shè)計(jì)

也可以不添加AXI timer,AXI BRAM等IP。

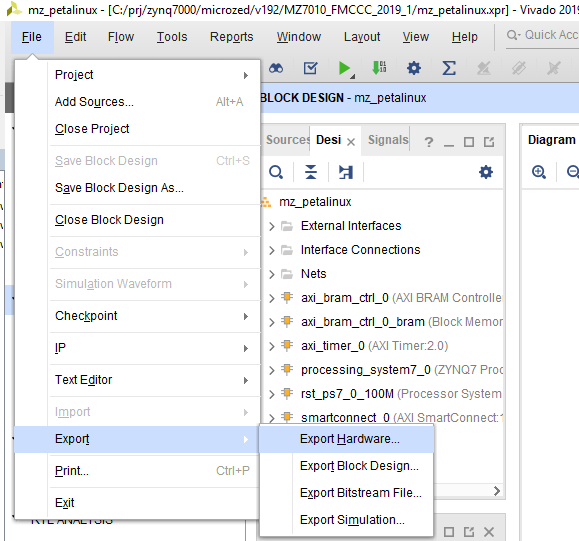

3.2. 導(dǎo)出硬件的菜單

3.3. 導(dǎo)出硬件的界面

請(qǐng)指定XSA文件的路徑和名字。

3.4. Vivado在TCL Console里關(guān)于導(dǎo)出硬件的打印。

write_hw_platform -fixed -force -include_bit -file C:/prj/zynq7000/microzed/v192/MZ7010_FMCCC_2019_1/mz_vitis_sw/mz_petalinux_wrapper.xsa INFO: [Vivado 12-4895] Creating Hardware Platform: C:/prj/zynq7000/microzed/v192/MZ7010_FMCCC_2019_1/mz_vitis_sw/mz_petalinux_wrapper.xsa ... INFO: [Vivado 12-4896] Successfully created Hardware Platform: C:/prj/zynq7000/microzed/v192/MZ7010_FMCCC_2019_1/mz_vitis_sw/mz_petalinux_wrapper.xsa write_hw_platform: Time (s): cpu = 00:00:16 ; elapsed = 00:00:17 . Memory (MB): peak = 1570.996 ; gain = 0.000

4. 創(chuàng)建工程

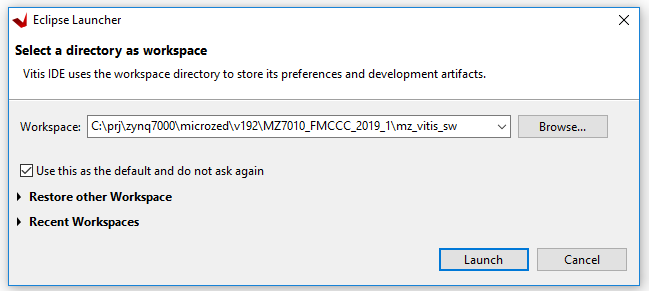

4.1. 指定workspace目錄。

啟動(dòng)Vitis,指定它的workspace目錄。

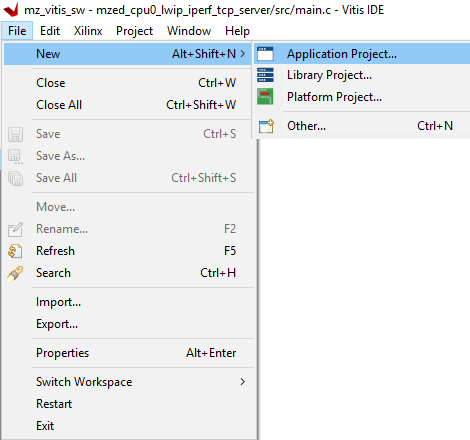

4.2. VitisFile菜單

在Vitis的File菜單里,選擇"New --> Application Project"。

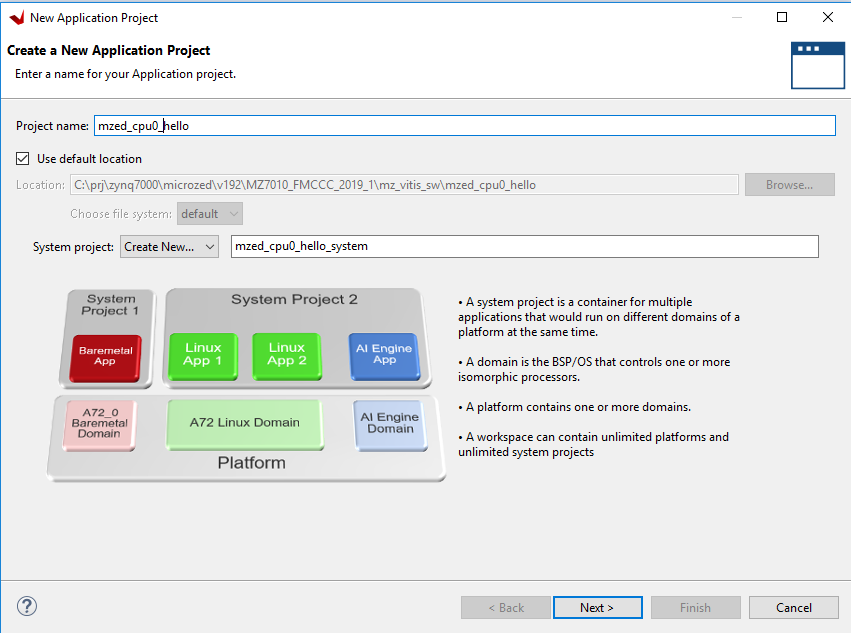

4.3. 指定Application工程名

指定Application的工程名,可以使用默認(rèn)的system工程名。

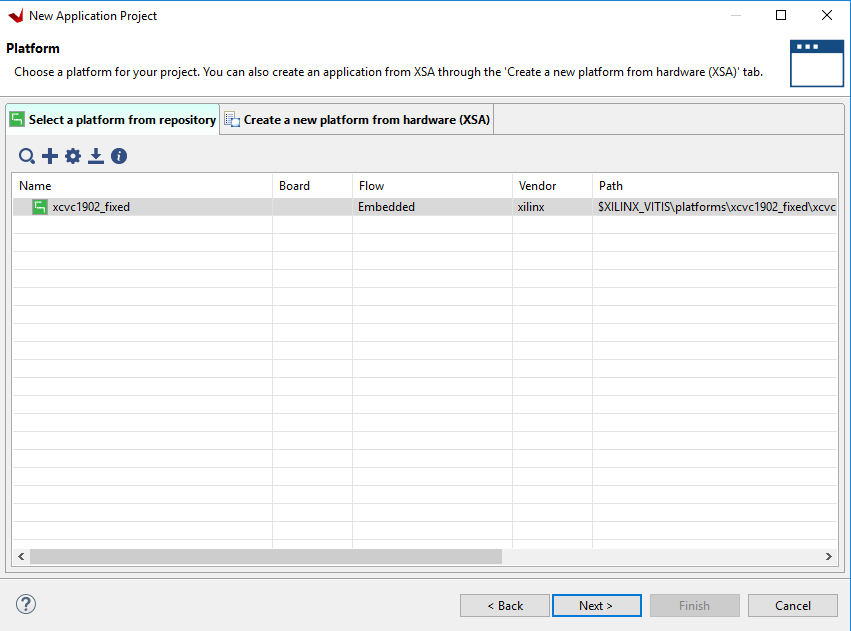

4.4. Platform頁面

點(diǎn)擊Next,進(jìn)入Platform頁面。

4.5. 指定XSA文件

在Platform頁面,選擇右邊的“Creae a new platform from hardware(XSA)”, 在點(diǎn)擊“+”,指定平臺(tái)的XSA文件,然后Vitis自動(dòng)創(chuàng)建platform。

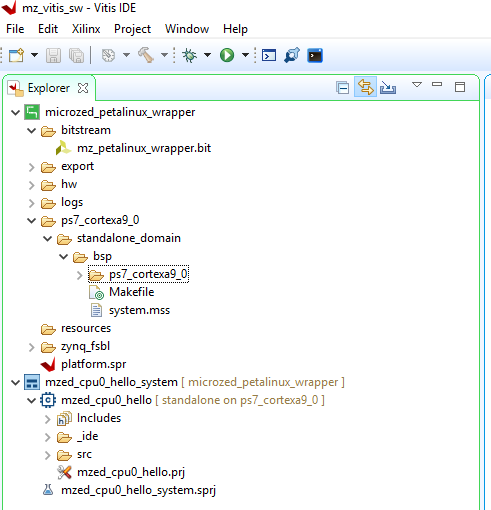

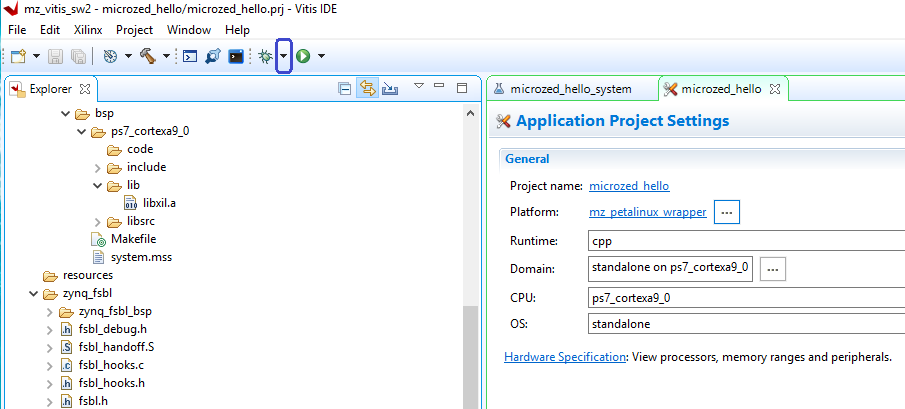

4.7. 創(chuàng)建工程后的目錄結(jié)構(gòu)。

4.8. 執(zhí)行編譯。

創(chuàng)建工程后,執(zhí)行編譯。會(huì)先編譯FSBL工程,BSP工程,再編譯應(yīng)用程序工程。

Project --> Build Project

15:53:30 **** Build of configuration Debug for project mzed_cpu0_hello **** make all C:/Xilinx/Vitis/2019.2/gnuwin/bin/make --no-print-directory pre-build a9-linaro-pre-build-step C:/Xilinx/Vitis/2019.2/gnuwin/bin/make --no-print-directory main-build Building file: ../src/helloworld.c Invoking: ARM v7 gcc compiler arm-none-eabi-gcc -Wall -O0 -g3 -c -fmessage-length=0 -MT"src/helloworld.o" -mcpu=cortex-a9 -mfpu=vfpv3 -mfloat-abi=hard -IC:/prj/zynq7000/microzed/v192/MZ7010_FMCCC_2019_1/mz_vitis_sw/microzed_petalinux_wrapper/export/microzed_petalinux_wrapper/sw/microzed_petalinux_wrapper/standalone_domain/bspinclude/include -MMD -MP -MF"src/helloworld.d" -MT"src/helloworld.o" -o "src/helloworld.o" "../src/helloworld.c" Finished building: ../src/helloworld.c Building file: ../src/platform.c Invoking: ARM v7 gcc compiler arm-none-eabi-gcc -Wall -O0 -g3 -c -fmessage-length=0 -MT"src/platform.o" -mcpu=cortex-a9 -mfpu=vfpv3 -mfloat-abi=hard -IC:/prj/zynq7000/microzed/v192/MZ7010_FMCCC_2019_1/mz_vitis_sw/microzed_petalinux_wrapper/export/microzed_petalinux_wrapper/sw/microzed_petalinux_wrapper/standalone_domain/bspinclude/include -MMD -MP -MF"src/platform.d" -MT"src/platform.o" -o "src/platform.o" "../src/platform.c" Finished building: ../src/platform.c Building target: mzed_cpu0_hello.elf Invoking: ARM v7 gcc linker arm-none-eabi-gcc -mcpu=cortex-a9 -mfpu=vfpv3 -mfloat-abi=hard -Wl,-build-id=none -specs=Xilinx.spec -Wl,-T -Wl,../src/lscript.ld -LC:/prj/zynq7000/microzed/v192/MZ7010_FMCCC_2019_1/mz_vitis_sw/microzed_petalinux_wrapper/export/microzed_petalinux_wrapper/sw/microzed_petalinux_wrapper/standalone_domain/bsplib/lib -o "mzed_cpu0_hello.elf" ./src/helloworld.o ./src/platform.o -Wl,--start-group,-lxil,-lgcc,-lc,--end-group Finished building target: mzed_cpu0_hello.elf Invoking: ARM v7 Print Size arm-none-eabi-size mzed_cpu0_hello.elf |tee "mzed_cpu0_hello.elf.size" text data bss dec hex filename 19064 1144 22568 42776 a718 mzed_cpu0_hello.elf Finished building: mzed_cpu0_hello.elf.size 15:53:43 Build Finished (took 12s.869ms)

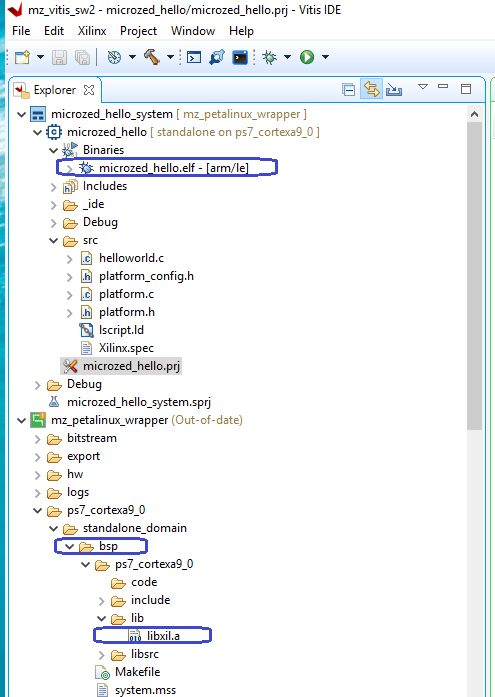

編譯后應(yīng)用程序和Domain目錄結(jié)構(gòu)

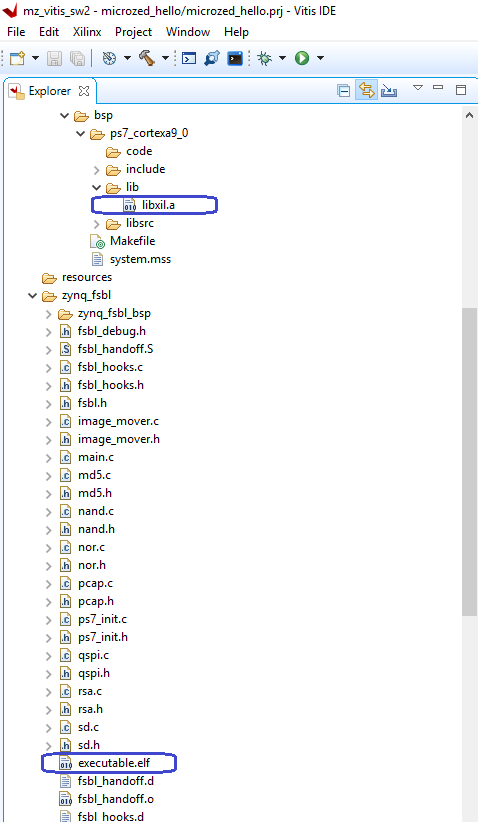

編譯后FSBL目錄結(jié)構(gòu)

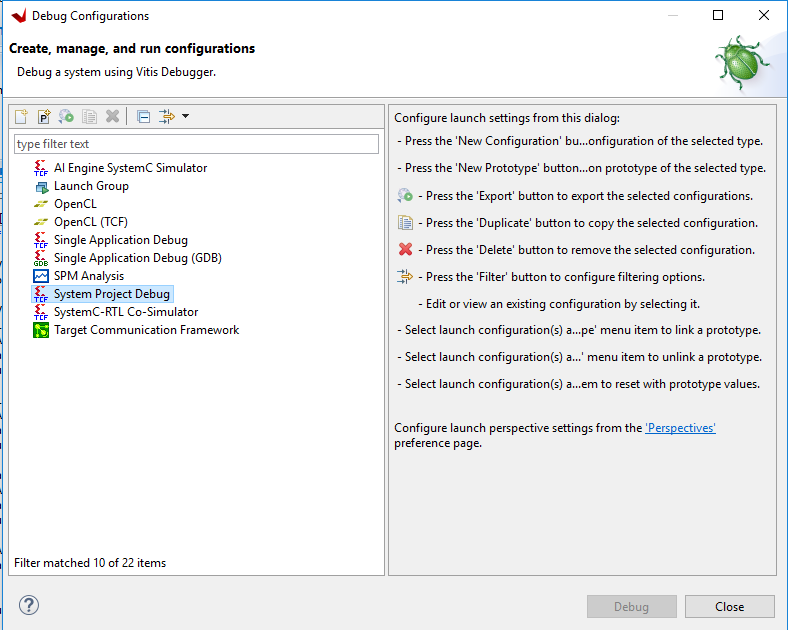

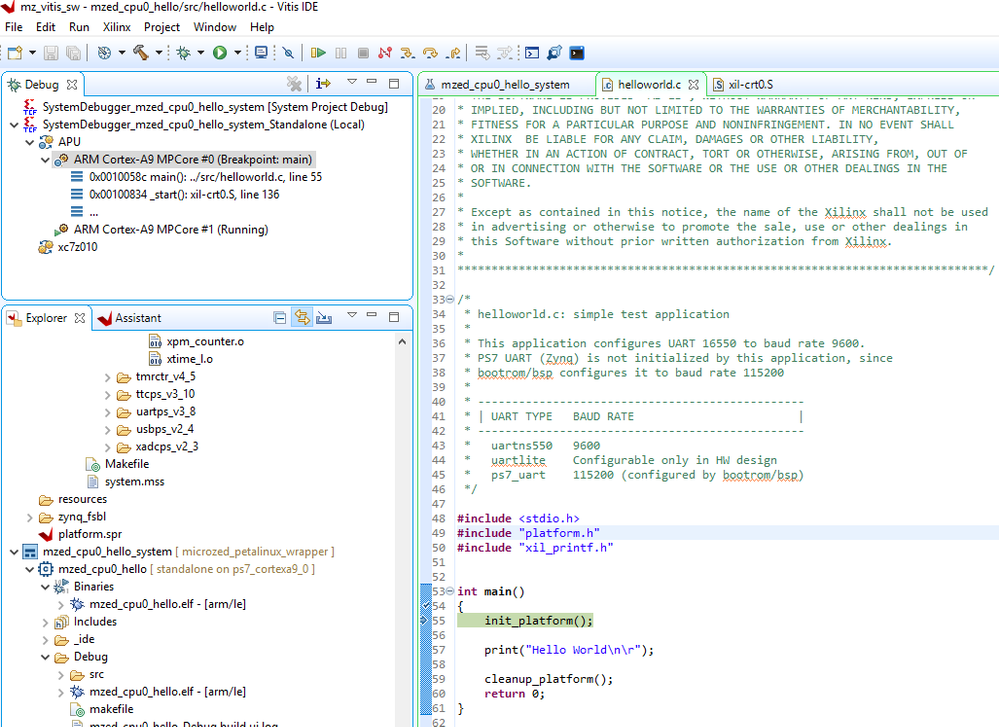

5. 調(diào)試工程 5.1. 調(diào)試配置界面

先點(diǎn)擊想調(diào)試的工程,再點(diǎn)擊工具條調(diào)試圖標(biāo)旁邊的三角形,選擇"Debug Configurations",

得到調(diào)試配置界面。

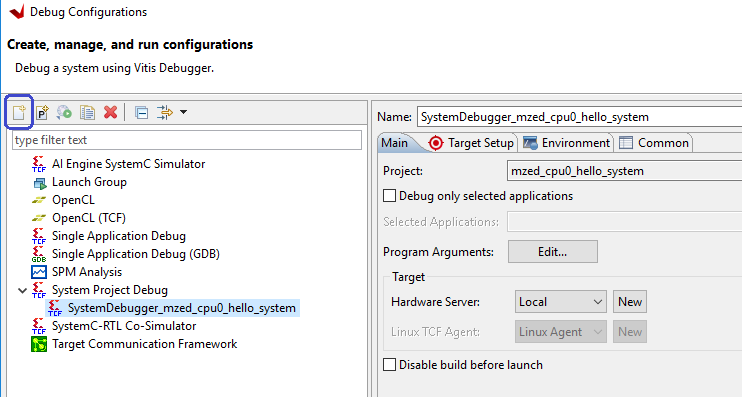

5.2. 自動(dòng)創(chuàng)建調(diào)試配置

雙擊System Project,Vitis自動(dòng)創(chuàng)建了調(diào)試配置。

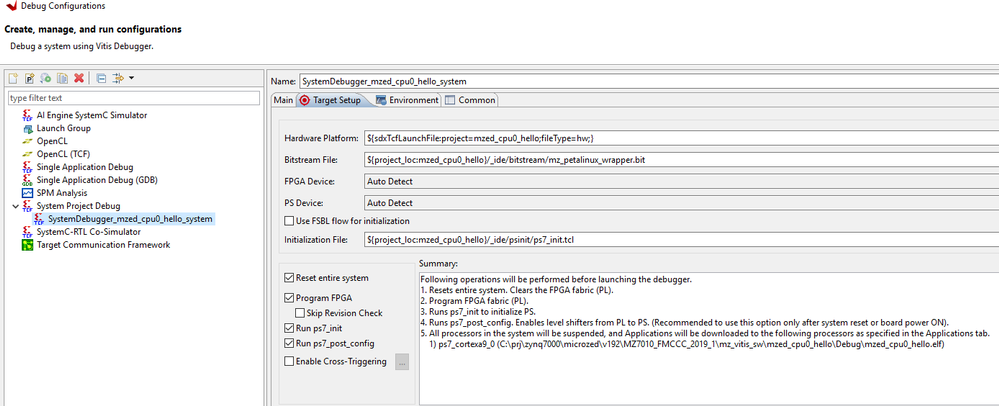

5.3. 檢查調(diào)試配置的Target Setup。

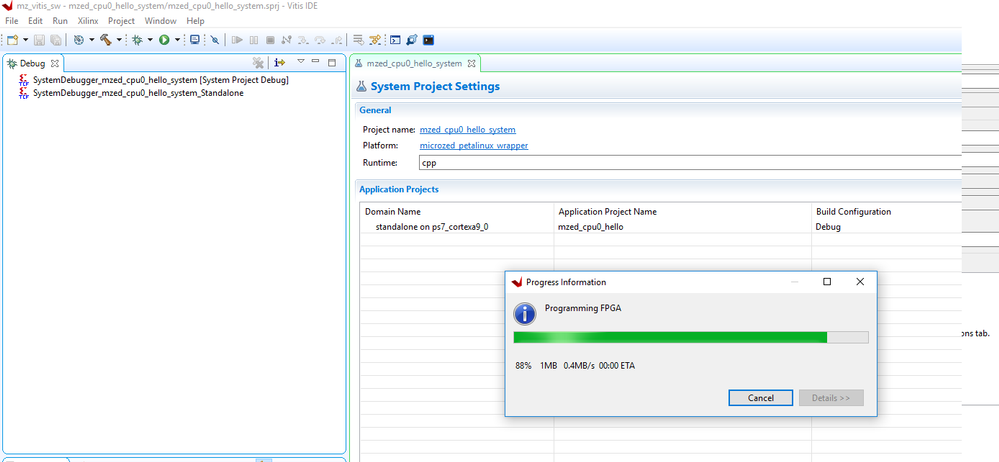

5.4. 開始調(diào)試

點(diǎn)擊Debug后,會(huì)開始調(diào)試。由于有FPGA設(shè)計(jì),先下載FPGA。

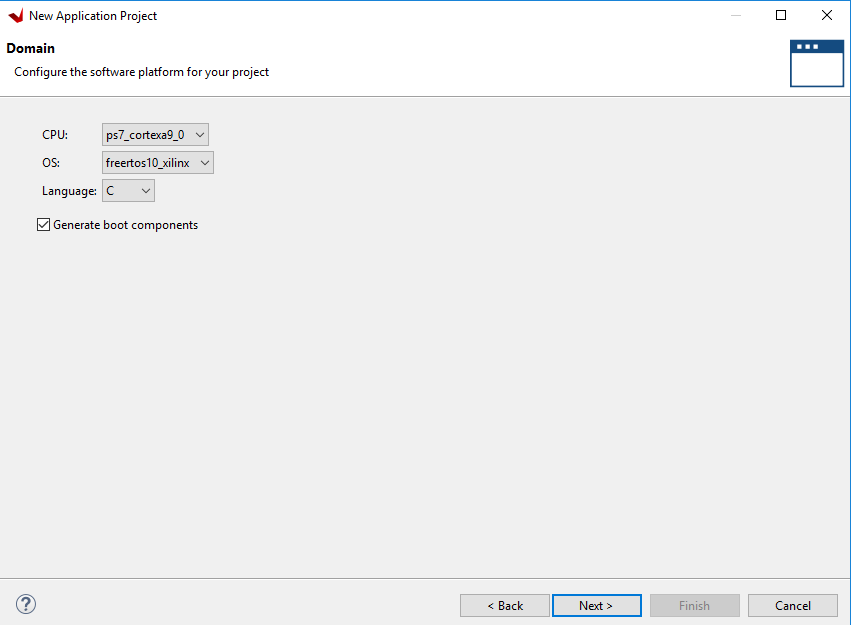

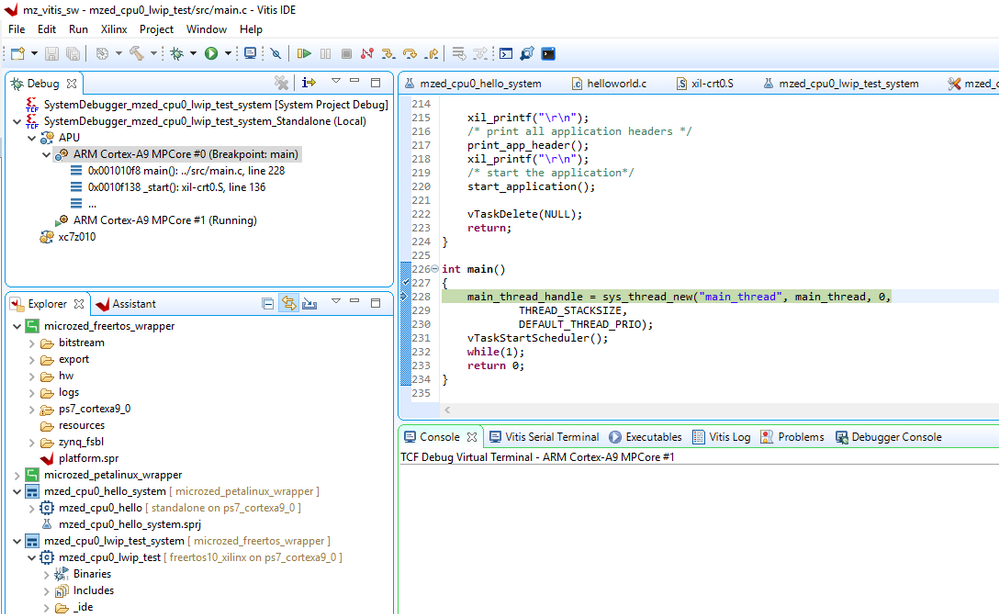

6. 調(diào)試工程 6.1. FreeRTOS

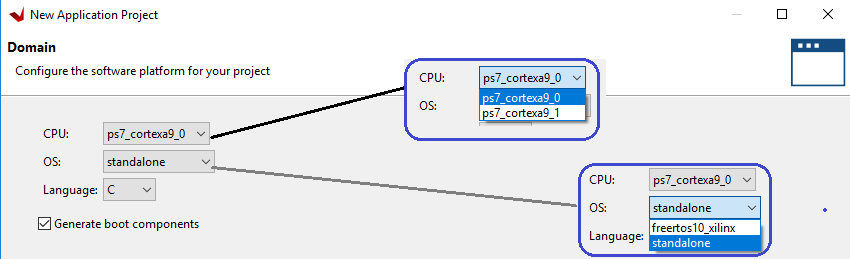

之前只是簡(jiǎn)單的Hello world工程。下面創(chuàng)建更復(fù)雜的FreeRTOS LWIP TCP iPerf server. 在Domain界面,為OS選擇FreeRTOS。

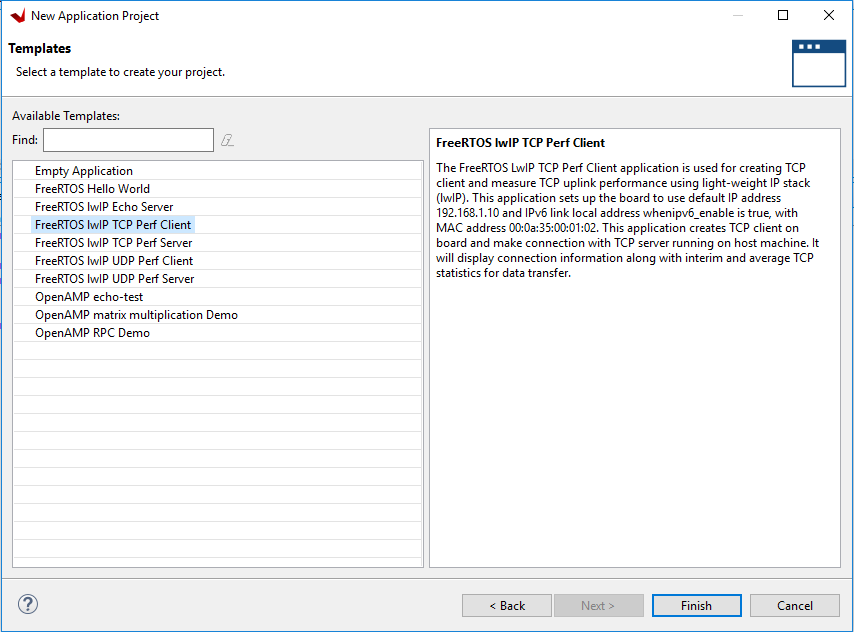

6.2. LWIP TCP iPerf server

在Templates界面,為Template選擇FreeRTOS LWIP TCP Perf server。

6.3. 調(diào)試LWIP TCP iPerf server

同樣的啟動(dòng)調(diào)試,也在main函數(shù)入口處停下,直接選擇連續(xù)運(yùn)行。

6.4. 連續(xù)運(yùn)行

連續(xù)運(yùn)行后,單板串口打印。

-----lwIP Socket Mode TCP Server Application------ Start PHY autonegotiation Waiting for PHY to complete autonegotiation. autonegotiation complete link speed for phy address 0: 100 ERROR: DHCP request timed out Configuring default IP 192.168.1.10 Board IP: 192.168.1.10 Netmask : 255.255.255.0 Gateway : 192.168.1.1 TCP server listening on port 5001 On Host: Run $iperf -c 192.168.1.10 -i 5 -t 300 -w 2M

6.5. 電腦Ping測(cè)試

設(shè)置電腦IP地址,再做Ping測(cè)試,檢查單板網(wǎng)絡(luò)是否正常。

C:/tools/iperf-2.0.5-2-win32>ping 192.168.1.10 Pinging 192.168.1.10 with 32 bytes of data: Reply from 192.168.1.10: bytes=32 time=1ms TTL=255 Reply from 192.168.1.10: bytes=32 time

6.6. 電腦iperf測(cè)試

在電腦啟動(dòng)iperf測(cè)試。

C:/tools/iperf-2.0.5-2-win32>iperf -c 192.168.1.10 -i 5 -t 20 -w 2M ------------------------------------------------------------ Client connecting to 192.168.1.10, TCP port 5001 TCP window size: 2.00 MByte ------------------------------------------------------------ [ 3] local 192.168.1.100 port 63484 connected with 192.168.1.10 port 5001 [ ID] Interval Transfer Bandwidth [ 3] 0.0- 5.0 sec 55.4 MBytes 92.9 Mbits/sec [ 3] 5.0-10.0 sec 53.4 MBytes 89.5 Mbits/sec [ 3] 10.0-15.0 sec 53.5 MBytes 89.8 Mbits/sec [ 3] 15.0-20.0 sec 53.4 MBytes 89.5 Mbits/sec [ 3] 0.0-20.0 sec 216 MBytes 90.4 Mbits/sec

6.7. 單板iperf測(cè)試串口打印

在電腦啟動(dòng)啟動(dòng)iperf測(cè)試后,單板串口打印。

[ 1] local 192.168.1.10 port 5001 connected with 192.168.1.100 port 5001 [ ID] Interval Transfer Bandwidth [ 1] 0.0- 5.0 sec 53.2 MBytes 89.3 Mbits/sec [ 1] 5.0-10.0 sec 53.4 MBytes 89.6 Mbits/sec [ 1] 10.0-15.0 sec 53.4 MBytes 89.6 Mbits/sec [ 1] 15.0-20.0 sec 53.4 MBytes 89.6 Mbits/sec [ 1] 0.0-20.2 sec 216 MBytes 89.6 Mbits/sec TCP test passed Successfully 編輯:hfy

-

嵌入式軟件

+關(guān)注

關(guān)注

4文章

245瀏覽量

27275 -

MicroZed

+關(guān)注

關(guān)注

0文章

9瀏覽量

5311

發(fā)布評(píng)論請(qǐng)先 登錄

河北軟件職業(yè)技術(shù)學(xué)院走訪飛凌嵌入式,共同探討產(chǎn)教融合新模式

如何使用AMD Vitis HLS創(chuàng)建HLS IP

如何成為一名嵌入式軟件工程師?

嵌入式開發(fā):高門檻的系統(tǒng)性工程與 996 的行業(yè)困局

想在嵌入式領(lǐng)域高薪就業(yè)?先邁過這些人才門檻!

嵌入式軟件工程師就業(yè)好不好?

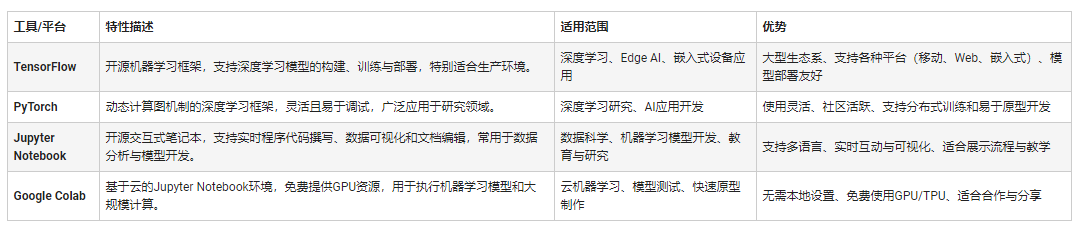

嵌入式機(jī)器學(xué)習(xí)的應(yīng)用特性與軟件開發(fā)環(huán)境

如何提高嵌入式代碼質(zhì)量?

使用AMD Vitis進(jìn)行嵌入式設(shè)計(jì)開發(fā)用戶指南

嵌入式工程師常用的開發(fā)工具有哪些?

嵌入式學(xué)習(xí)建議

什么是嵌入式?一文讀懂嵌入式主板

名單公布!【書籍評(píng)測(cè)活動(dòng)NO.42】 嵌入式Hypervisor:架構(gòu)、原理與應(yīng)用

嵌入式軟件開發(fā)與AI整合

Vitis里如何創(chuàng)建嵌入式軟件工程

Vitis里如何創(chuàng)建嵌入式軟件工程

評(píng)論