本文逐步演示了如何使用 AMD Vitis HLS 來創建一個 HLS IP,通過 AXI4 接口從存儲器讀取數據、執行簡單的數學運算,然后將數據寫回存儲器。接著會在 AMD Vivado Design Suite 設計中使用此 HLS IP,并使用嵌入式 Vitis 應用控制此 HLS IP。

具體的運行和測試條件如下:

操作系統:Ubuntu 20.04

版本:2023.1

注釋:請確保使用您的操作系統支持的版本 -受支持的操作系統:

https://docs.amd.com/r/2023.1-English/ug973-vivado-release-notes-install-license/Supported-Operating-Systems

本文使用的工具流程為 Vitis HLS > Vivado > Vitis IDE。我們將使用 Vitis HLS 創建一個自定義 IP,將該 HLS IP 合并到 Vivado 的硬件設計中,然后創建一個與 HLS IP 通信的 Vitis 應用。該 Vitis 應用將按照自定義硬件上的嵌入式工程所需進行設置。應用代碼將利用自動生成的 HLS API 驅動程序調用來控制 HLS IP 并與之通信。整個流程假設您已經安裝了 Vitis、Vitis HLS 和 Vivado。

1下載并解壓縮 ReferenceDocs 文件夾

將該文件夾保存在所需工作位置。vitis_hls 和 Vivado 各有單獨的文件夾。稍后,可創建自己的 Vitis 應用工程文件夾。

2創建 HLS IP

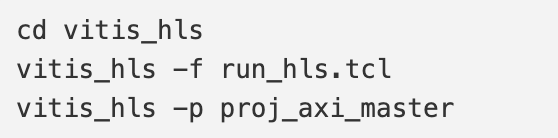

打開 Linux 終端,執行以下命令以便:

進入 vitis_hls 文件夾 - 該文件夾包含 HLS IP 的源代碼。

運行 TCL 腳本來設置 HLS 工程 - 該腳本還將運行 C 語言仿真、C 語言綜合與協同仿真。

在 GUI 中打開 HLS 工程

打開 GUI 后,檢查 example.cpp 源代碼。HLS IP 使用 Volatile 指針和 Memcpy 函數在存儲器上讀取和寫入數據。Memcpy 需要一個緩沖器來存儲存儲器傳輸事務的各項結果。m_axi 接口編譯指示要求此 IP 使用存儲器映射。深度設置為 50 意味著串流在給定時間最多可以容納 50 個未完成的元素,選擇該值是為了匹配緩沖器的大小。s_axilite 接口編譯指示允許此 IP 接受應用的控制,并與 AMD Zynq SoC 器件通信。

使用 GUI 左下角的 Flow Navigator,以便在 GUI 中運行 C 語言仿真、C 語言綜合與協同仿真,查看每項報告并熟悉 IDE。準備就緒后,可以通過在 Flow Navigator 中選擇“Export RTL”來導出 HLS IP,以便在 Vivado 中使用。

3創建 Vivado 平臺

有兩種方法可用于創建 Vivado 平臺。

選項 1:

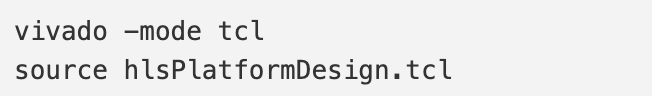

使用以下所示命令從“Vivado”文件夾運行 Tcl 腳本。運行此腳本后,將創建一個 Vivado 工程,隨后可在 GUI 中打開該工程。在 GUI 中,您需要綜合、實現、生成比特流,并導出硬件。

選項 2:

按照以下步驟在 Vivado 中自行創建平臺:

打開 Vivado,并使用 ZCU102 評估板創建一個新工程

將 Vitis HLS IP 添加到 IP 目錄中:

打開 IP 目錄,右鍵單擊并選擇“add Repo”。

瀏覽到導出 IP 的位置,并將“ip”文件夾添加到目錄中。默認路徑為

注釋:如果希望使用不同的位置將 HLS IP 添加到 IP 目錄中,可以使用導出 HLS IP 時創建的export.zip文件:

https://docs.xilinx.com/r/en-US/ug1399-vitis-hls/Exporting-the-RTL-Design

它位于相同的默認路徑中,但您可以將其移至期望的位置,并使用該位置代替“ip”文件夾,以添加到 IP 目錄中。“ip”文件夾所含內容與解壓后 IP 的內容相同。

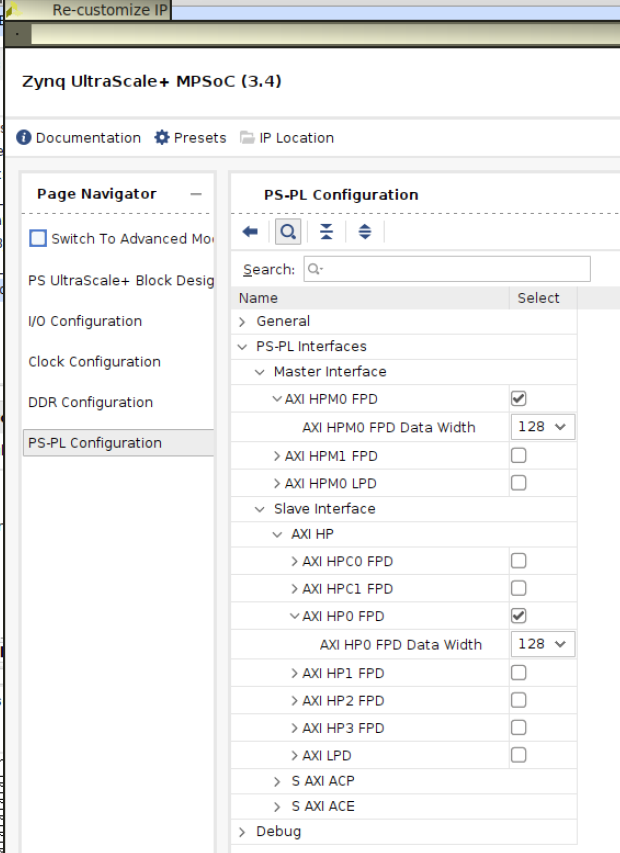

創建一個新的塊設計,并添加 HLS IP 和 Zynq UltraScale+ MPSoC。通過雙擊 Zynq,對其進行自定義。在該設計中,我們添加了 S_AXI_HP0_FPD 端口。該評估板默認啟用 DDR,但請在“DDR Configurations”選項卡中確認 DDR 是否已啟用。

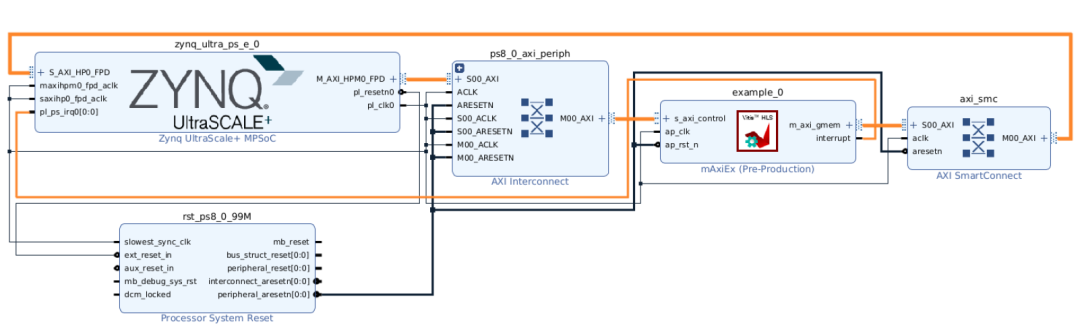

使用設計輔助來運行自動連接。它將通過 AXI Interconnect 和 AXI SmartConnect 自動連接 Zynq 和 HLS IP。

須手動將 HLS IP 上的中斷端口連接到 Zynq 上的 pl_ps_irq 端口。此時設計應與以下截屏相似:

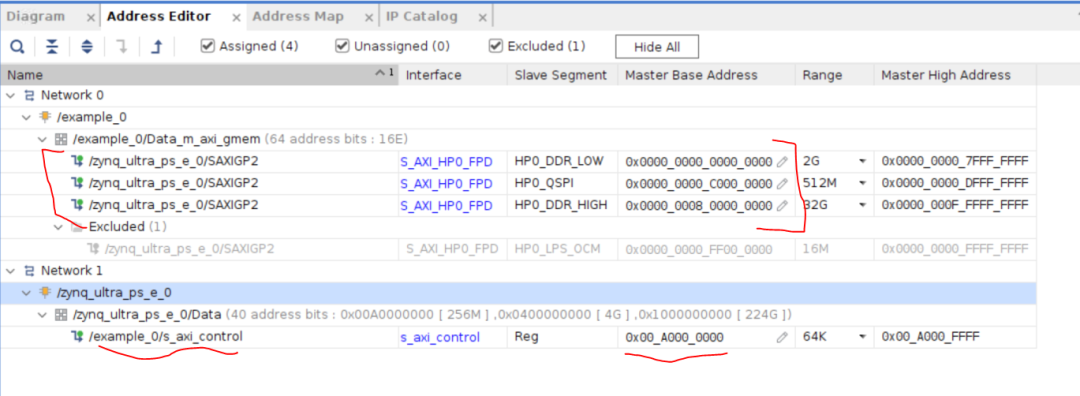

打開“Address Editor”選項卡,確保已如下所示分配了所有地址。

確認該設計。如果沒有錯誤,則運行綜合、實現和生成比特流的步驟。完成后,選擇“File > Export > Export Hardware”導出設計,并將 XSA 文件保存到期望的位置。

注釋:在導出硬件時,確保選擇“Include bitstream”。

4創建 Vitis 應用

打開 Vitis 并選擇“Create Application Project”- 這適用于獨立的嵌入式系統。

對于平臺選擇,請選擇“Create a new platform from hardware (XSA)”選項卡,并瀏覽到您在上一節中創建的 XSA 文件所在位置。單擊“Next”。

確保選中“Generate boot components”以及“psu_cortexa53_0”。在下一個框中按需更改平臺名稱,然后單擊“Next”。

命名應用工程。系統名稱將使用相同的標題。選擇處理器“psu_cortexa53_0”。單擊“Next”。

對于“Domain”選擇,請確保操作系統設置為“standalone”,且架構為 64 位。單擊“Next”。

對于模板,請選擇“Empty C Application”。

設置源代碼

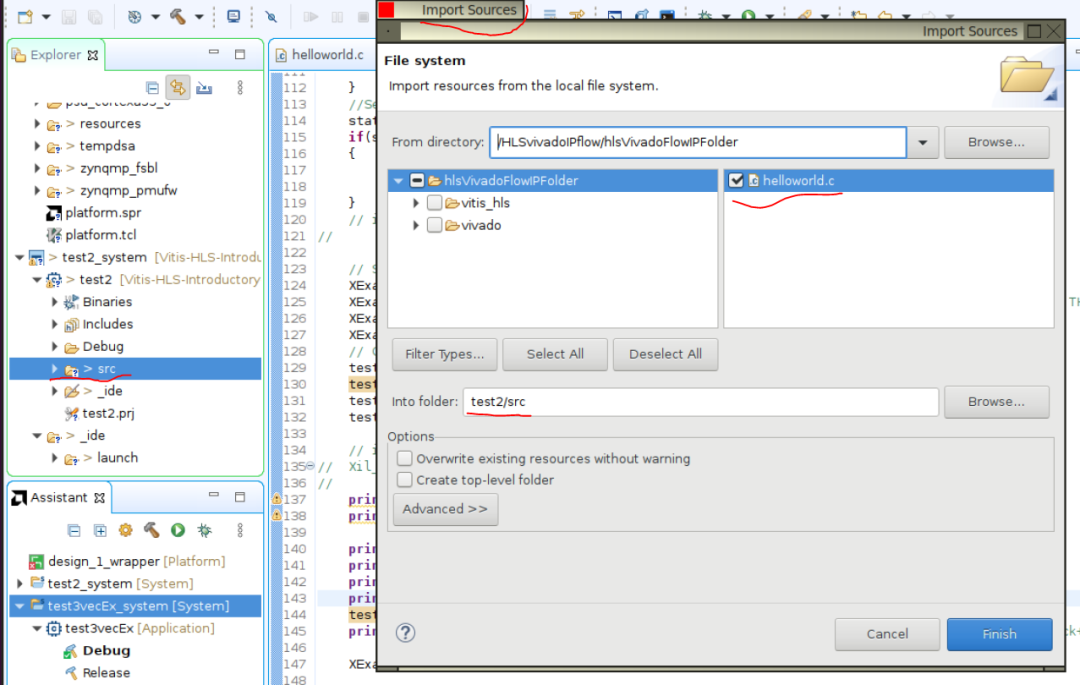

在 GUI 中打開 Vitis 工程后,在左側的“Explorer”選項卡中右鍵單擊 projectName_system/projectName/src,然后選擇“Import Sources”。在彈出窗口中,瀏覽至源代碼所在的文件夾。

添加 helloworld.c,它位于“閱讀原文”底部的壓縮文件夾中,然后從文件列表中選擇 helloworld.c,如下圖所示。接著單擊“Finish”。

檢查 helloworld.c。整個過程中都有注釋用于解釋每一節的作用。以“XExample”開頭的數據類型和函數調用是自動生成的 API 調用,用來控制 HLS IP 并與之通信。

關鍵要點包括:須創建一個 Vitis HLS IP 實例,如第 14 行所示,并使用 API 調用來獲取/設置 IP 與數據并且啟動它(第 34、35 和 48 行)。

此時還須完成另一項不尋常的操作,即,使用 Xil_DCacheInvalidate() 函數,告訴處理器對 DDR(而非其高速緩存)執行讀取/寫入操作,以確保處理器和 HLS IP 在相同的位置執行讀取/寫入。

構建并運行工程

構建系統工程。這將構建整個工程,包括平臺和應用。右鍵單擊系統工程或選擇錘子圖標。還可以使用左下角的應用助手來構建和運行設計。

該工程未經軟件仿真測試,因為這需要執行額外的步驟,不在本博客的討論范圍之內。但在 ZCU102 評估板上,已通過選擇“Run As”選項中的“Launch Hardware”來對該工程進行了測試和驗證。當連接到該評估板時,您還可以運行調試器并單步執行代碼。您可使用終端連接到 UART (com0),以查看硬件上的輸出。

參考文件

HLS - Tcl 腳本 - run_hls.tcl

HLS - 源代碼 - example.cpp 和測試激勵文件

Vivado - 從 write_project_tcl 創建的 Tcl 腳本

Vitis - 應用源代碼

-

amd

+關注

關注

25文章

5594瀏覽量

136557 -

接口

+關注

關注

33文章

9032瀏覽量

153949 -

Vivado

+關注

關注

19文章

835瀏覽量

68967 -

Vitis

+關注

關注

0文章

150瀏覽量

7979

原文標題:開發者分享|AMD Vitis? HLS 系列 1 - AMD Vivado? IP 流程(Vitis 傳統 IDE)

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA高層次綜合HLS之Vitis HLS知識庫簡析

使用Vitis HLS創建屬于自己的IP相關資料分享

Vivado HLS和Vitis HLS 兩者之間有什么區別

Vitis HLS工具簡介及設計流程

使用AXI4-Lite將Vitis HLS創建的IP連接到PS

如何使用AMD Vitis HLS創建HLS IP

如何使用AMD Vitis HLS創建HLS IP

評論