您是否擔(dān)心 RTL 設(shè)計中的延遲?

您的設(shè)計是否有效并經(jīng)過優(yōu)化?

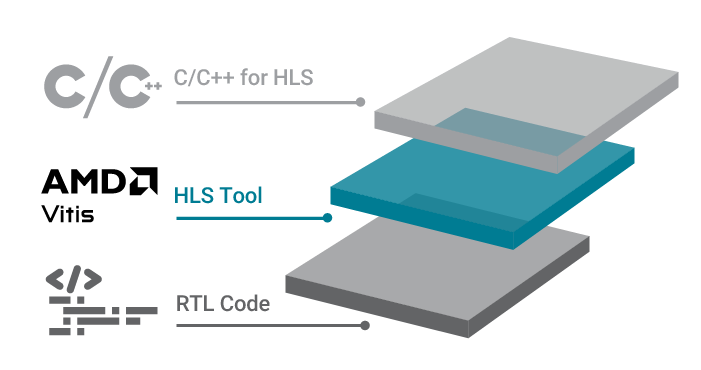

通過 Vitis HLS,您可將 C/C++ 函數(shù)綜合到 RTL 中,從而輕松創(chuàng)建復(fù)雜設(shè)計算法。

AMD Vitis HLS 工具允許用戶通過將 C/C++ 函數(shù)綜合成 RTL,輕松創(chuàng)建復(fù)雜的 FPGA 算法。Vitis HLS 工具與 Vivado Design Suite(用于綜合、布置和布線)及 Vitis 統(tǒng)一軟件平臺(用于所有異構(gòu)系統(tǒng)設(shè)計和應(yīng)用)高度集成。

使用 Vitis HLS 流程,用戶可針對 C 代碼應(yīng)用指令,創(chuàng)建專門用于所需實(shí)現(xiàn)方案的 RTL。

不僅可從 C 語言源代碼創(chuàng)建多個設(shè)計架構(gòu),而且還可啟用用于高質(zhì)量 Correct-by-Construction RTL 的路徑。

C 語言仿真可用于驗(yàn)證設(shè)計,支持比基于 RTL 的傳統(tǒng)仿真更快的迭代。

Vitis HLS 工具具有一系列豐富的分析及調(diào)試工具,其可促進(jìn)設(shè)計優(yōu)化。

全新推出的Vitis HLS資源,具有以下特點(diǎn):

較之傳統(tǒng)的 RTL,Vitis HLS 可實(shí)現(xiàn)更快的設(shè)計驗(yàn)證和更高效的迭代

通過 Vitis HLS,開發(fā)者可使用 C/C++ 代碼中的自動 pragma 推理、流水線循環(huán)和函數(shù)等高級功能來滿足系統(tǒng)性能要求

審核編輯 :李倩

-

amd

+關(guān)注

關(guān)注

25文章

5537瀏覽量

135515 -

源代碼

+關(guān)注

關(guān)注

96文章

2948瀏覽量

67508 -

Vitis

+關(guān)注

關(guān)注

0文章

147瀏覽量

7759

原文標(biāo)題:AMD 全新Vitis HLS資源現(xiàn)已推出

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發(fā)者社區(qū)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

新思科技推出全新硬件輔助驗(yàn)證產(chǎn)品組合

使用AMD Vitis進(jìn)行嵌入式設(shè)計開發(fā)用戶指南

全新AMD Vitis統(tǒng)一軟件平臺2024.2版本發(fā)布

AMD Vitis Unified Software Platform 2024.2發(fā)布

AMD Vivado Design Suite 2024.2全新推出

U50的AMD Vivado Design Tool flow設(shè)置

AMD全新處理器擴(kuò)大數(shù)據(jù)中心CPU的領(lǐng)先地位

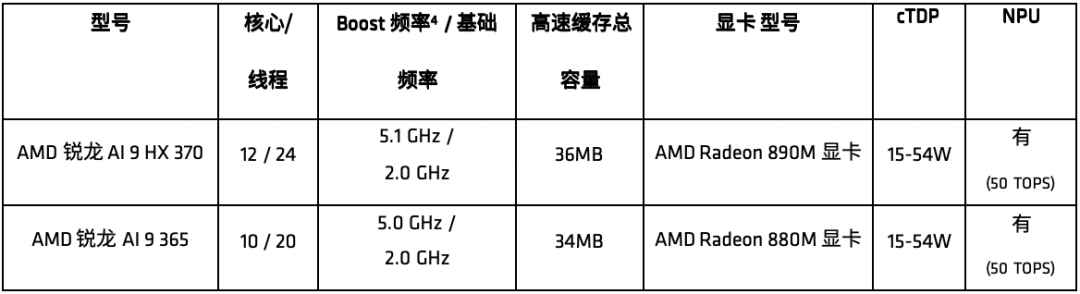

AMD推出全新銳龍AI 300系列處理器

AMD Vivado Design Suite 2024.1全新推出

一種在HLS中插入HDL代碼的方式

一個更適合工程師和研究僧的FPGA提升課程

AMD推出全新AMD銳龍和EPYC處理器,擴(kuò)大數(shù)據(jù)中心和PC領(lǐng)域領(lǐng)先地位

PROPHESEE 攜手 AMD,推出業(yè)界首款兼容 Kria? KV260 視覺 AI 入門套件的事件視覺解決方案

AMD Vitis?設(shè)計工具中的Libraries新功能介紹

在Windows 10上創(chuàng)建并運(yùn)行AMD Vitis?視覺庫示例

AMD全新Vitis HLS資源現(xiàn)已推出

AMD全新Vitis HLS資源現(xiàn)已推出

評論