本文逐步演示了如何使用 AMD Vitis HLS 來創(chuàng)建一個 HLS IP,通過 AXI4 接口從存儲器讀取數(shù)據(jù)、執(zhí)行簡單的數(shù)學(xué)運(yùn)算,然后將數(shù)據(jù)寫回存儲器。接著會在 AMD Vivado Design Suite 設(shè)計(jì)中使用此

![的頭像]() 發(fā)表于

發(fā)表于 06-13 09:50

?683次閱讀

這篇文章在開發(fā)者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 傳統(tǒng) IDE) 的基礎(chǔ)上撰寫,但使用的是 AMD Vitis Unifie

![的頭像]() 發(fā)表于

發(fā)表于 06-20 10:06

?1017次閱讀

組件開始,該組件可以導(dǎo)出為 XO 文件用于 Vitis 系統(tǒng)工程;這與“自上而下的流程”相反,后者從 Vitis 工程開始,然后將

![的頭像]() 發(fā)表于

發(fā)表于 07-02 10:55

?500次閱讀

,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統(tǒng)一將HLS集成到Vitis里了,集成之后增加了一些功能,同時將這部分開源出來了。

發(fā)表于 09-07 15:21

1、使用Vitis HLS創(chuàng)建屬于自己的IP高層次綜合(High-level Synthesis)簡稱HLS,指的是將高層次語言描述的邏輯結(jié)構(gòu),自動轉(zhuǎn)換成低抽象級語言描述的電路模型的過程。對于AMD

發(fā)表于 09-09 16:45

來的是VivadoIP,用于支持Vivado IP 設(shè)計(jì)流程。后者用于Vitis應(yīng)用加速流程,此時,Vitis HLS會自動推斷接口,無需在代碼里通過Pragma或Directive的方式定義Interface,最終會輸出.

![的頭像]() 發(fā)表于

發(fā)表于 11-05 17:43

?4w次閱讀

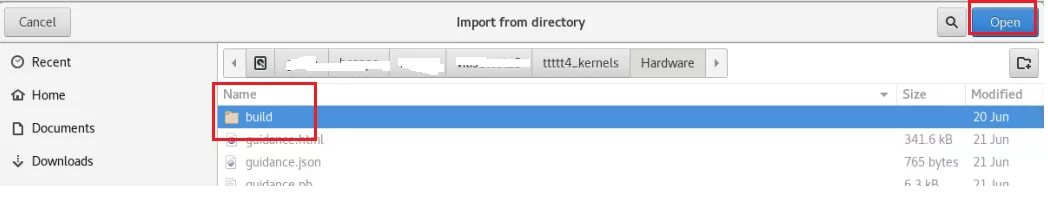

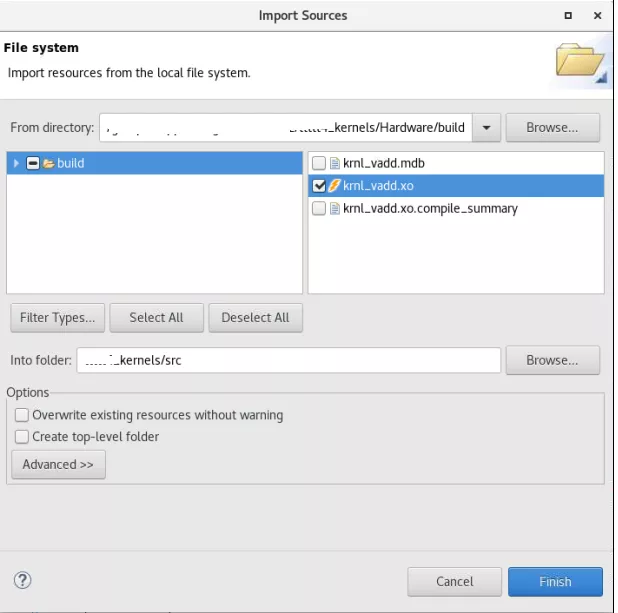

Q1 HLS導(dǎo)出的.xo文件如何導(dǎo)入到Vitis里面?需要把.xo

![的頭像]() 發(fā)表于

發(fā)表于 08-26 17:03

?2995次閱讀

Vitis HLS 是一種高層次綜合工具,支持將 C、C++ 和 OpenCL 函數(shù)硬連線到器件邏輯互連結(jié)構(gòu)和 RAM/DSP 塊上。Vitis HLS 可在

![的頭像]() 發(fā)表于

發(fā)表于 05-25 09:43

?2835次閱讀

Vitis HLS 工具能夠?qū)?C++ 和 OpenCL 功能部署到器件的邏輯結(jié)構(gòu)和 RAM/DSP 塊上。在 GitHub 上提供 Vitis HLS 前端為研究人員、開發(fā)人員和編譯

![的頭像]() 發(fā)表于

發(fā)表于 08-03 09:53

?1238次閱讀

對于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統(tǒng)一將HLS集成到Vitis里了,集成之后增加了一些功能,同時將這部分開

![的頭像]() 發(fā)表于

發(fā)表于 09-02 09:06

?4058次閱讀

相比于VivadoHLS,Vitis HLS更加智能化,這體現(xiàn)在Vitis HLS可以自動探測C/C++代碼中可并行執(zhí)行地部分而無需人工干預(yù)添加

![的頭像]() 發(fā)表于

發(fā)表于 11-24 11:42

?2131次閱讀

AMD Vitis HLS 工具允許用戶通過將 C/C++ 函數(shù)綜合成 RTL,輕松創(chuàng)建復(fù)雜的 FPGA 算法。Vitis HLS 工具與 Vivado Design Suite(用于

![的頭像]() 發(fā)表于

發(fā)表于 04-23 10:41

?1432次閱讀

Xilinx平臺的Vivado HLS 和 Vitis HLS 使用的 export_ip 命令會無法導(dǎo)出 IP

![的頭像]() 發(fā)表于

發(fā)表于 07-07 14:14

?1254次閱讀

Vitis? HLS 2023.1 支持新的 L1 庫向?qū)В疚膶⒅v解如何下載 L1 庫、查看所有可用功能以及如何在 Vitis HLS GUI 中使用庫函數(shù)。

![的頭像]() 發(fā)表于

發(fā)表于 08-16 10:26

?1594次閱讀

電子發(fā)燒友網(wǎng)站提供《Vitis HLS移植指南.pdf》資料免費(fèi)下載

發(fā)表于 09-13 09:21

?0次下載

Vitis HLS如何添加HLS導(dǎo)出的.xo文件

Vitis HLS如何添加HLS導(dǎo)出的.xo文件

評論