1、綜合約束

在“設置”對話框的“約束”部分下,選擇“默認約束設置”作為活動約束設置;包含在Xilinx設計約束(XDC)文件中捕獲的設計約束的一組文件,可以將其應用于設計中。兩種類型的設計約束是:

1) 物理約束:這些約束定義引腳的位置以及單元(例如Block RAM,LUT,觸發器和設備配置設置)的絕對或相對位置。

2) 時序約束:這些約束定義了設計的頻率要求。由于沒有時序限制,Vivado設計套件僅針對線長度和布局擁堵來優化設計。

2、綜合策略

1) Defaults(默認設置)

2) RuntimeOptimized

執行較少的時序優化,并消除一些RTL優化以減少綜合運行時間。

3) AreaOptimized_high

執行常規面積優化,包括強制執行三進制加法器,在比較器中使用新閾值以使用進位鏈以及實現面積優化的多路復用器。

4) AreaOptimized_medium

執行常規面積優化,包括更改控制集優化的閾值,強制執行三進制加法器,將推理的乘法器閾值降低到DSP模塊,將移位寄存器移入BRAM,在比較器中使用較低閾值以使用進位鏈,以及進行區域優化的MUX操作。

5) AlternateRoutability

一組提高路由能力的算法(較少使用MUXF和CARRY)。

6) AreaMapLargeShiftRegToBRAM

檢測大型移位寄存器,并使用專用的Block RAM實現它們。

7) AreaMultThresholdDSP

專用DSP塊推斷的下限閾值。

8) FewerCarryChains

較高的操作數大小閾值以使用LUT代替進位鏈。

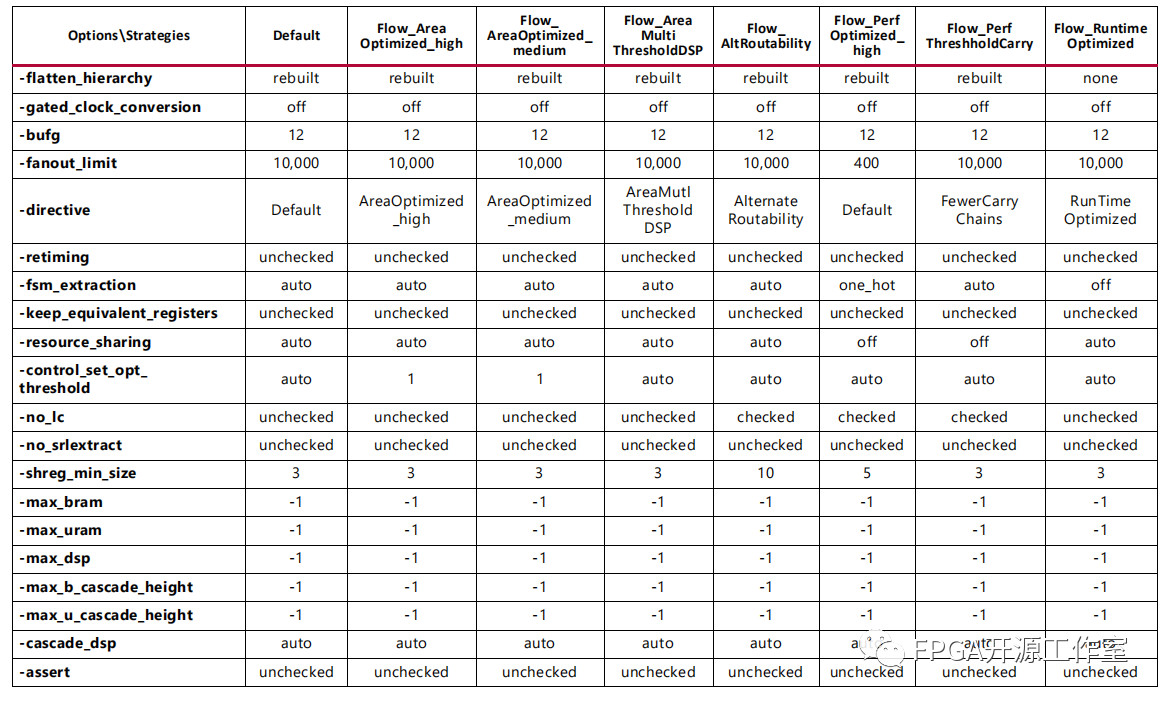

3、其他選項

-flatten_hierarchy:確定Vivado綜合如何控制層次結構。

- none:指示綜合工具不要展平層次結構。綜合的輸出與原始RTL具有相同的層次結構。

-full :指示工具完全展平層次結構,僅保留頂層。

-rebuilt:設置后,重新構建允許綜合工具展平層次結構,執行綜合,然后基于原始RTL重建層次結構。該值使QoR受益于跨邊界優化,其最終層次類似于RTL,以便于分析。

-gated_clock_conversion:啟用和禁用綜合工具轉換時鐘邏輯的功能。

-bufg: 控制工具在設計中推斷出多少BUFG。當設計網表中的其他BUFG對合成過程不可見時,Vivado設計工具將使用此選項。該工具可以推斷出指定的數量,并跟蹤RTL中實例化的BUFG數量。例如,如果-bufg選項設置為12,并且在RTL中實例化了三個BUFG,則Vivado綜合工具最多可以推斷出另外九個BUFG。

-fanout_limit:指定信號在開始復制邏輯之前必須驅動的負載數。此全局限制是一般指南,當工具確定有必要時,可以忽略該選項。

-retiming :布爾選項

-fsm_extraction : 控制綜合如何提取和映射有限狀態機。 FSM_ENCODING更詳細地描述了這些選項。

FSM_ENCODING可以放在狀態機寄存器上。合法的值是“ one_hot”,“ sequential”,“johnson”,“ gray”,“ auto”和“ none”。“ auto”值是默認值,并允許該工具確定最佳編碼。可以在RTL或XDC中設置此屬性。

-keep_equivalent_registers :防止合并具有相同輸入邏輯的寄存器。

-resource_sharing:設置不同信號之間的算術運算符共享。這些值是自動的,打開的和關閉的。自動值集執行資源共享以取決于設計時間。

-control_set_opt_threshold: 將時鐘使能優化的閾值設置為較少的控制集。默認值為自動,這意味著該工具將根據目標設備選擇一個值。支持任何正整數值。

給定值是工具將控制集移入寄存器的D邏輯所需的扇出數量。如果扇出大于該值,則該工具嘗試使該信號驅動該寄存器上的control_set_pin。

-no_lc:選中后,此選項將關閉LUT合并。

-no_srlextract:選中后,此選項將關閉完整設計的SRL提取,以便將其實現為簡單寄存器。

-shreg_min_size:推斷SRL的閾值。默認設置為3。這將設置順序元素的數量,這些元素將導致推斷固定延遲鏈的SRL(靜態SRL)。策略也將此設置定義為5和10。

-max_bram:描述設計中允許的最大塊RAM數量。通常在設計中有黑匣子或第三方網表時使用此選項,并允許設計人員為這些網表節省空間。

-max_uram:設置設計中允許的最大UltraRAM(UltraScale+?設備塊RAM)塊。默認設置為-1表示該工具選擇指定零件允許的最大數量。

-max_dsp:描述設計中允許的最大塊DSP數量。通常在設計中有黑匣子或第三方網表時使用,并為這些網表留出空間。默認設置為-1表示該工具選擇指定零件允許的最大數量。

-max_bram_cascade_height:控制該工具可以級聯的BRAM的最大數量。默認設置為-1表示該工具選擇指定零件允許的最大數量。

-max_uram_cascade_height:控制該工具可以級聯的UltraScale+設備UltraRAM塊的最大數量。默認設置為-1表示該工具選擇指定零件允許的最大數量。

-cascade_dsp: 控制如何實現總和DSP模塊輸出中的加法器。默認情況下,使用塊內置加法器鏈計算DSP輸出的總和。價值樹迫使總和在結構中實現。值是:auto,tree和force。默認為自動。

-no_timing_driven: (可選)禁用默認的時序驅動綜合算法。這導致減少了綜合運行時間,但忽略了時序對綜合的影響。

-sfcu:在單文件編譯單元模式下運行綜合。

-assert: 啟用要評估的VHDL斷言語句。故障或錯誤的嚴重性級別會停止綜合流程并產生錯誤。警告的嚴重性級別會生成警告。

tcl.pre和tcl.post選項是在合成之前和之后立即運行的Tcl文件的掛鉤。

4、Tcl Commands to Get Property

get_property DIRECTORY [current_project] get_property DIRECTORY [current_run]

編輯:hfy

-

FPGA

+關注

關注

1644文章

21991瀏覽量

615270 -

Xilinx

+關注

關注

73文章

2184瀏覽量

124575 -

Vivado

+關注

關注

19文章

834瀏覽量

68366

發布評論請先 登錄

FPGA時序約束之設置時鐘組

Vivado HLS設計流程

Vivado FIR IP核實現

【米爾-Xilinx XC7A100T FPGA開發板試用】Key-test

助力AIoT應用:在米爾FPGA開發板上實現Tiny YOLO V4

Xilinx_Vivado_SDK的安裝教程

采用Xilinx FPGA的AFE79xx SPI啟動指南

正點原子fpga開發指南

Vivado使用小技巧

Xilinx FPGA案例學習之Vivado設計綜合約束

Xilinx FPGA案例學習之Vivado設計綜合約束

評論