1 I/O延遲約束介紹

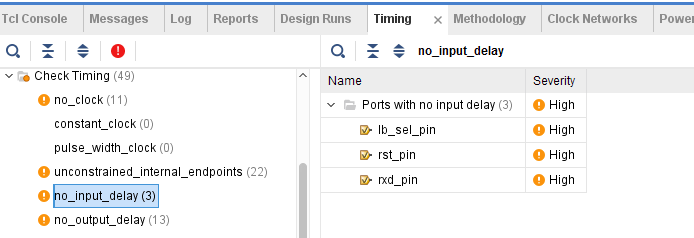

要在設(shè)計中精確建模外部時序,必須為輸入和輸出端口提供時序信息。Xilinx Vivado集成設(shè)計環(huán)境(IDE)僅在FPGA邊界內(nèi)識別時序,因此必須使用以下命令指定超出這些邊界的延遲值:

1,set_input_delay

2,set_output_delay

2 輸入延遲(Input Delay)

set_input_delay命令指定輸入端口上相對于設(shè)計接口處時鐘邊沿的輸入路徑延遲。

在考慮應(yīng)用板時,輸入延遲表示以下各項之間的相位差:

A.數(shù)據(jù)從外部芯片通過電路板傳播到FPGA的輸入封裝引腳。

B.相關(guān)的板上參考時鐘

輸入延遲值可以是正的或負(fù)的,這取決于設(shè)備接口處的時鐘和數(shù)據(jù)相對相位。

雖然-clock選項在Synopsys設(shè)計約束(SDC)標(biāo)準(zhǔn)中是可選的,但它是Vivado IDE所必需的。相對時鐘可以是設(shè)計時鐘或虛擬時鐘。

使用set_input_delay命令選項

例1:此示例定義了相對于先前定義的sysClk的輸入延遲,用于最小和最大分析。

》 create_clock -name sysClk -period 10 [get_ports CLK0]

》 set_input_delay -clock sysClk 2 [get_ports DIN]

例2:此示例定義相對于先前定義的虛擬時鐘的輸入延遲。

》 create_clock -name clk_port_virt -period 10

》 set_input_delay -clock clk_port_virt 2 [get_ports DIN]

例3:此示例為min分析和最大分析相對于sysClk的定義了不同的輸入延遲值。

》 create_clock -name sysClk -period 10 [get_ports CLK0]

》 set_input_delay -clock sysClk -max 4 [get_ports DIN]

》 set_input_delay -clock sysClk -min 1 [get_ports DIN]

例4:要限制I / O端口之間的純組合路徑,必須在I / O端口上相對于先前定義的虛擬時鐘定義輸入和輸出延遲。以下示例在端口DIN和DOUT之間的組合路徑上設(shè)置5 ns(10 ns - 4 ns - 1 ns)約束:

》 create_clock -name sysClk -period 10 [get_ports CLK0]

》 set_input_delay -clock sysClk 4 [get_ports DIN]

》 set_output_delay -clock sysClk 1 [get_ports DOUT]

例5:此示例指定相對于DDR時鐘的輸入延遲值。

》 create_clock -name clk_ddr -period 6 [get_ports DDR_CLK_IN]

》 set_input_delay -clock clk_ddr -max 2.1 [get_ports DDR_IN]

》 set_input_delay -clock clk_ddr -max 1.9 [get_ports DDR_IN] -clock_fall -add_delay

》 set_input_delay -clock clk_ddr -min 0.9 [get_ports DDR_IN]

》 set_input_delay -clock clk_ddr -min 1.1 [get_ports DDR_IN] -clock_fall -add_delay

3 輸出延遲(Output Delay)

set_output_delay命令指定輸出端口相對于設(shè)計接口處的時鐘邊沿的輸出路徑延遲。

在考慮開發(fā)板時,此延遲表示以下兩者之間的相位差:

A.數(shù)據(jù)從FPGA的輸出封裝引腳傳播,通過電路板傳輸?shù)搅硪粋€器件

B. 相對參考板時鐘。

輸出延遲值可以是正數(shù)或負(fù)數(shù),具體取決于FPGA外部的時鐘和數(shù)據(jù)相對相位。

使用set_output_delay命令選項:

例1:此示例定義了相對于先前定義的sysClk的輸出延遲,用于最小和最大分析。

》 create_clock -name sysClk -period 10 [get_ports CLK0]

》 set_output_delay -clock sysClk 6 [get_ports DOUT]

例2:此示例定義相對于先前定義的虛擬時鐘的輸出延遲。

》 create_clock -name clk_port_virt -period 10

》 set_output_delay -clock clk_port_virt 6 [get_ports DOUT]

例3:此示例指定相對于DDR時鐘的輸出延遲值,其具有用于min(hold)和max(setup)分析的不同值。

》 create_clock -name clk_ddr -period 6 [get_ports DDR_CLK_IN]

》 set_output_delay -clock clk_ddr -max 2.1 [get_ports DDR_OUT]

》 set_output_delay -clock clk_ddr -max 1.9 [get_ports DDR_OUT] -clock_fall -add_delay

》 set_output_delay -clock clk_ddr -min 0.9 [get_ports DDR_OUT]

》 set_output_delay -clock clk_ddr -min 1.1 [get_ports DDR_OUT] -clock_fall -add_delay

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1644文章

21991瀏覽量

615264 -

Xilinx

+關(guān)注

關(guān)注

73文章

2184瀏覽量

124575 -

參考時鐘

+關(guān)注

關(guān)注

0文章

6瀏覽量

3052

發(fā)布評論請先 登錄

vivado約束參考文檔

如何使用TX_ClK_o作為參考時鐘來設(shè)置輸出延遲?

Xilinx工具vivado使用約束命令時出現(xiàn)警告的解決辦法?

FPGA設(shè)計約束技巧之XDC約束之I/O篇 (上)

FPGA設(shè)計約束技巧之XDC約束之I/O篇(下)

Xilinx Vivado I/O延遲約束介紹

Xilinx Vivado I/O延遲約束介紹

評論