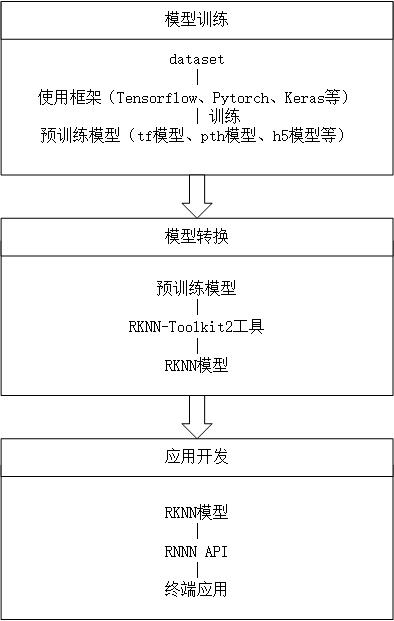

GPIO的結構體系

zynq的GPIO,分為兩種,MIO(multiuse I/O)和EMIO(extendable multiuse I/O)。

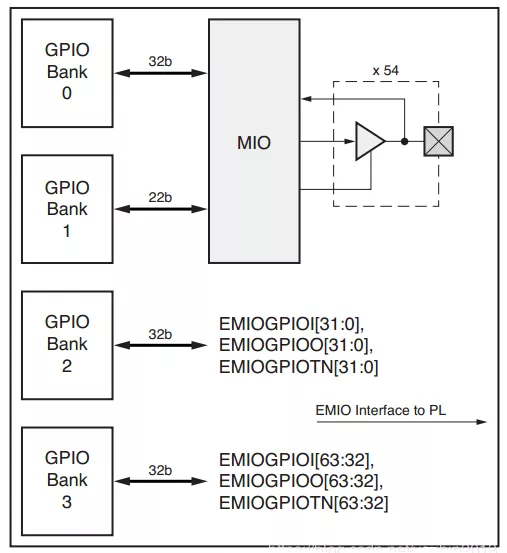

ZYNQ的GPIO由4個BANK組成,其體系結構如圖1所示。其中Bank0有32個GPIO引腳,Bank1有22個引腳,共54個GPIO引腳直接通過MIO連接到PS上,每個引腳可以通過寄存器的設置來確定該引腳為輸入、輸出或者中斷,因為54個MIO引腳直接連接在PS上,像其他普通ARM一樣,不需要通過XPS進行硬件配置,直接通過SDK編程即可。

Bank2和Bank3通過EMIO接口將CPU的GPIO連接到PL部分的引腳上,其中每個Bank各有32個引腳,通過EMIO擴展的GPIO連接到PL上,可以在PL部分進行邏輯設計,進行特定功能的IP核制定。然后在PS部分,像控制普通MIO一樣進行編程。因此,使用EMIO引腳必須通過XPS進行硬件配置,然后在PS部分使用SDK進行編程控制。

圖1 GPIO的組成

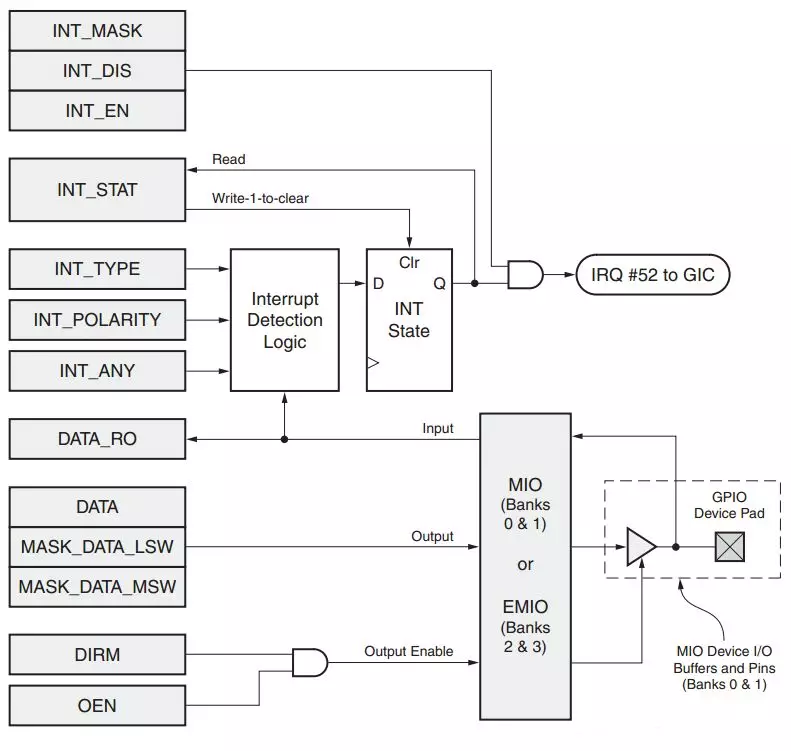

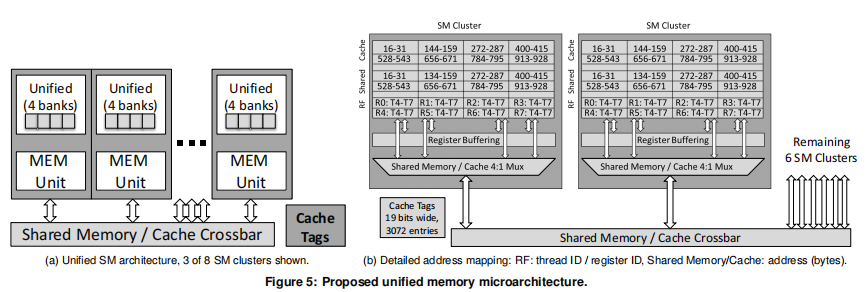

GPIO的內部結構和內部數據流及寄存器結構如圖2所示。上半部分為GPIO中斷相關的寄存器,下半部分為GPIO查詢方式讀寫的寄存器。

圖2 GPIO寄存器數據流組成

DATA_RO寄存器是讀取GPIO引腳值寄存器,不論該GPIO引腳配置為輸入還是輸出,都能正確讀取該GPIO引腳值。如果該引腳的功能沒有配置成GPIO功能,讀取的值為隨機值,因為該寄存器只能讀取GPIO引腳值。

DATA寄存器的值是要輸出到GPIO引腳上的數值,當讀取該寄存器的數值時,結果是前一次寫入DATA寄存器里的數值,而不是當前GPIO引腳的數值。

MASK_DATA_LSW和MASK_DATA_MSW寄存器是傳統的數據寄存器(DATA)和屏蔽寄存器(MASK)的結合,該寄存器32位,分成高16位和低16位,其中高16位作為傳統的MASK使用,低16位作為傳統的DATA使用。因此,MASK_DATA_LSW是對GPIO的16位引腳進行設置和屏蔽寄存器。當某位在MASK_DATA_LSW高16位屏蔽時,即使修改MASK_DATA_LSW低16位的數據,也不影響該位GPIO值。

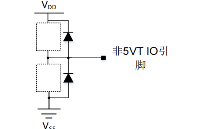

DIRM寄存器是方向控制寄存器,控制GPIO的輸入或者輸出,該寄存器值不影響輸入,即GPIO輸入功能始終有效。

OEN寄存器是輸出時能寄存器,當GPIO引腳被配置成輸出引腳時,該寄存器控制該引腳是否輸出;當GPIO引腳被配置成輸出禁止時,該引腳為三態;當OEN[x] = 0時,輸出無效。

GPIO使用實例

ZYNQ核的添加及配置

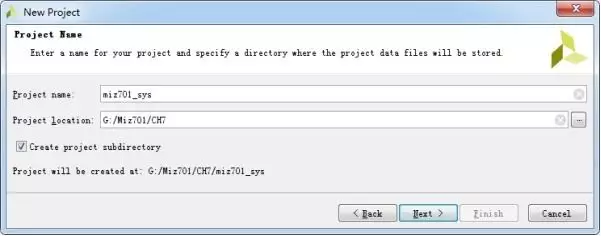

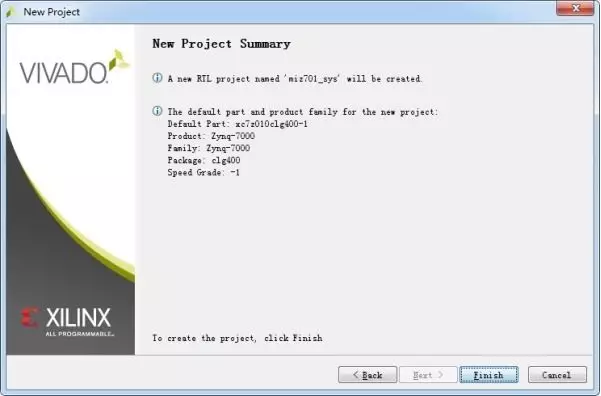

Step1:新建一個名為為Miz701_sys的工程

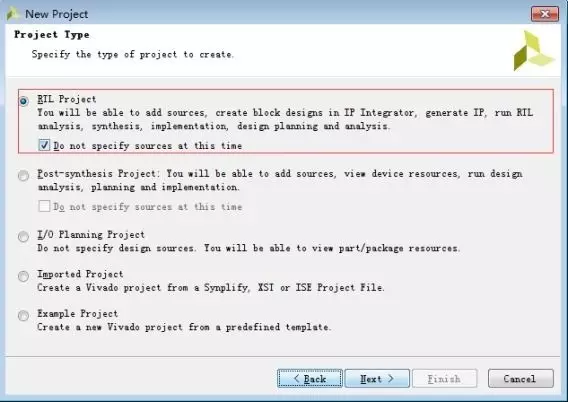

Step2:選擇RTL Project 勾選Do not specify source at this time

Step3:選擇芯片型號xc7z010clg400-1

Step4:單擊Finish

使用IP Integrator創建硬件系統

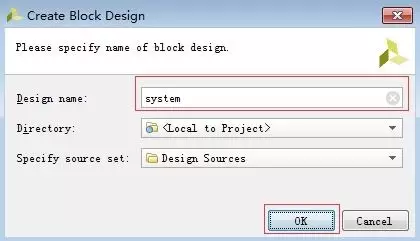

Step1:單擊Create Block Design

Step2:輸入system

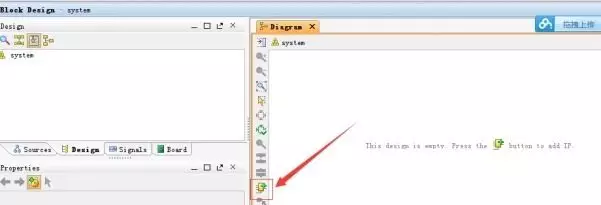

Step3:添加IP按鈕

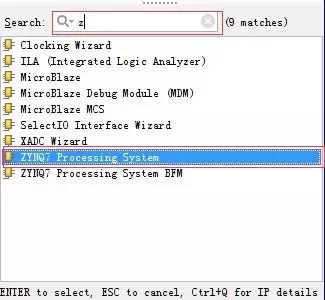

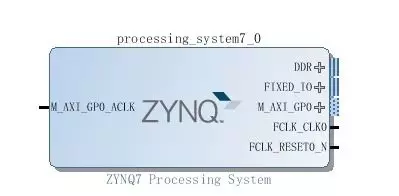

Step4:搜素單詞z選擇ZYNQ7 Processing System,然后雙擊

Step5:添加進來了ZYNQ CPU IP,雙擊ZYNQ CPU IP。

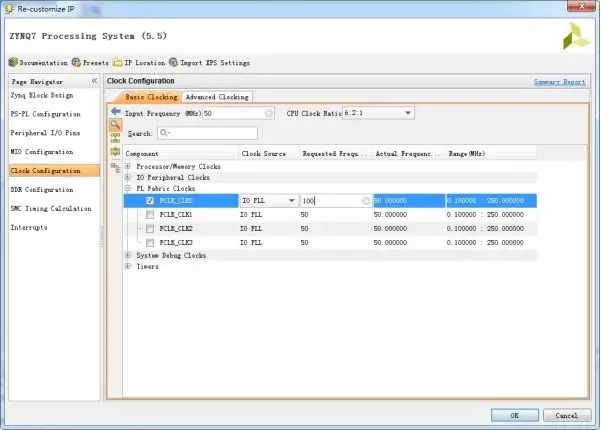

Step6: 修改時鐘輸入為50MHZ,可以看到ARM時鐘為650MHZ DDR為525MHZ(1050MHZ),并且修改FCLK_CLK0 為100MHZ

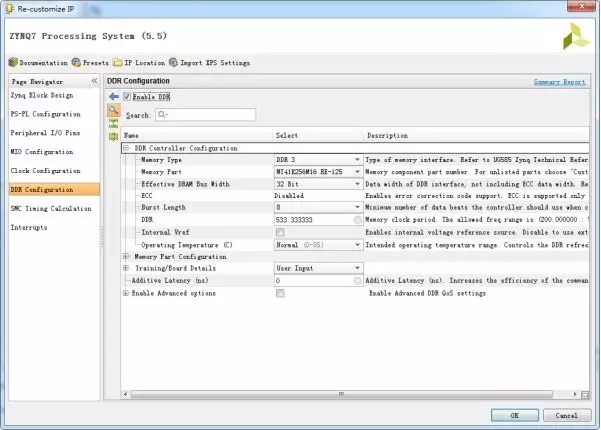

step7:修改內存型號為MT41K256M16RE-125 M,單擊OK。

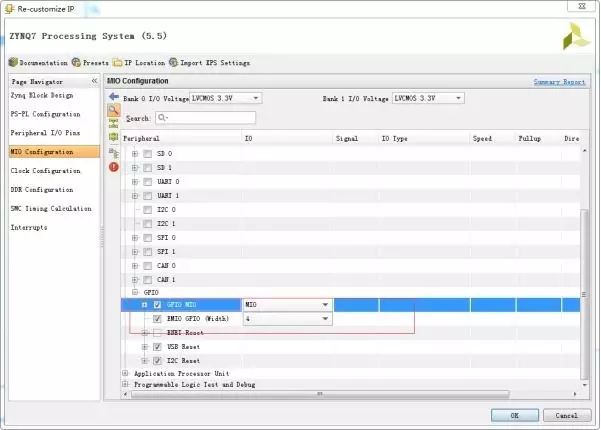

Setp8:選擇MIO Configuration選項卡,再看到I/O Peripherals 中的GPIO一欄,勾選上其中的EMIO一欄,并選擇4位引腳輸出(最多可以選擇64位,但是這個使用只需要4位足夠了)。

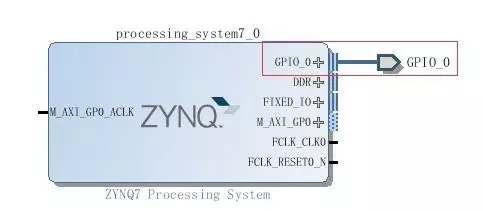

Setp9:按照上圖設置好了之后,點擊OK,仔細觀察發現的zynq核心多出一組引腳名為GPIO_0,這個正是我們剛剛設置的一組EMIO,我們右擊該引腳,選擇make external把GPIO_0引腳引出(或者單擊該引腳處,按快捷鍵Ctrl +t,也可以將引腳引出)。效果如下圖所示:

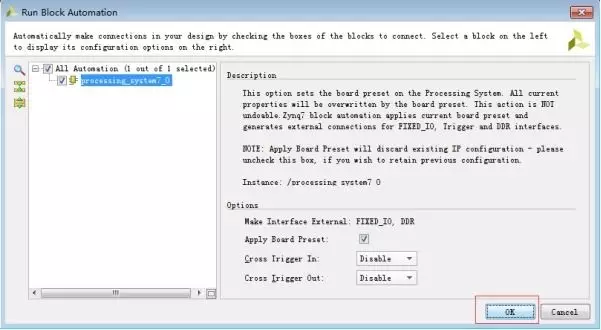

step10::單擊Run Block Automation 進行自動連線,VIVADO軟件會根據信號的命名規則智能連線。

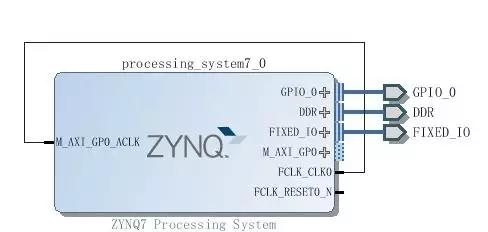

Step11:在你點擊了OK后,你會發現DDR以及FICED_IO自動的延伸出來,然后把時鐘FCLK_CLK0和M_AXI_GPI0_ACLK連接,其實就是給M_AXI_GP0_ACLK提供一個時鐘。方法:當把鼠標靠近的時候會自動連接。

產生HDL和約束文件

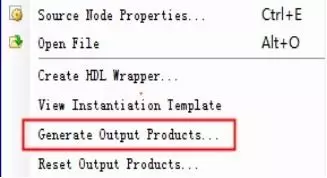

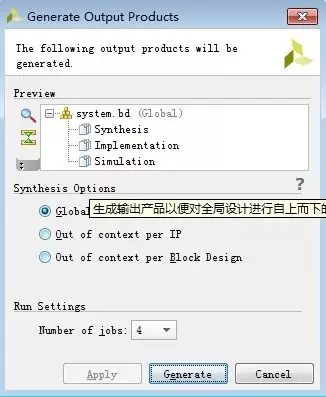

Setp1:接下來依然是,右鍵單擊Block文件,文件選擇Generate the Output Products,是文件得到一定的約束。

Setp2:彈出如下對話框,直接點擊Generate

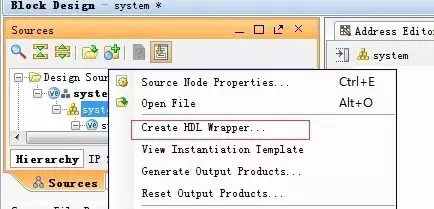

Setp3:繼續右鍵單擊Block文件,選擇Create a HDL wrapper,根據Block文件內容產生一個HDL 的頂層文件:

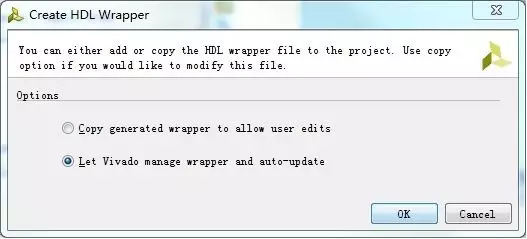

Setp4:并選擇讓vivado自動完成

Setp5:這里我們看到,Vivado給我創建了這樣的頂層文件,其中的gpio_0_tri_io就是我們配置的EMIO

EMIO的管腳約束修改

我們發現,之前引出的EMIO叫做GPIO_0,到了頂層他的名字gpio_0_tri_io,而不是GPIO_0。所以分配引腳的時候就要注意了名字別錯了,創建一個約束文件,分配引腳如下:

產生bit文件

此時可以,開始生成bit文件了:

導出bit文件

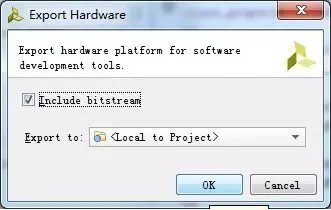

編譯成功之后,依然是導出硬件:

加載到SDK

通過4個GPIO口輸出高低電平到引出的引腳上。

配置GPIO的步驟如下:

通過GPIO的外設ID找到對應的外設信息;

填充GPIO外設寄存器基地址和一些相關信息;

配置GPIO口的方向為輸出方向;

配置GPIO口的輸出使能;

設置GPIO口輸出高低電平;

打開SDK,然后新建一個工程,以及添加一個main.C文件。

添加程序如下:

編輯:hfy

-

寄存器

+關注

關注

31文章

5426瀏覽量

123687 -

GPIO

+關注

關注

16文章

1278瀏覽量

53697 -

Zynq

+關注

關注

10文章

614瀏覽量

48082 -

SDK

+關注

關注

3文章

1068瀏覽量

47843

發布評論請先 登錄

基于小凌派RK2206開發板:OpenHarmony如何使用IoT接口控制GPIO中斷

基于瑞芯微RK3562 四核 ARM Cortex-A53 + 單核 ARM Cortex-M0工業評估板——NPU開發案列

基于小凌派RK2206開發板:OpenHarmony如何使用IoT接口控制GPIO外設

為什么GPIO配置總是出問題?

GPIO內部電路的原理

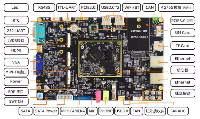

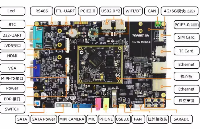

正點原子ZYNQ7015開發板!ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2,性能強悍,資料豐富!

【GD32 MCU入門教程】GD32 MCU GPIO 結構與使用注意事項

ZYNQ開發案例:GPIO的結構體系及使用案例

ZYNQ開發案例:GPIO的結構體系及使用案例

評論