來源:電子技術(shù)應(yīng)用ChinaAET

針對高速運動平臺彈速補償?shù)膶崟r性要求,在基于距離徙動校正(Range Cell Migration Compensation,RCMC) 的思想上提出了一種彈速補償?shù)?a href="http://m.xsypw.cn/soft/data/30-91/" target="_blank">FPGA實現(xiàn)方法。將距離徙動校正的思想用于彈速補償,提高了相參積累后的信噪比,并在FPGA中完成硬件實現(xiàn),仿真實驗表明使用FPGA實現(xiàn)彈速補償方法具有實時性高、處理速度快、精度高等有優(yōu)點。

高速飛行器具有重要的戰(zhàn)略意義和極高的應(yīng)用價值,其具有全球攻擊、機動作戰(zhàn)等特點,特別是在遠(yuǎn)程打擊、快速突防、電子壓制、對地偵察和預(yù)警等方面極具發(fā)展?jié)摿1]。目標(biāo)檢測性能優(yōu)劣是實現(xiàn)高速運動飛行器對目標(biāo)精確打擊的關(guān)鍵。對于高速運動飛行器而言,雷達導(dǎo)引頭接收到的各脈沖回波間,由于平臺速度引入了不可忽略的距離走動,嚴(yán)重降低相干積累后的檢測前信噪比,從而直接影響整個雷達導(dǎo)引頭的探測性能,因此必須對彈速產(chǎn)生的距離徙動進行補償。

近年來,現(xiàn)場可編程邏輯門陣列(Field Programmable Gate Array,F(xiàn)PGA)技術(shù)飛速發(fā)展,集成度越來越高,功耗、成本不斷降低,特別是在并行處理、流水線設(shè)計、可重構(gòu)等方面具有獨一無二的優(yōu)勢,使其逐漸在雷達信號處理領(lǐng)域中占據(jù)重要地位。本文使用FPGA對距離徙動校正算法進行了硬件實現(xiàn),具有實時性高,處理速度快,精度高等特點[2-3]。

1 RCMC算法

彈載雷達彈速補償方法采用了RCMC的思想,本節(jié)將從信號模型的角度對RCMC原理簡要地闡述[4]。

假設(shè)一彈載雷達發(fā)射一串載頻為f0,帶寬為B,脈沖持續(xù)時間為Tp的線性調(diào)頻信號,發(fā)射的脈沖串信號可表示為:

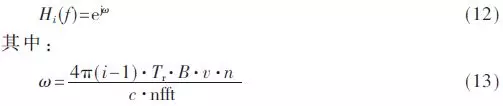

距離徙動校正(RCMC)是通過補償各次脈沖的時間延遲Δti,使得第i(i=2,3,…,N)個脈壓輸出時域信號峰值位置按第一個脈沖對齊。第i次脈沖的RCMC補償因子的頻域形式可表示為:

綜上,只需對距離壓縮后的回波信號在頻域乘以一個距離徙動校正因子Hi(f),就可以去掉距離走動效應(yīng)。所以彈速補償?shù)膶崿F(xiàn)方法的核心問題就是讓硬件來運算式(11)。

2 算法的FPGA實現(xiàn)

由于FPGA在并行處理、流水線設(shè)計、可重構(gòu)等方面的優(yōu)勢,使其相對于DSP等處理器更適合來運算式(11)。具體的實現(xiàn)方法按流程上可分為三步來做,第一步是將時域信號變?yōu)轭l域信號;第二步在頻域下乘以Hi(f);第三步將運算結(jié)果逆變?yōu)闀r域信號。顯然,第一步和第三步使用FFT和IFFT即可實現(xiàn),并且FFT和IFFT算法的FPGA實現(xiàn)已很成熟,所以實現(xiàn)方法的核心問題就是實現(xiàn)第二步。

在做RCMC之前首先要在FPGA內(nèi)做數(shù)字下變頻和脈沖壓縮,由于距離徙動校正和脈壓有緊密的互聯(lián)結(jié)構(gòu),在硬件設(shè)計中,特別是同步設(shè)計上,往往要將這兩者綜合考慮,所以本設(shè)計中將脈壓和距離徙動校正封裝在一個模塊內(nèi)。

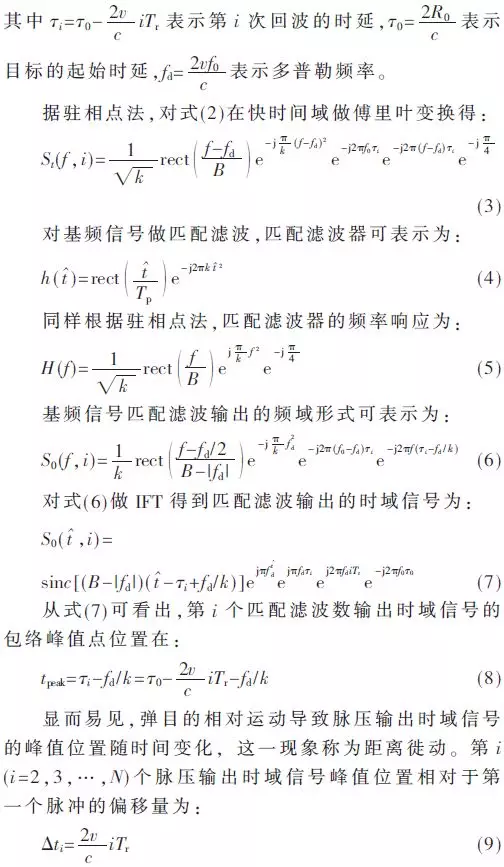

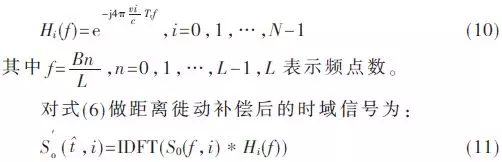

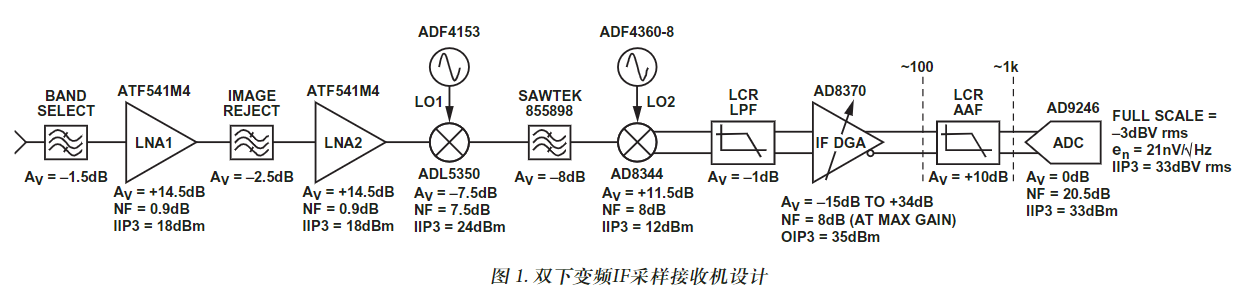

接下來按照功能來介紹,先對脈沖壓縮進行簡要介紹,再對距離徙動校正作詳細(xì)介紹。圖1為距離徙動校正模塊的系統(tǒng)框圖。RCMC模塊的頂層的輸入輸出很簡潔,輸入輸出端口與式(11)、式(16)中的參數(shù)的映射關(guān)系如表1所示。

2.1 脈沖壓縮的FPGA實現(xiàn)

脈沖壓縮在時域下是回波信號與匹配濾波器的沖擊響應(yīng)的卷積,而在頻域下為乘積運算,便于硬件實現(xiàn)。所以本設(shè)計中采用頻域下相乘的方法來實現(xiàn)時序脈沖壓縮。

將輸入的兩路正交回波信號DIN_RE和DIN_IM進行FFT運算,XILINX提供了免費的FFT IP核,所以這里直接在FPGA工程中調(diào)用一個FFT IP。將DVIN與FFT的start引腳連接,將輸入數(shù)據(jù)DIN_RE、DIN_IM與FFT的xn_re,xn_im連接。然后將經(jīng)過FFT運算后的兩路頻域數(shù)據(jù)與量化后的匹配濾波系數(shù)復(fù)乘。匹配濾波系數(shù)由MATLAB生成導(dǎo)入FPGA的ROM內(nèi)。如圖1所示,ROM的使能引腳與FFT的輸出有效引腳dv連接,ROM使能之后地址累加1開始輸出系數(shù),與FFT輸出的數(shù)據(jù)作同步處理之后輸入給復(fù)數(shù)乘法器,若不作距離徙動校正將復(fù)數(shù)乘法器的結(jié)果進行逆FFT運算之后便完成了脈沖壓縮。

2.2 距離徙動校正的FPGA實現(xiàn)

由式(10),可令:

其中,i為脈沖序列數(shù),初始值為1;Tr為慢時間域下的脈沖重復(fù)周期(單位:s);v為導(dǎo)彈速度(單位:m/s);c為光速(單位:m/s);f為單一頻點的頻率(單位:Hz);B為脈沖寬度(單位:Hz),這里取40 MHz;nfft為FFT的字長,這里取16 384;n為量化后的序列數(shù),初始值為0。

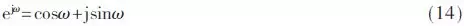

對于FPGA來說,它無法直接計算ejω,而根據(jù)歐拉公式可得:

所以為便于FPGA實現(xiàn)可以通過正余弦函數(shù)來計算ejω。正余弦函數(shù)本文采用查表法的方式來實現(xiàn),首先由MATLAB生成兩組數(shù)據(jù),數(shù)據(jù)值為round(G·cos(k))和round(G·sin(k)),G=8 192,k的取值范圍為1:1:1024。G與k的取值與精度要求有關(guān)。將生成的這兩組數(shù)據(jù)分別存在兩個coe文件中。在FPGA工程中調(diào)用兩個ROM,將存儲深度定為1 024,位寬定為15,將MATLAB生成的兩個coe文件導(dǎo)入ROM。如圖1所示,再將ROM的使能與FFT IP核的dv引腳連接,通過計算ROM的地址即可計算得出的ejω的數(shù)值。具體計算方法如下。

式中,addr為ROM的地址,ROM的存儲深度為1 024,所以sin與cos函數(shù)每1 024個數(shù)據(jù)為一個周期,所以要計算得出cosω與sinω,只要通過乘法器計算出addr,再將addr對1 024取余,即截取addr的低10位,然后接入兩個ROM的地址總線引腳,接著把兩個ROM輸出的數(shù)據(jù)除以8 192,即截掉低15位,得到cosω與sinω的計算結(jié)果。

對式(15)的參數(shù)進行整理,將B、c、nfft等常數(shù)合并為系數(shù)coe,并取整得:

如圖1所示,將兩個正余弦ROM的輸出與脈壓之后頻域下的數(shù)據(jù)作復(fù)乘(數(shù)據(jù)同步之后輸入復(fù)數(shù)乘法器)即可完成ejω的運算,最后再對復(fù)乘結(jié)果進行逆FFT運算(IFFT IP核的設(shè)置與上文的FFT IP核的設(shè)置相同),即可得到脈壓和距離徙動校正之后的數(shù)據(jù)。

3 仿真結(jié)果

本節(jié)將通過測試和仿真等手段來驗證本方法的正確性和硬件系統(tǒng)的性能。

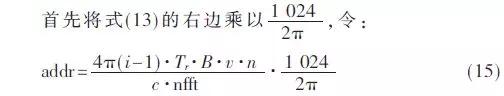

3.1 測試數(shù)據(jù)

為驗證本方法的正確性和可行性,將一組(10個脈沖)下變頻之后的回波數(shù)據(jù)輸入FPGA進行運算,在復(fù)數(shù)乘法器1的輸出口和整個系統(tǒng)的輸出口設(shè)了兩個測試點,將這兩個測試點的數(shù)據(jù)保存至txt文件,導(dǎo)入MATLAB,與直接用MATLAB作距離徙動校正后的數(shù)據(jù)進行對比。

輸入的初始回波數(shù)據(jù)如圖2所示。

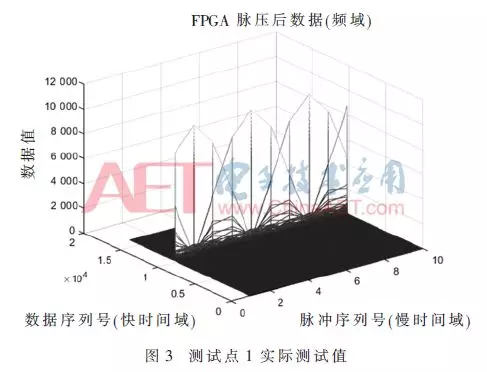

第一個測試點數(shù)據(jù)作折線圖,如圖3所示。MATLAB的仿真結(jié)果如圖4所示。

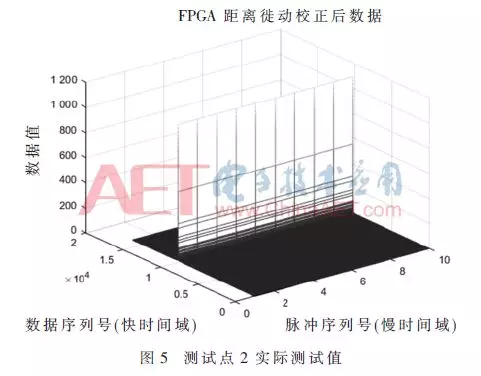

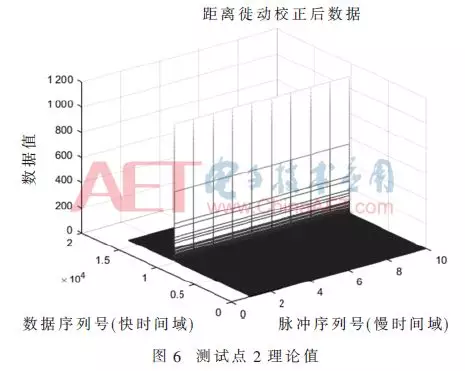

第二個測試點數(shù)據(jù)作折線圖,如圖5所示。MATLAB的仿真結(jié)果如圖6所示。

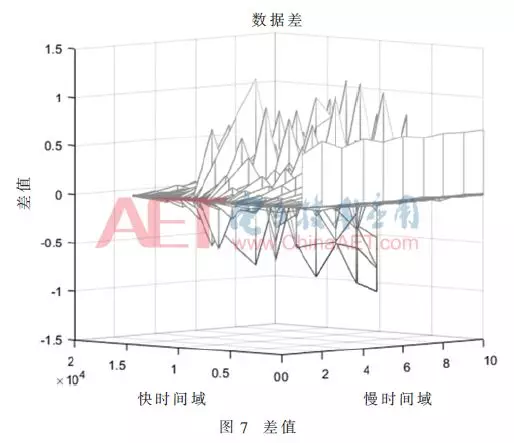

由上面兩圖可以看出FPGA運行結(jié)果與MATLAB仿真結(jié)果非常一致,將測試點2的兩個數(shù)據(jù)做差可以看出誤差,如圖7所示,可以估算出最大誤差為1.5/1 100=0.14%。

3.2 仿真波形

圖8是MODELSIM仿真波形,以一個脈沖數(shù)據(jù)為例,可以看出,從第一個回波數(shù)據(jù)輸入到系統(tǒng)處理結(jié)束后最后一個數(shù)據(jù)輸出,整個系統(tǒng)的處理時間為493.355 μs,扣除數(shù)據(jù)傳輸時間16 384×5 ns=81.92 μs,系統(tǒng)處理時間為411.435 μs。

在FFT處理出第一個數(shù)據(jù)的瞬間,使能信號就會傳遞給ROM_MATCH和乘法器模塊,這些模塊便開始進行運算,并且FFT每輸出一個數(shù)據(jù),這些模塊便計算一次,當(dāng)16 384個數(shù)據(jù)全部FFT運算結(jié)束,其他模塊也幾乎同時運算結(jié)束,數(shù)據(jù)從FFT輸出到復(fù)數(shù)乘法器輸出結(jié)果延時時間小于20個時鐘周期,本系統(tǒng)的主時鐘頻率為200 MHz,所以延時時間小于100 ns,很好地體現(xiàn)了FPGA并行處理和流水線運算的優(yōu)勢,總延時493 ?滋s絕大部分都消耗在了FFT和IFFT運算以及數(shù)據(jù)傳輸時間上。

4 結(jié)論

將距離徙動校正的思想用于彈速補償,提高了相參積累后的信噪比,使用FPGA實現(xiàn)距離徙動校正算法具有實時性高、處理速度快、精度高等特點,為雷達導(dǎo)引頭提供了很好的軟硬件支持,提高了雷達導(dǎo)引頭的探測性能。

參考文獻

[1] 尚煒.某相參末制導(dǎo)雷達信號處理機的理論分析及實現(xiàn)[D].西安:西安電子科技大學(xué),2009.

[2] 宋萬均,張安堂.雙基地雷達目標(biāo)速度計算的FPGA實現(xiàn)[J].電子技術(shù)應(yīng)用,2014(1).47-49.

[3] 王龍,楊承志,吳宏超,等.基于FPGA的數(shù)字基帶多模雷達信號源設(shè)計[J].電子技術(shù)應(yīng)用,2016(8):87-90.

[4] CUMMING I G,WONG F H.合成孔徑雷達成像算法與實現(xiàn)[M].洪文,等,譯.北京:電子工業(yè)出版,2012.

-

FPGA

+關(guān)注

關(guān)注

1645文章

22049瀏覽量

618371

發(fā)布評論請先 登錄

技術(shù)干貨 | DAC頻率響應(yīng)特性解析:從sinc函數(shù)衰減到補償技術(shù)

一種環(huán)保型紅色發(fā)煙彈主裝藥配方設(shè)計與優(yōu)化

掃描電機的PID恒速控制仿真及實驗

FPGA芯片的概念和結(jié)構(gòu)

PWM脈寬調(diào)制實現(xiàn)電機的恒速驅(qū)動

OptiSystem-系統(tǒng)角度下分析色散補償方案

AN-851: 一種WiMax雙下變頻IF采樣接收機設(shè)計方案

介紹一種 WiMax 雙下變頻 IF 采樣接收機設(shè)計方案

一種實現(xiàn)寬電壓增益的改進型LLC-AHB變換器

PLC遠(yuǎn)程監(jiān)控物聯(lián)網(wǎng)方案解析

一種彈速補償?shù)腇PGA實現(xiàn)方案解析

一種彈速補償?shù)腇PGA實現(xiàn)方案解析

評論