來(lái)源:納芯微電子

摘要

BMS系統(tǒng)的工作電壓普遍大于人體所能承受的安全電壓,若絕緣性能下降將導(dǎo)致漏電流增大,對(duì)人身安全造成威脅。

本文中介紹的絕緣監(jiān)測(cè)電路使用固態(tài)繼電器NSI7258通過(guò)電池正母線對(duì)地、負(fù)母線對(duì)地絕緣電阻的計(jì)算和監(jiān)測(cè)來(lái)判斷絕緣性能,實(shí)現(xiàn)高精度和高可靠性的絕緣監(jiān)測(cè)。

1. 方案原理

1.1 絕緣監(jiān)測(cè)實(shí)現(xiàn)原理

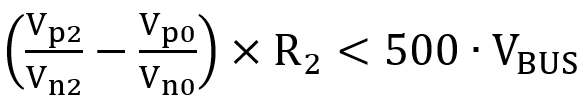

根據(jù)GB 18384《電動(dòng)汽車(chē)安全要求》要求,在最大工作電壓下,絕緣電阻需要大于500Ω/V。因此對(duì)于母線電壓為VBUS的系統(tǒng),絕緣電阻均需要滿足大于 500·VBUS以保障人身安全。當(dāng)絕緣電阻劣化,絕緣監(jiān)測(cè)電路應(yīng)快速識(shí)別并發(fā)出報(bào)警。

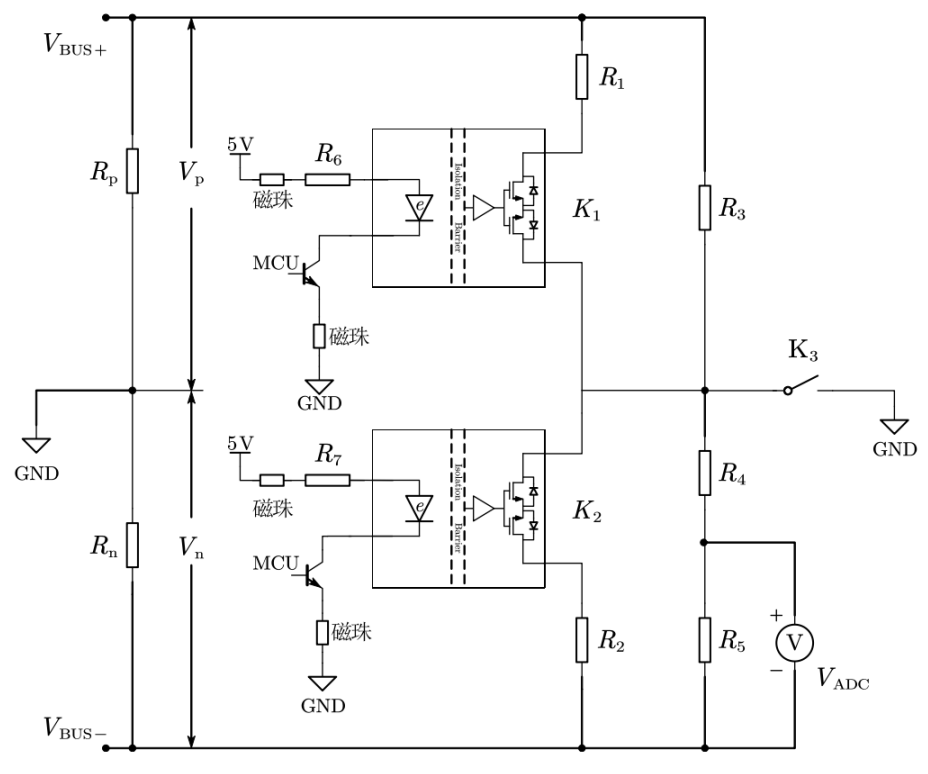

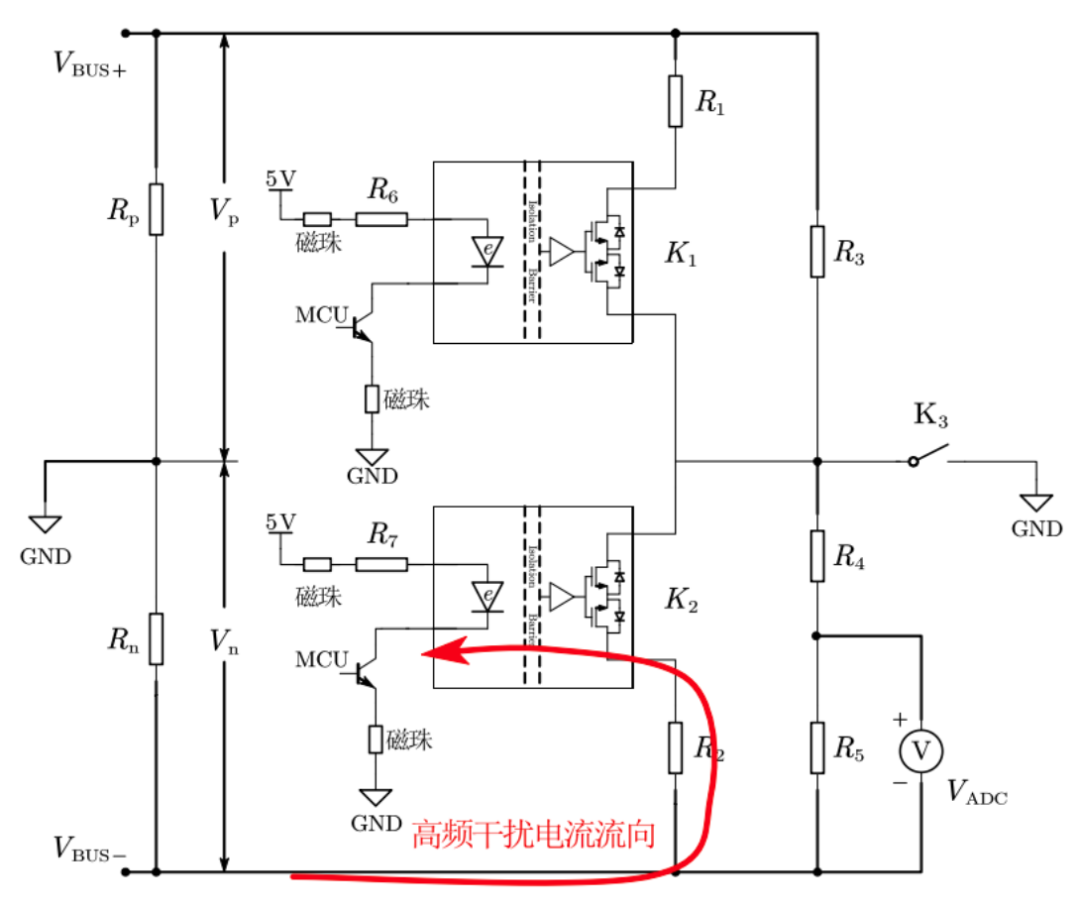

圖1.1 絕緣監(jiān)測(cè)電路推薦應(yīng)用電路

絕緣監(jiān)測(cè)電路推薦應(yīng)用電路如圖1.1所示,K1及K2為納芯微固態(tài)繼電器(Solid-State Relay, SSR)產(chǎn)品在絕緣監(jiān)測(cè)電路中的主要應(yīng)用位置,芯片采用低壓側(cè)控制,即芯片低壓側(cè)參考地為車(chē)身地。該應(yīng)用電路每隔2-3秒,通過(guò)K1、K2開(kāi)關(guān)來(lái)進(jìn)行一次絕緣監(jiān)測(cè)電路Rp、Rn的阻值測(cè)量,通過(guò)開(kāi)關(guān)K3實(shí)現(xiàn)絕緣監(jiān)測(cè)電路是否工作的控制。絕緣監(jiān)測(cè)過(guò)程中,K3處于常閉狀態(tài)。

定義母線電壓為VBUS,直流正母線到車(chē)身地的電壓為Vp,車(chē)身地到直流負(fù)母線的電壓為Vn。

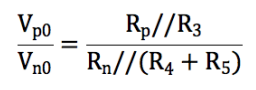

當(dāng)K1斷開(kāi),K2斷開(kāi),此時(shí)R5上電壓為V0,則Vn0= V0*(R4+R5)/R5,Vp0=VBUS-Vn0,可得計(jì)算公式(1):

當(dāng)K1閉合,K2斷開(kāi),此時(shí)R5上電壓為V1,則Vn1= V1*(R4+R5)/R5,Vp1=VBUS-Vn1,可得計(jì)算公式(2):

由計(jì)算公式(1)和計(jì)算公式(2)可得計(jì)算公式(3):

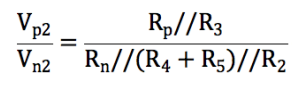

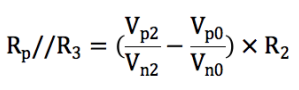

當(dāng)K1斷開(kāi),K2閉合,此時(shí)R5上電壓為V2,則Vn2= V2*(R4+R5)/R5,Vp2=VBUS-Vn2,可得計(jì)算公式(4):

由計(jì)算公式(1)和計(jì)算公式(4)可得計(jì)算公式(5):

公式(3)和公式(5)是絕緣電阻計(jì)算的結(jié)果。

2. 器件選型

2.1 電阻選型

· 2.1.1 電阻選型考量

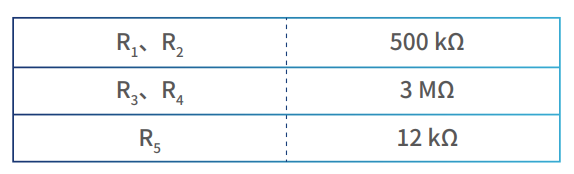

通常,電路設(shè)計(jì)上,令R1=R2<R3=R4,并存在如下設(shè)計(jì)考量:

對(duì)ADC輸入電壓的考量:R5上的電壓需要一直小于ADC的最大輸入電壓,最大值接近ADC的最大輸入電壓,以保證ADC的輸出精度。所以R5/(R4+R5)*VBUS需要接近ADC的最大輸入電壓,以此得到R5、R4的比例。

對(duì)ADC內(nèi)阻的考量:R5作為ADC采樣的輸入口,其阻值需要小于ADC的內(nèi)阻(如

對(duì)絕緣阻抗影響的考量:K1和K2開(kāi)關(guān)過(guò)程中,監(jiān)測(cè)電路中的R1和R2分別并聯(lián)在Rp和Rn上,如果R1、R2過(guò)小,將導(dǎo)致實(shí)際上的絕緣電阻Rp//R1和Rn//R2大幅降低。

對(duì)識(shí)別精度的考量:結(jié)合公式(4),當(dāng)Rp//R3劣化達(dá)到小于臨界值500·VBUS后,當(dāng):

MCU識(shí)別到絕緣電阻劣化并報(bào)警,因此需要較小的R2,以便Vp2和Vn2在數(shù)值上有足夠的差異來(lái)抵消ADC精度誤差。

對(duì)Settle time的考量:在實(shí)際系統(tǒng)中,部分客戶車(chē)身地和電池地中間并聯(lián)Y電容(即與Rn并聯(lián)),存在RC充放電過(guò)程,R1、R2需要小一些以便于減少settle time。如R1、R2取得過(guò)小,將導(dǎo)致K1、K2閉合時(shí)的并聯(lián)等效阻抗Rp//R3//R1、Rn//(R4+R5)//R2偏小,也對(duì)人身安全造成威脅。

· 2.1.2400V/800V系統(tǒng)推薦電阻值

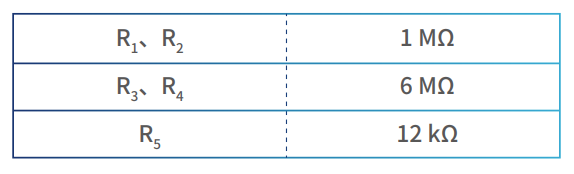

基于上述分析,可以基于下表設(shè)計(jì)絕緣監(jiān)測(cè)電路分壓電阻。

表2.1 400V系統(tǒng)推薦電阻選型

表2.2 800V系統(tǒng)推薦電阻選型

2.2 繼電器選型

· 2.2.1 繼電器漏電流對(duì)監(jiān)測(cè)精度影響

絕緣電阻劣化到小于500·VBUS時(shí)系統(tǒng)監(jiān)測(cè)到此現(xiàn)象應(yīng)報(bào)警。以VBUS=800V的系統(tǒng)為例,按標(biāo)準(zhǔn)要求絕緣電阻應(yīng)大于400kΩ,若K1、K2上漏電流小于1μA,其等效阻抗大于800MΩ,遠(yuǎn)大于絕緣電阻Rp、Rn,對(duì)于400kΩ測(cè)量帶來(lái)的誤差小于0.05%。若K1、K2上漏電流為10μA,其等效阻抗等于400 MΩ,測(cè)量誤差約為0.5%。

因此,漏電流越大,對(duì)于測(cè)量精度的影響越大。選用漏電流小(<1μA)的納芯微SSR產(chǎn)品來(lái)實(shí)現(xiàn)K1、K2的開(kāi)通、關(guān)斷功能將有益于提升測(cè)量精度,避免誤報(bào)警。

· 2.2.2 繼電器可靠性對(duì)系統(tǒng)可靠性的影響

傳統(tǒng)機(jī)械繼電器開(kāi)關(guān)壽命受限,一旦到達(dá)最大開(kāi)關(guān)次數(shù),系統(tǒng)絕緣監(jiān)測(cè)功能失效,人身安全隱患突出。因此機(jī)械繼電器已經(jīng)基本退出此應(yīng)用場(chǎng)景。

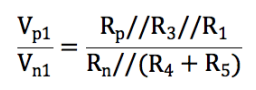

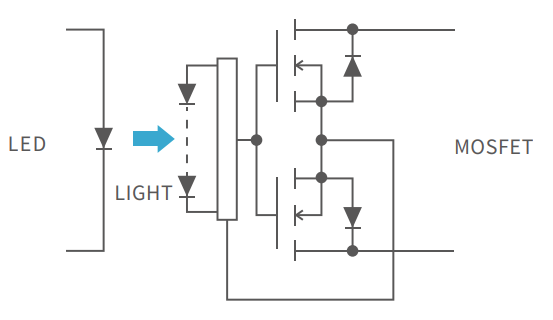

傳統(tǒng)PhotoMOS目前使用較多。PhotoMOS在控制側(cè)發(fā)光二極管(LED)通電流后,光敏二極管接收到光的照射,由光電效應(yīng)產(chǎn)生電流從而控制高壓側(cè)MOS導(dǎo)通。

圖3.1 PhotoMOS原理

LED經(jīng)過(guò)長(zhǎng)時(shí)間使用后,發(fā)光強(qiáng)度將會(huì)降低。主流光耦供應(yīng)商對(duì)于PhotoMOS產(chǎn)品使用壽命進(jìn)行了預(yù)測(cè),1000小時(shí)后閾值電流就會(huì)升高10%,11年后閾值電流需要提高5倍以上。若按照數(shù)據(jù)手冊(cè)中的閾值電流進(jìn)行設(shè)計(jì),光敏二極管接收到的能量不足,將導(dǎo)致誤碼失效。改善的方法只能是設(shè)計(jì)較大的輸入電流來(lái)解決光衰問(wèn)題。但是另一方面,更大電流帶來(lái)更高的溫度,高溫將導(dǎo)致發(fā)光二極管將電信號(hào)轉(zhuǎn)化為光信號(hào)和光敏二極管將光信號(hào)轉(zhuǎn)化為電信號(hào)的效率降低,同時(shí),由于高溫壽命問(wèn)題,PhotoMOS一般限制在最大85°C環(huán)境溫度下。多種因素使得光耦產(chǎn)品可靠性受到極大的挑戰(zhàn)。

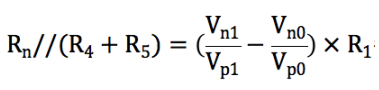

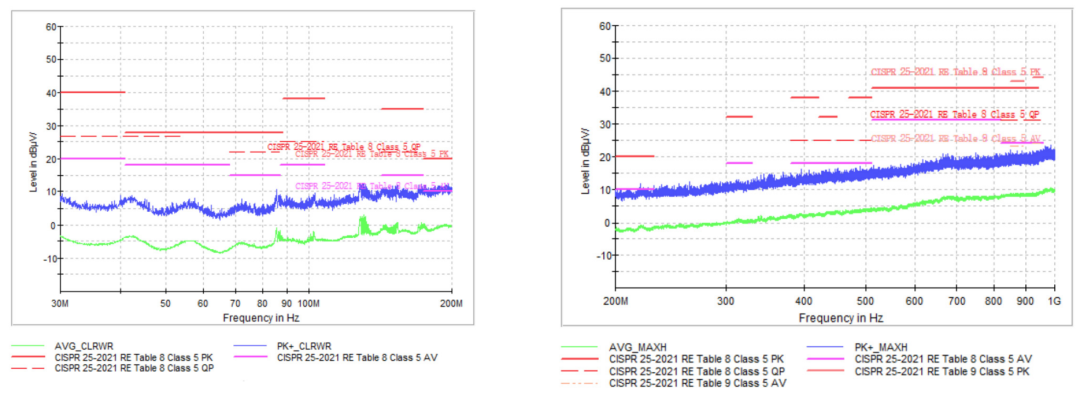

采用容隔或者磁隔的固態(tài)繼電器來(lái)替代類(lèi)似光耦的PhotoMOS,可以極大提高系統(tǒng)的可靠性。納芯微開(kāi)發(fā)的NSI7258固態(tài)繼電器是一款通過(guò)EMI CISPR25 CLASS 5標(biāo)準(zhǔn),同時(shí)采用高可靠電容隔離技術(shù)的產(chǎn)品,將強(qiáng)大的技術(shù)創(chuàng)新能力與車(chē)規(guī)高可靠性的質(zhì)量管理體系結(jié)合,為絕緣監(jiān)測(cè)系統(tǒng)提供高性能,高可靠性的解決方案。

圖3.2 NSI7258 EMI測(cè)試結(jié)果

3. 絕緣監(jiān)測(cè)應(yīng)用中的EMS注意項(xiàng)及推薦解決方案

3.1 絕緣監(jiān)測(cè)應(yīng)用潛在EMS問(wèn)題

在新能源汽車(chē)中,電子組件的可靠性對(duì)車(chē)輛的整車(chē)性能起著至關(guān)重要的作用。特別是在面對(duì)惡劣電磁干擾環(huán)境下,確保車(chē)輛集成的各單元能夠正常運(yùn)作,符合電磁兼容性標(biāo)準(zhǔn),成為了一個(gè)關(guān)鍵問(wèn)題。

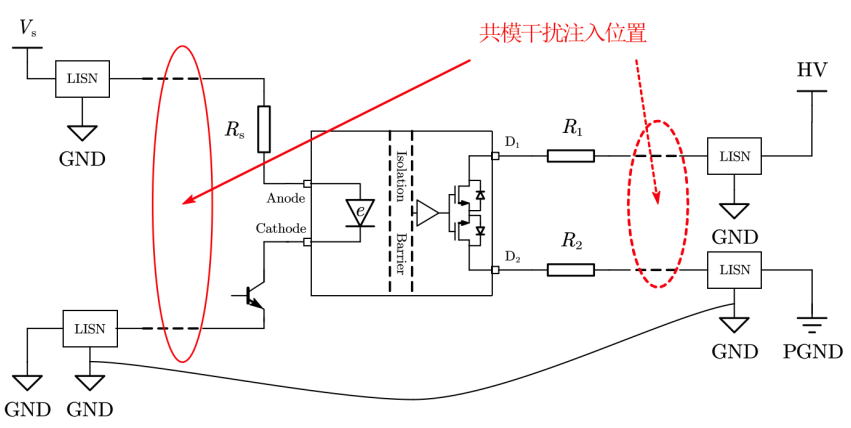

諸如輻射抗擾(RI)、大電流注入(BCI)、手持發(fā)射機(jī)抗擾(PTI)等部分EMS測(cè)試,可等效為在芯片的高、低壓側(cè)兩端加一高頻電流源,如圖4.1所示。盡管電路板上及空間中存在寄生電容高頻電流泄放路徑,但仍然會(huì)有部分電流直接注入芯片內(nèi)部。在電流頻率較高時(shí)(約幾百M(fèi)Hz),隔離電容呈現(xiàn)阻抗相對(duì)較低,成為潛在電流通路,且當(dāng)電路上無(wú)其他高頻電流泄放路徑設(shè)計(jì)時(shí),電流將穿過(guò)隔離電容,經(jīng)由芯片高壓側(cè)回流至低壓側(cè),形成電流環(huán)路,將可能干擾芯片正常工作。

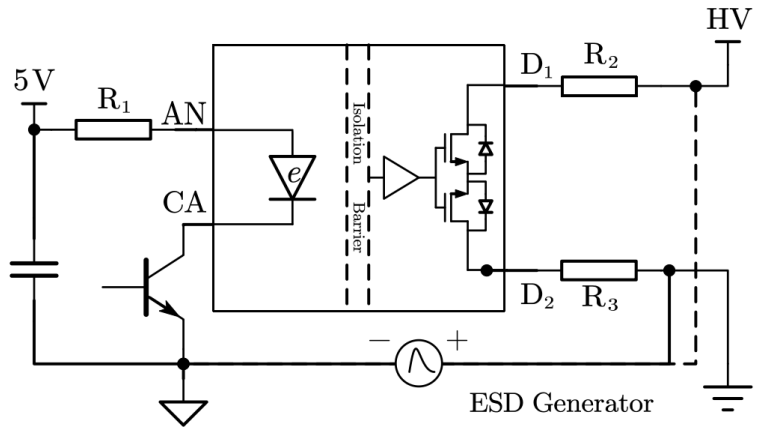

圖4.1 部分EMS測(cè)試等效模型

BMS系統(tǒng)產(chǎn)品在設(shè)計(jì)驗(yàn)證環(huán)節(jié)中,需要對(duì)進(jìn)行系統(tǒng)ESD測(cè)試,其中下電模式,用以模擬產(chǎn)品在制造、組裝、測(cè)試、存放及搬運(yùn)等過(guò)程中,因人為接觸所導(dǎo)致人體積累的靜電的泄放過(guò)程,評(píng)估產(chǎn)品抵抗靜電放電破壞能力。

在該測(cè)試中,需要將ESD槍的地接至設(shè)備機(jī)殼地,放電點(diǎn)為暴露在表面的零部件(機(jī)殼、螺絲等)及人能直接接觸到的接插件的每個(gè)Pin腳,且通常需要通過(guò)±8kV測(cè)試需求。由于固態(tài)繼電器產(chǎn)品跨接在BMS系統(tǒng)高壓域與低壓域間,若芯片位置設(shè)計(jì)不合理,±8kV的ESD電壓將直接施加在芯片隔離帶兩側(cè),且無(wú)其他ESD電流泄放路徑。測(cè)試等效模型如圖4.2所示。

圖4.2 系統(tǒng)ESD測(cè)試等效模型

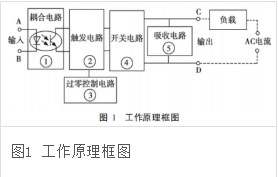

為避免上述電磁兼容問(wèn)題影響或損壞芯片,可根據(jù)如下推薦原理圖及布局設(shè)計(jì)電路。

3.2 推薦應(yīng)用電路分析

如圖2.1,在絕緣監(jiān)測(cè)應(yīng)用電路中,推薦將SSR放至電橋中點(diǎn)兩側(cè),經(jīng)過(guò)大分壓電阻R1、R2后再與高壓母線VBUS+及VBUS-連接。以K1為例,由于K1的D1、D2引腳至高壓母線及線路上均存在大分壓電阻,使得高頻干擾電流難以灌入SSR芯片,同時(shí)K3導(dǎo)通,進(jìn)一步提供了高頻干擾電流泄放路徑。當(dāng)系統(tǒng)注入干擾時(shí),干擾電流流通路徑為VBUS+→ R1 → K1導(dǎo)通電阻RDSON→ K3導(dǎo)通電阻RDSON→ 車(chē)身地GND,不會(huì)流經(jīng)SSR隔離電容,SSR受干擾誤工作風(fēng)險(xiǎn)低。

同時(shí),推薦在圖中芯片低壓側(cè)串聯(lián)磁珠,用以進(jìn)一步增大芯片低壓側(cè)的線路阻抗,阻礙高頻電流流入芯片。考慮到隔離電容在高頻情況下更容易穿過(guò)電流,推薦使用阻抗在100MHz-400MHz頻段內(nèi)較高的磁珠,可以很好阻礙干擾電流。同時(shí),在系統(tǒng)ESD下電模式測(cè)試中,ESD電壓將施加在VBUS+、VBUS-與車(chē)身地GND之間。對(duì)于K1、K2及K3,由于在ESD路徑上,存在兆歐級(jí)限流電阻,將保護(hù)芯片。

電路的欠佳設(shè)計(jì)如圖4.2所示,與圖2.1不同,K2與R2位置互換,直接與HV-相連,使得K1與K2表現(xiàn)出不同的EMS及ESD性能。由于缺少了分壓大電阻的阻擋,高頻電流將直接通過(guò)D2引腳直接注入K2,同時(shí),由于K2的D1引腳與電橋中點(diǎn)間存在大分壓電阻R2,隔離電容的阻抗相對(duì)更小,干擾電流無(wú)法經(jīng)由K3流至車(chē)身地GND,而是直接經(jīng)過(guò)K2的隔離電容回到車(chē)身地。干擾電流流通路徑為 HV- → K2隔離電容CISO→ 車(chē)身地GND。由于電流流經(jīng)SSR隔離電容,SSR存在受干擾誤工作風(fēng)險(xiǎn)。同時(shí),在系統(tǒng)ESD測(cè)試中,ESD電壓將由K2的隔離電容直接承壓,當(dāng)施加的ESD電壓過(guò)高,將導(dǎo)致芯片損壞。

圖4.3 絕緣監(jiān)測(cè)欠佳設(shè)計(jì)

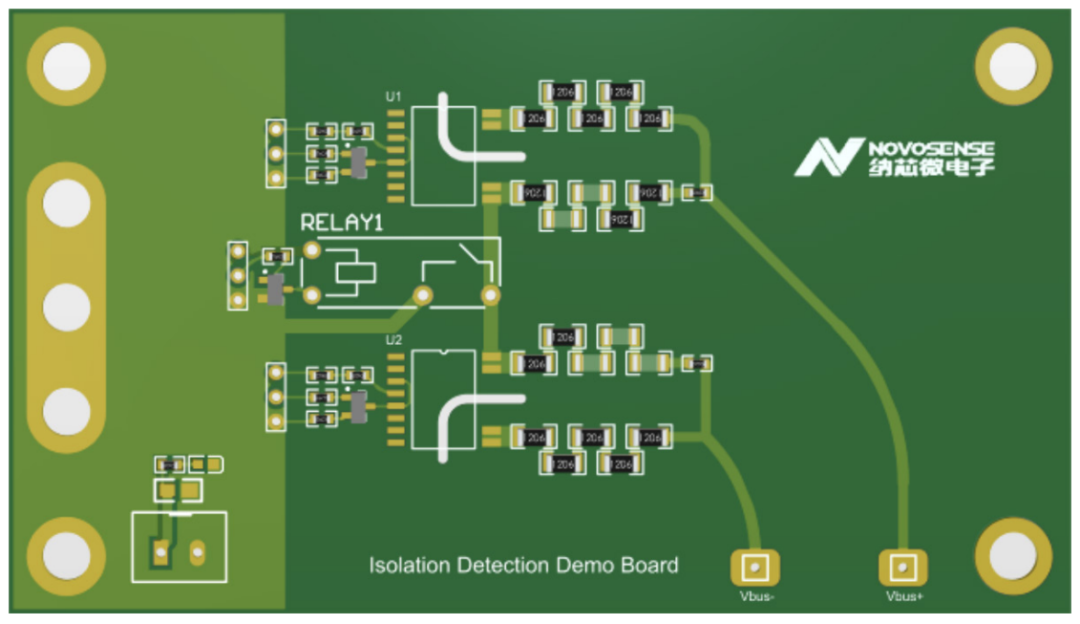

3.3 推薦PCB布局

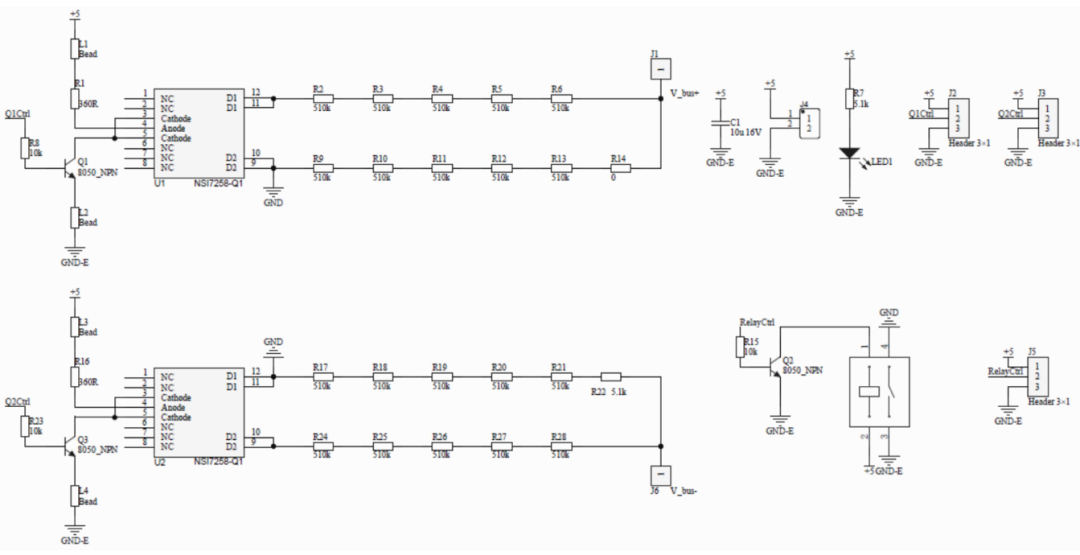

PCB板布局PCB布局對(duì)EMS性能非常重要。根據(jù)4.1節(jié)中的電路優(yōu)化設(shè)計(jì)思路,給出如下PCB電路設(shè)計(jì)參考設(shè)計(jì)。請(qǐng)參閱圖4.4推薦原理圖、圖4.5推薦布局和下面的PCB布局指南:

1. 為符合隔離和安全要求,一次側(cè)和二次側(cè)必須物理隔離。爬電距離和間隙必須符合適用于該應(yīng)用的安全標(biāo)準(zhǔn)。考慮到一般PCB電路板為CTI Ⅲ級(jí),需進(jìn)行開(kāi)槽以保證足夠的爬電。

2. 為保證足夠的抗共模干擾性能,應(yīng)充分注意PCB板上走線,考慮分布寄生電容的影響,避免因同層、跨層走線過(guò)近,產(chǎn)生寄生低阻抗路徑,使干擾電流在芯片高壓側(cè)直接注入芯片D1、D2引腳。同時(shí),在磁珠附近,應(yīng)避免大面積鋪地,避免電流通過(guò)空間電容繞過(guò)磁珠,降低磁珠效果。

經(jīng)實(shí)驗(yàn)驗(yàn)證,該推薦電路可通過(guò)100k-400MHz ISO11452-4 Level 4的BCI測(cè)試及±10kV的系統(tǒng)ESD測(cè)試。

圖4.4 絕緣監(jiān)測(cè)推薦原理圖

圖4.5 絕緣監(jiān)測(cè)推薦布局

納芯微固態(tài)繼電器NSI7258現(xiàn)已量產(chǎn),進(jìn)一步咨詢,請(qǐng)聯(lián)系郵箱:sales@novosns.com。

納芯微電子(簡(jiǎn)稱納芯微,科創(chuàng)板股票代碼688052)是高性能高可靠性模擬及混合信號(hào)芯片公司。自2013年成立以來(lái),公司聚焦傳感器、信號(hào)鏈、電源管理三大方向,為汽車(chē)、工業(yè)、信息通訊及消費(fèi)電子等領(lǐng)域提供豐富的半導(dǎo)體產(chǎn)品及解決方案。

納芯微以『“感知”“驅(qū)動(dòng)”未來(lái),共建綠色、智能、互聯(lián)互通的“芯”世界』為使命,致力于為數(shù)字世界和現(xiàn)實(shí)世界的連接提供芯片級(jí)解決方案。

-

固態(tài)繼電器

+關(guān)注

關(guān)注

8文章

407瀏覽量

39818 -

bms

+關(guān)注

關(guān)注

109文章

1116瀏覽量

67883 -

絕緣監(jiān)測(cè)

+關(guān)注

關(guān)注

1文章

77瀏覽量

10626 -

納芯微

+關(guān)注

關(guān)注

2文章

324瀏覽量

15143

原文標(biāo)題:固態(tài)繼電器NSI7258在高可靠性BMS系統(tǒng)絕緣監(jiān)測(cè)中的應(yīng)用

文章出處:【微信號(hào):米芯微電子,微信公眾號(hào):米芯微電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

固態(tài)繼電器電路疑問(wèn)

固態(tài)繼電器簡(jiǎn)介

固態(tài)繼電器輸出驅(qū)動(dòng)電路

固態(tài)繼電器應(yīng)用研究

固態(tài)繼電器作用

固態(tài)繼電器的接線方法 固態(tài)繼電器的優(yōu)點(diǎn)及缺點(diǎn)

納芯微宣布推出基于電容隔離技術(shù)的全新固態(tài)繼電器產(chǎn)品NSI7258系列

納芯微發(fā)布全新固態(tài)繼電器產(chǎn)品NSI7258系列

固態(tài)繼電器和電磁繼電器的區(qū)別

納芯微推出全新固態(tài)繼電器:支持1700V耐壓, 滿足CISPR25 Class 5要求

納芯微固態(tài)繼電器NSI7258在絕緣監(jiān)測(cè)電路中的應(yīng)用

納芯微固態(tài)繼電器NSI7258在絕緣監(jiān)測(cè)電路中的應(yīng)用

評(píng)論