講解xilinx FPGA 使用mig IP對DDR3的讀寫控制,旨在讓大家更快的學習和應用DDR3。

本實驗和工程基于Digilent的Arty Artix-35T FPGA開發板完成。

軟件使用Vivado 2018.1。

第一篇:DDR3和mig的介紹

1 DDR3介紹

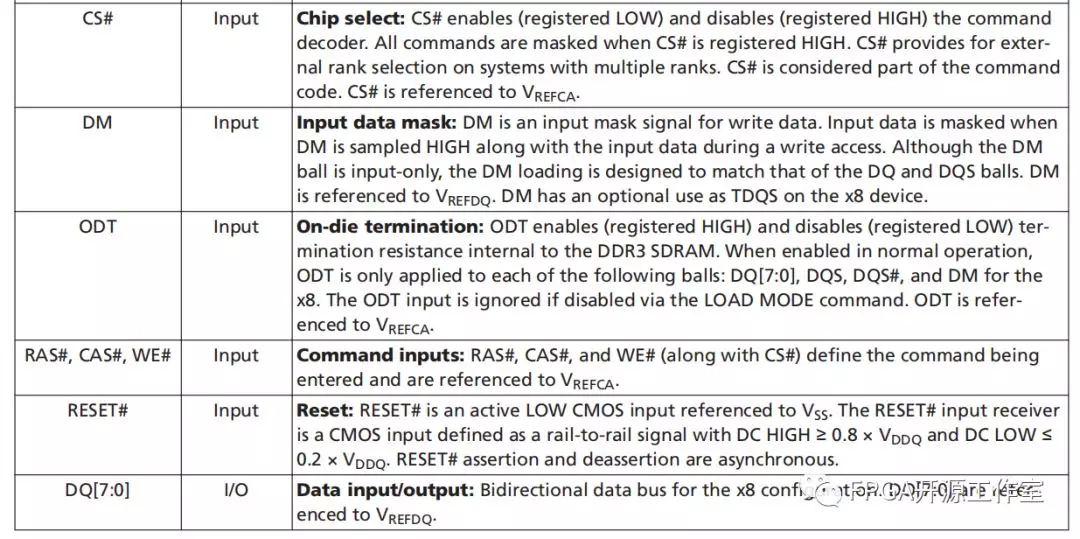

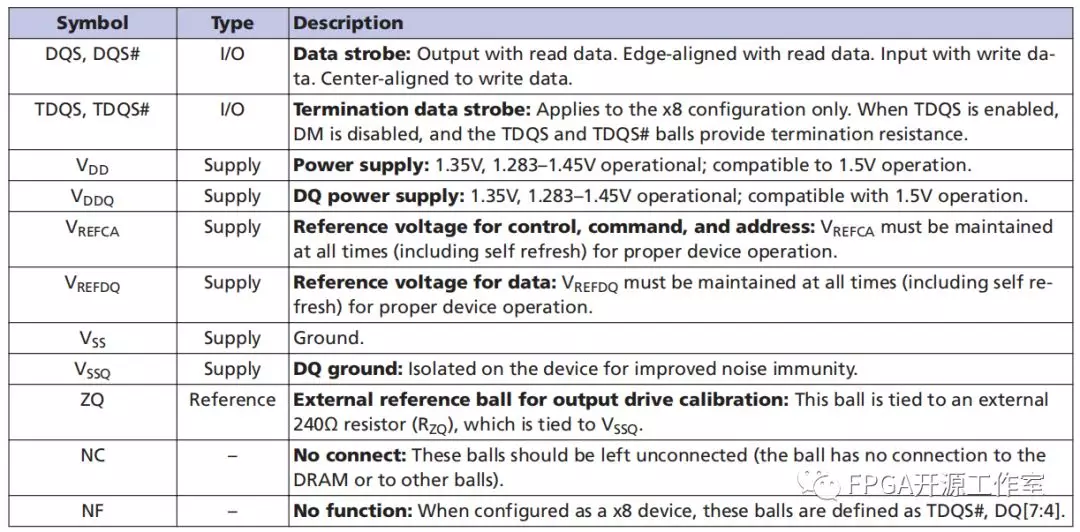

以鎂光的MT41K128M16為例來介紹DDR3。

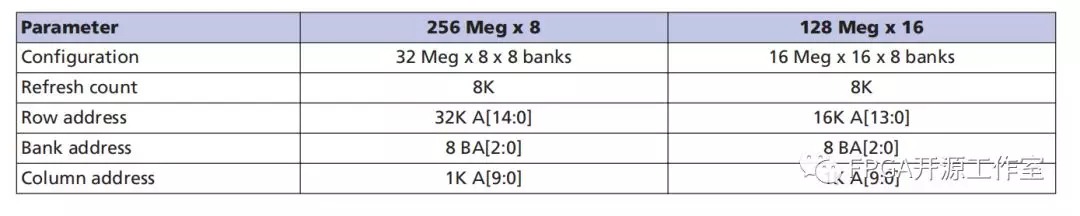

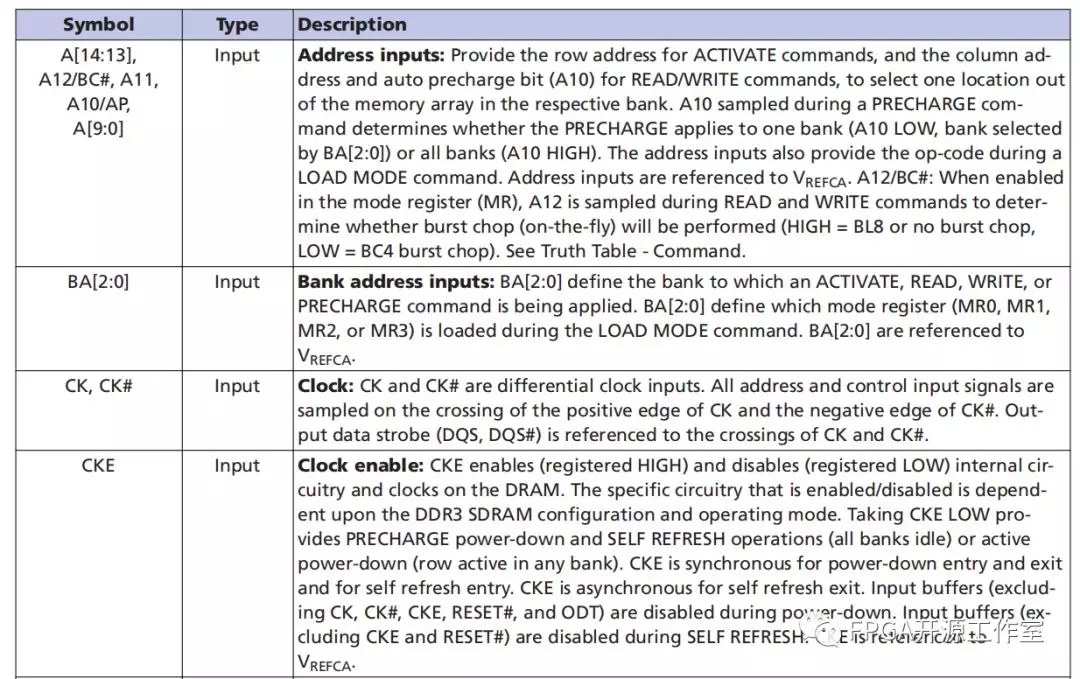

通過以上信息我們即可知道DDR3的內存容量,Row,Column和Bank的地址位寬。開發板選用的MT41K128M16 DDR3的容量為16Megx16x8banks=2048Mb=2Gb。

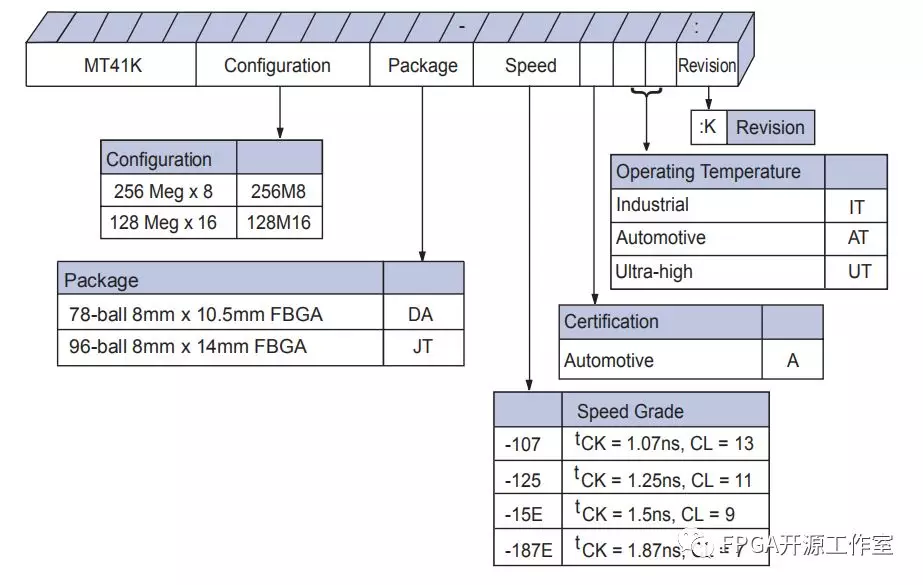

1.1 DDR3命名

我們通過Configuration,Package,Speed...等DDR3的命名可知道DDR3的容量,封裝,速度等級等信息。

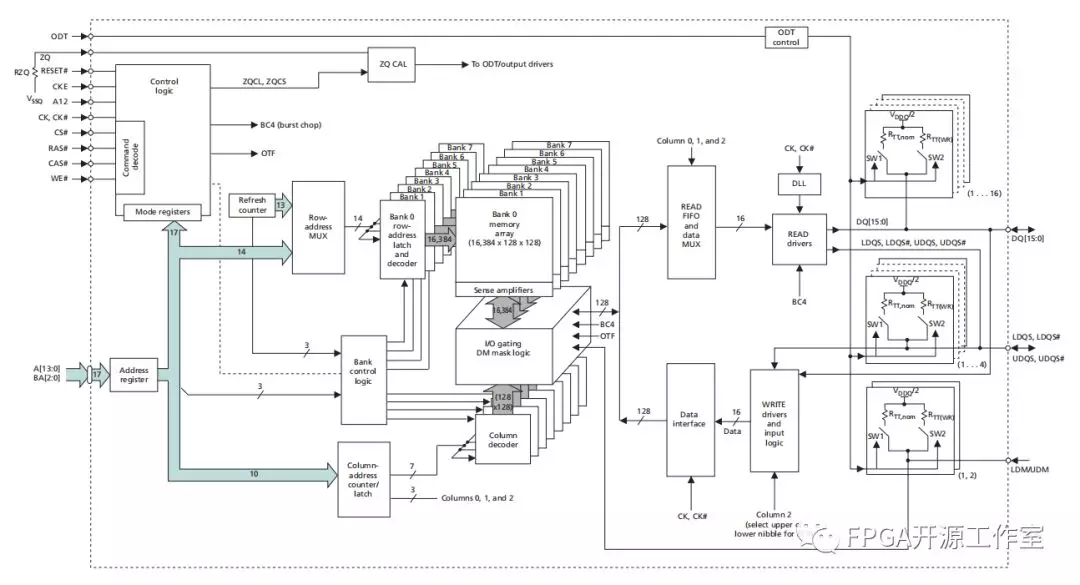

1.2 DDR3的內部結構

使用xilinx mig IP來控制DDR3的數據讀寫我們了解DDR3以上信息即可。

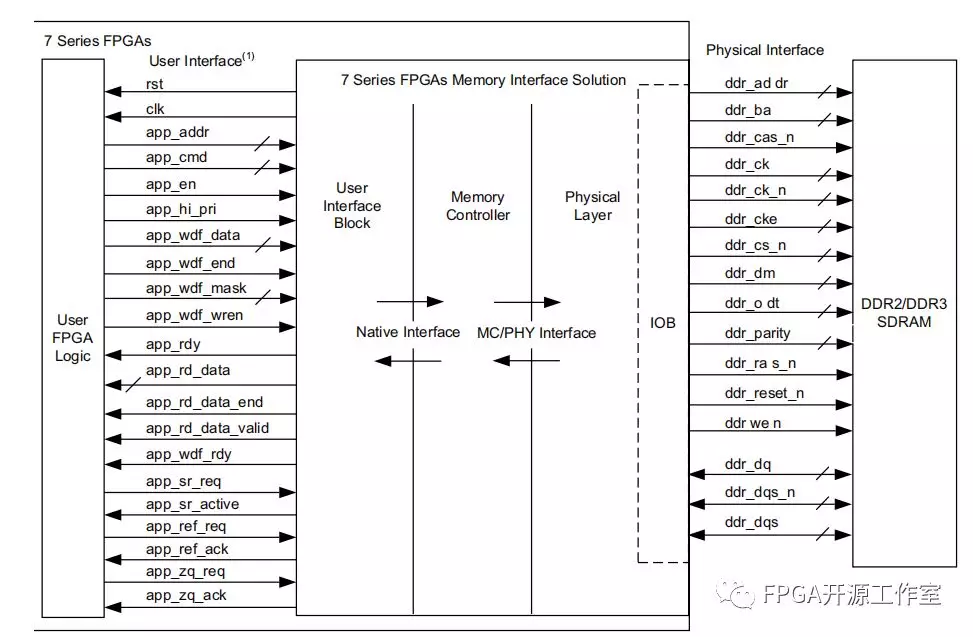

2 mig介紹

如上圖所示,mig(Memory Interface Solution) IP由三部分組成User Interface Block,Memory Controller和Physical Layer。IP的一邊是連接DDR3的接口(Physical Interface),另一邊是用戶邏輯控制接口(User FPGA Logic)。想要正確的控制DDR3的讀寫,我們需要正確的設置mig IP和正確的用戶邏輯控制接口邏輯。

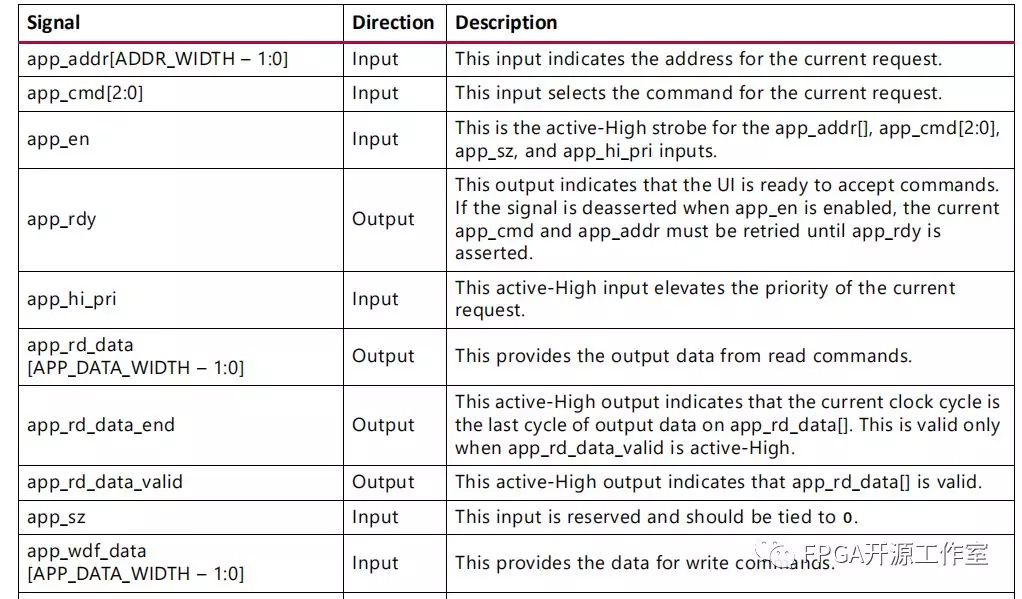

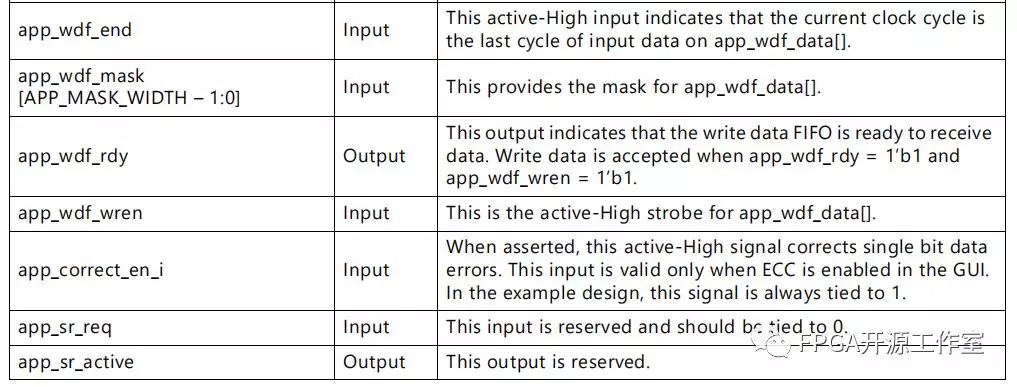

2.1 mig user interface

對于mig用戶端接口含義我們將在《第三篇--mig IP用戶邏輯接口讀寫時序分析》中詳細介紹。

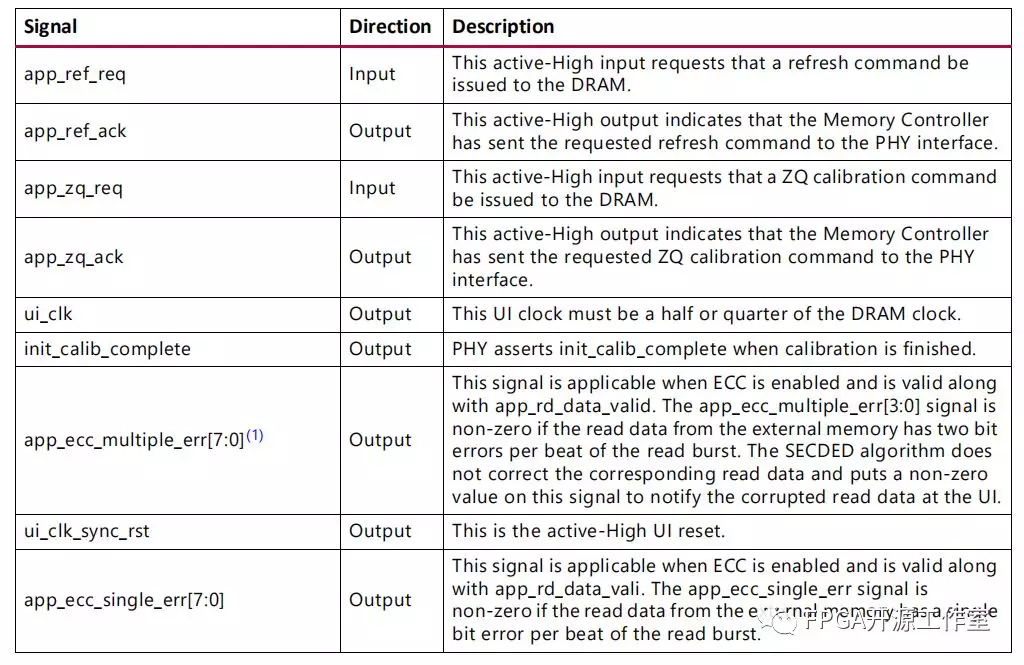

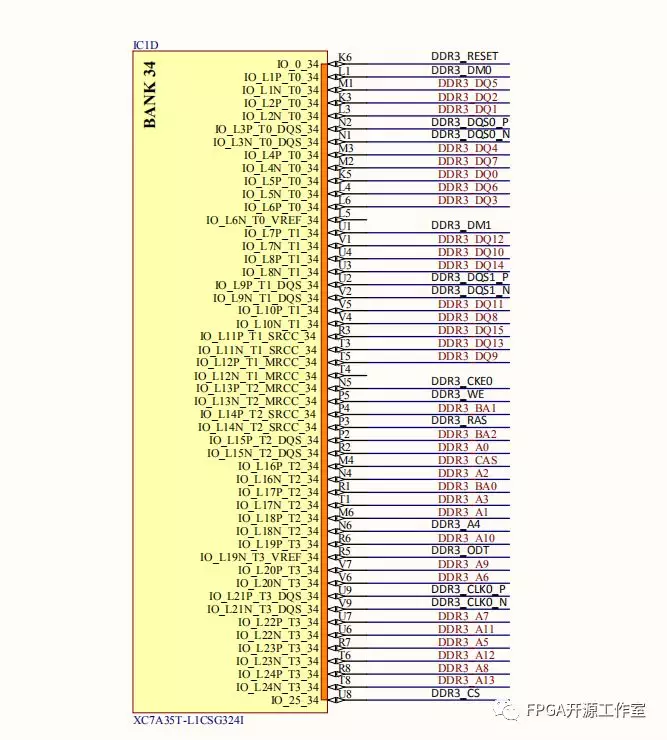

3 DDR3原理圖和FPGA原理圖

通過DDR3的原理圖我們可以知道DDR3的供電電壓為1.35V。DDR3掛在FPGA的34 bank上。

編輯:hfy

-

FPGA

+關注

關注

1640文章

21896瀏覽量

611080 -

DDR3

+關注

關注

2文章

279瀏覽量

42795 -

開發板

+關注

關注

25文章

5350瀏覽量

100455

發布評論請先 登錄

相關推薦

DDR3 SDRAM配置教程

初次使用XC7A35T-FGG484做設計,用的是25MHZ有源晶振,有源晶振3.3V供電,DDR3的供電1.35V,現在接上晶振后,DDR3的供電變成1.8V

三大內存原廠或將于2025年停產DDR3/DDR4

如何用OpenCV進行手勢識別--基于米爾全志T527開發板

基于Arty Artix-35T FPGA開發板的DDR3和mig介紹

基于Arty Artix-35T FPGA開發板的DDR3和mig介紹

評論