來源:至芯

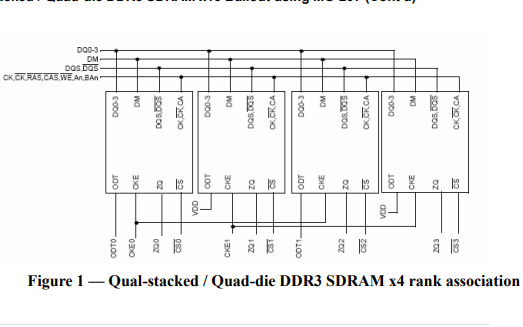

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代產品,相較于DDR2,DDR3有更高的運行性能與更低的電壓。DDR SDRAM是在SDRAM技術的基礎上發展改進而來的;與SDRAM相比,DDR SDRAM的最大特點是雙沿觸發,即在時鐘的上升沿和下降沿都能進行數據采集和發送,同樣的工作時鐘,DDR SDRAM的讀寫速度比傳統的SDRAM快一倍。本次實驗使用的DDR3芯片是MT41J256MM16,芯片的bank位寬為,行位寬為,列位寬為,所以它的地址大小等于,數據位寬為16bit,所以容量大小為256Mb*16bit,也就是512MB。DDR3是半雙工,讀寫不能同時發生,掉電數據丟失。

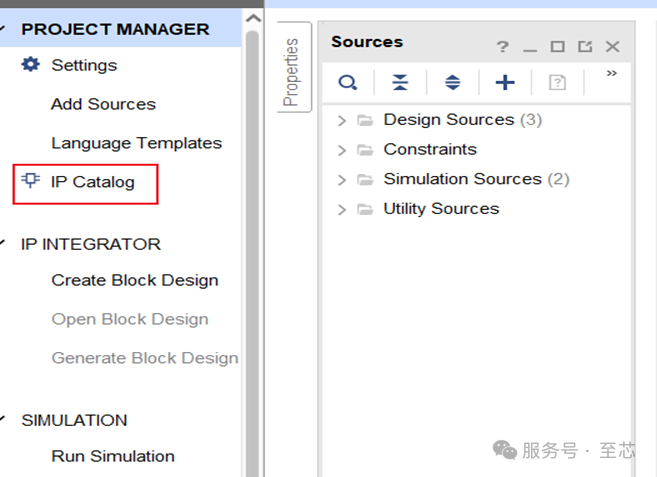

1)點擊“IP Catalog”按鈕。

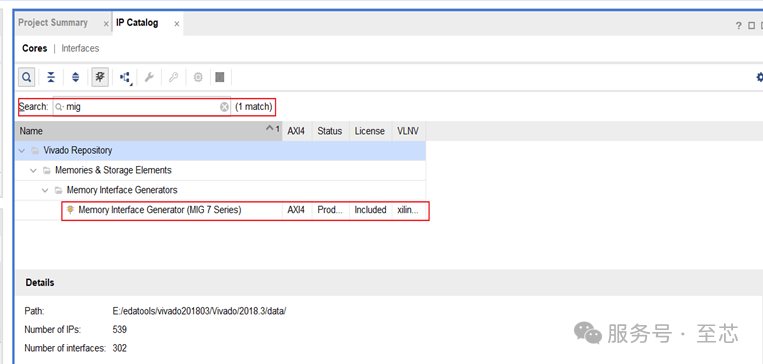

2)在搜索欄中輸入MIG,此時出現MIG IP核,直接雙擊打開。

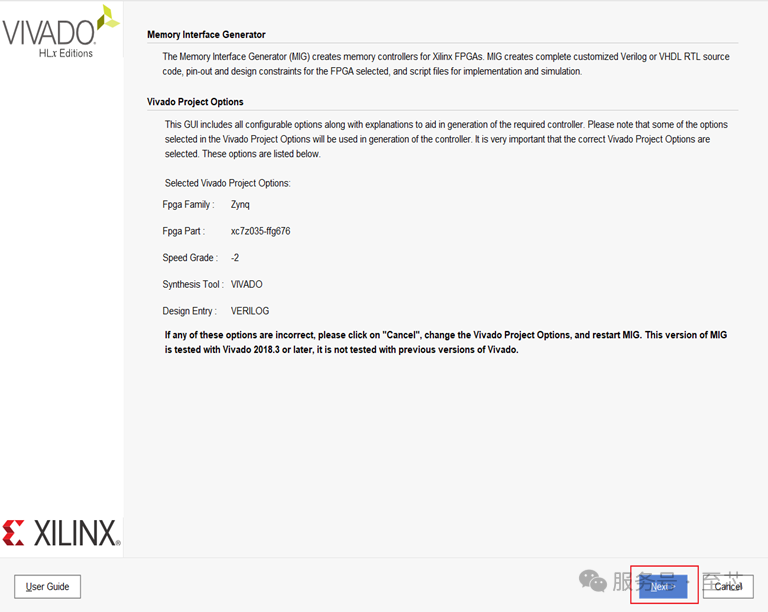

3)確認工程的信息,主要是芯片信息和編譯環境的信息,如果沒有問題,直接點擊“Next”。

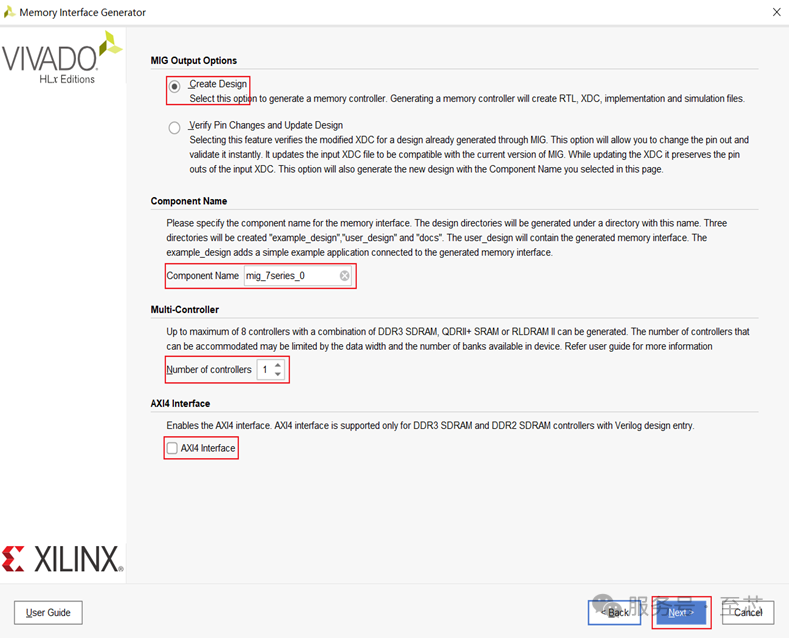

4)選擇“Create Design”,在“Component Name”一欄設置該IP核的名稱,這里取默認軟件的名稱,再往下選擇控制器數量,默認為“1”即可。最后是AXI4接口,本工程使用的是Native接口,不勾選。配置完點擊“Next”。

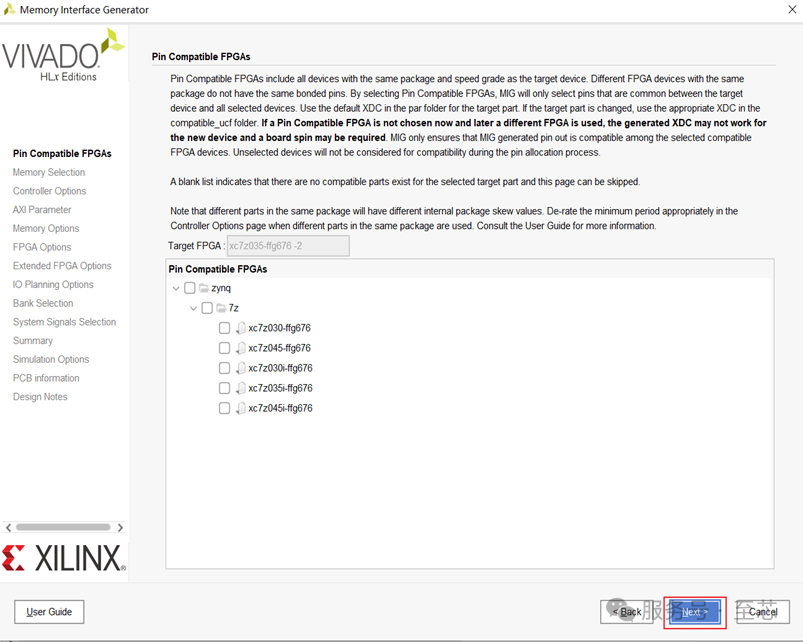

5)這一頁主要是讓用戶選擇可以兼容的芯片,本工程默認不勾選,即不需要兼容其他的FPGA芯片。配置完成點擊“Next”。

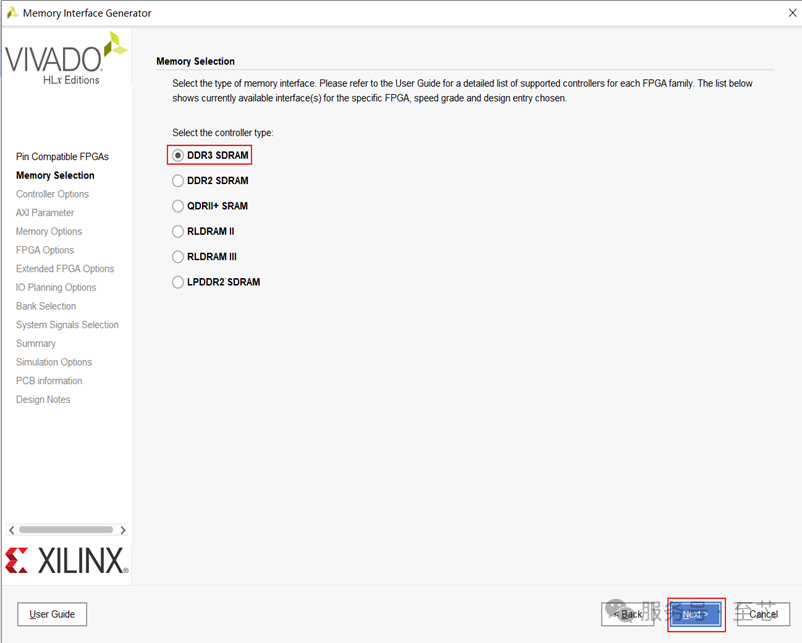

6)這一頁選擇第一個選項“DDR3 SDRAM”,因為本實驗用的就是DDR3芯片。配置完成點擊“Next”。

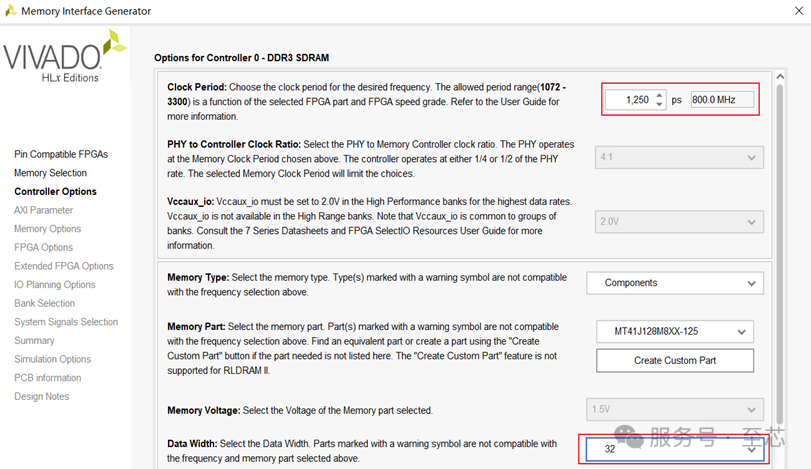

7)配置MIG IP核。

Clock Period:DDR3芯片運行時鐘周期,這個參數的范圍和FPGA的芯片選型以及具體類型的速度等級有關。本實驗選擇1250ps,對應800MHz。注意這個時鐘是由MIG IP核產生,并輸出給DDR3物理芯片使用,它關系到DDR3芯片具體的運行帶寬。本次實驗的開發板板載了2顆DDR3芯片,數據位寬為32位,因為是雙沿觸發,這里帶寬達到了800*32*2=51.2Gb/s。

PHY to ControllerClock Ratio:DDR3物理芯片運行時鐘和MIG IP核的用戶端(FPGA)的時鐘之比,一般有4:1和2:1兩個選項,本次實驗選4:1。由于DDR芯片的運行時鐘是800MHz,因此MIG IP核的用戶時鐘就是200MHz。當DDR3時鐘選擇了350MHz到最高的400MHz,比例默認只為4:1,低于350MHz才有4:1和2:1兩個選項。

VCCAUX_IO:這是FPGA高性能bank(High Performancebank)的供電電壓。它的設置取決于MIG控制器運行的周期/頻率。當用戶讓控制器工作在最快頻率的時候,系統會默認為2.0V。

Memory Type:DDR3存儲器類型選擇。本實驗選擇Component。

Memory Part:DDR3芯片的具體型號。本實驗選擇MT41J256M8XX-125,這個型號其實和實際硬件原理圖上的型號是不同的,這個沒關系,只要用戶的DDR3芯片容量和位寬一致大部分是可以兼容的,其他的型號也是可以的。

Memory Voltage:是DDR3芯片的電壓選擇,本實驗選1.5V。

Data Width:數據位寬選擇,根據硬件原理圖選擇,選擇32,因為是2片DDR拼接而成的。

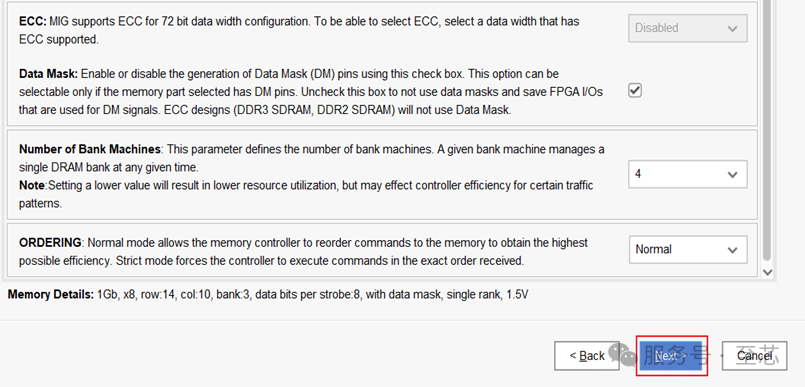

ECC:ECC校驗使能,數據位寬為72位的時候才能使用,本實驗不使用它。

Data Mask:數據屏蔽管腳使能。

Number of BankMachine:Bank Machine的數量是用來對具體的每個或幾個來單獨控制的,選擇多了控制效率就會高,相應的占用的資源也多,本實驗選擇4個,平均一個Bank Machine控制兩個Bank。

ORDERING:該信號用來決定MIG控制器是否可以對它的指令進行重新排序,選擇Normal則允許,Strict則禁止。本實驗選擇Normal,從而獲得更高效率。

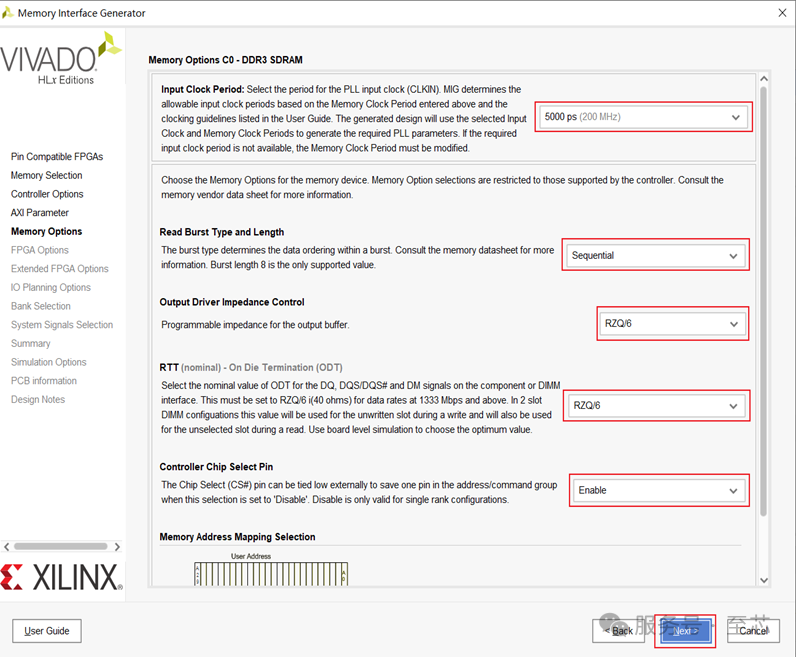

點擊“Next”,如下圖所示:

Input ClockPeriod:MIG IP核的系統輸入時鐘,該輸入時鐘是由FPGA內部產生的,本次實驗選擇的時鐘頻率為200MHz(5000ps)。

Read Burst Typeand Length:突發類型選擇,突發類型有順序突發和交叉突發兩種,本實驗選擇順序突發(Sequential),其突發長度固定為8。

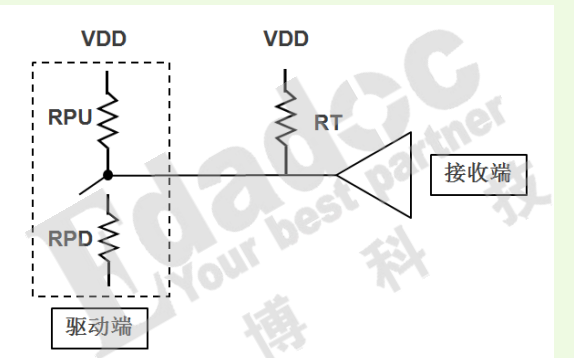

Output DriverImpdance Control:輸出阻抗控制。本實驗選擇RZQ/7。

RTT:終結電阻,可進行動態控制。本實驗選擇RZQ/4。

Controller ChipSelect Pin:片選管腳引出使能。本實驗選擇enable,表示把片選信號cs引出來,由外部控制。

BANK_ROW_COLUMN:尋址方式選擇。本實驗選擇第二種,即BANK-ROW-COLUMN的形式,這是一種最常規的DDR3尋址方式,即要指定某個地址,先指定bank,再指定行,最后指定列,這樣就確定了具體地址。一般來說這樣尋址方式有利于降低功耗,但是讀寫性能上不如“ROW_BANK_COLUMN”。配置完成點擊“Next”。

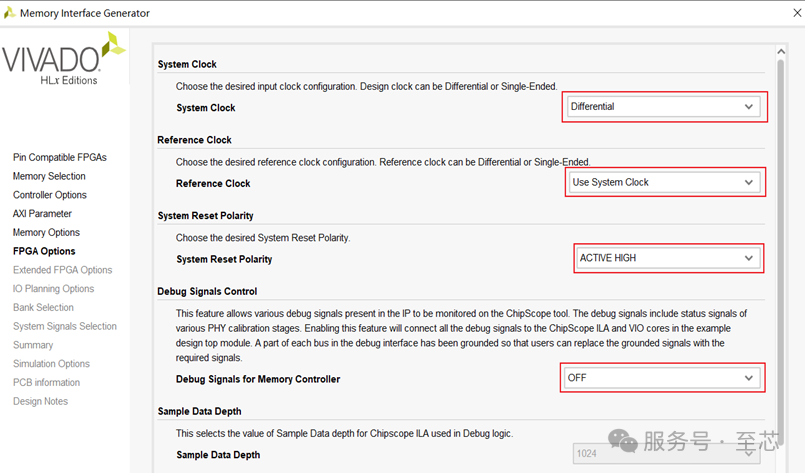

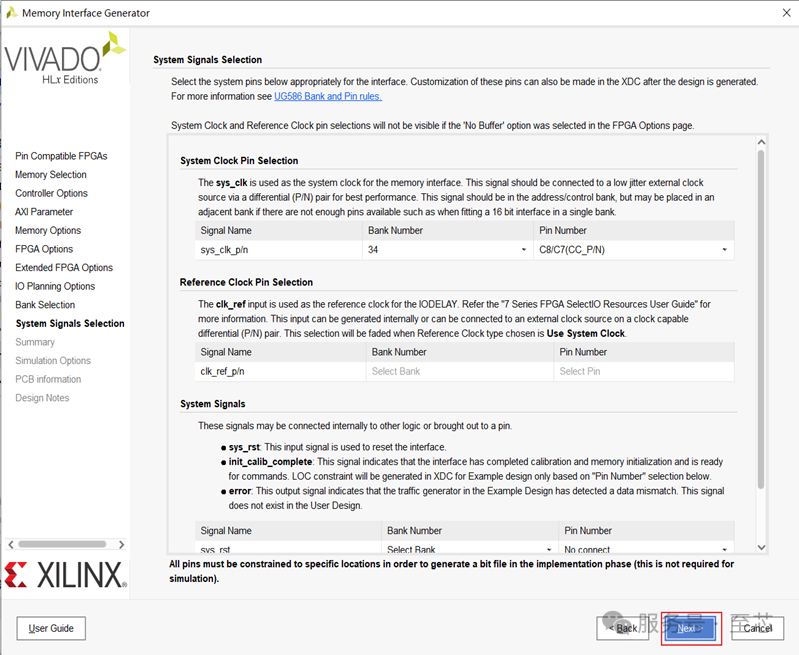

System Clock:MIG IP核輸入時鐘。本實驗選擇“Differential”,由外部晶振提供。

Referance Clock:MIG IP核參考時鐘。選擇“Use SystemClock”這個選項,這時候的MIG IP系統時鐘同時作為了參考時鐘,MIG IP核參考時鐘要求是200MHz,而MIG IP核的系統時鐘剛好也使用了200MHz的系統時鐘。

System ResetPolarity:復位有效電平選擇。本實驗選擇“ACTIVE HIGH”高電平有效。

Debug SignalsControl:該選項用于控制MIG IP核是否把一些調試信號引出來,它會自動添加到ILA,這些信號包括一些DDR3芯片的校準狀態信息。本實驗選擇“OFF”,不需要讓MIG IP核產生各種調試信號。

Sample DataDepth:采樣深度選擇。當“Debug Signals Control”選擇“OFF”時,所有采樣深度是不可選的。

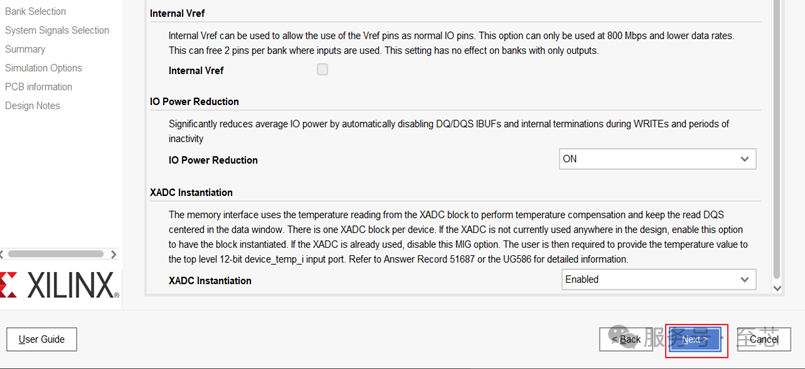

Internal Vref:內部參考管腳,表示將某些參考管腳當成普通的輸入管腳來用。由于開發板的IO資源較為緊張,因此這里需要選擇“ON”,把參考管腳當做普通的輸入管腳來用。

IO PowerReduction:IO管腳節省功耗設置。本實驗選擇“ON”,即開啟。

XADCInstantiation:XADC模塊例化。使用MIG IP核運行的時候需要進行溫度補償,可以直接選擇XADC模塊的溫度數據引到MIG IP核來使用,否則需要額外提供溫度數據,所以本實驗選擇“Enable”。

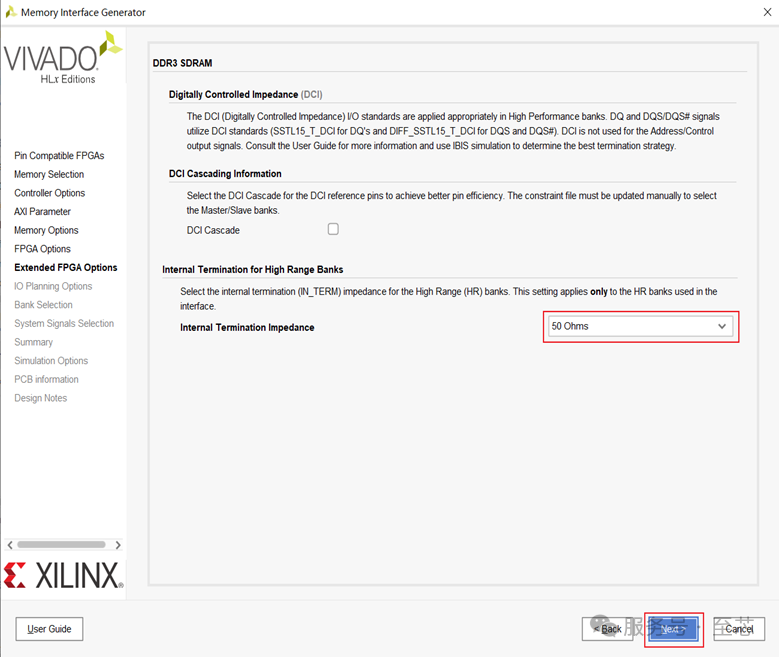

點擊“Next”按鈕,界面如下圖所示:

上圖界面是內部高性能bank端接匹配阻抗的設置,這里不去改它,默認50歐姆即可。接下來點擊“Next”,界面如下圖所示:

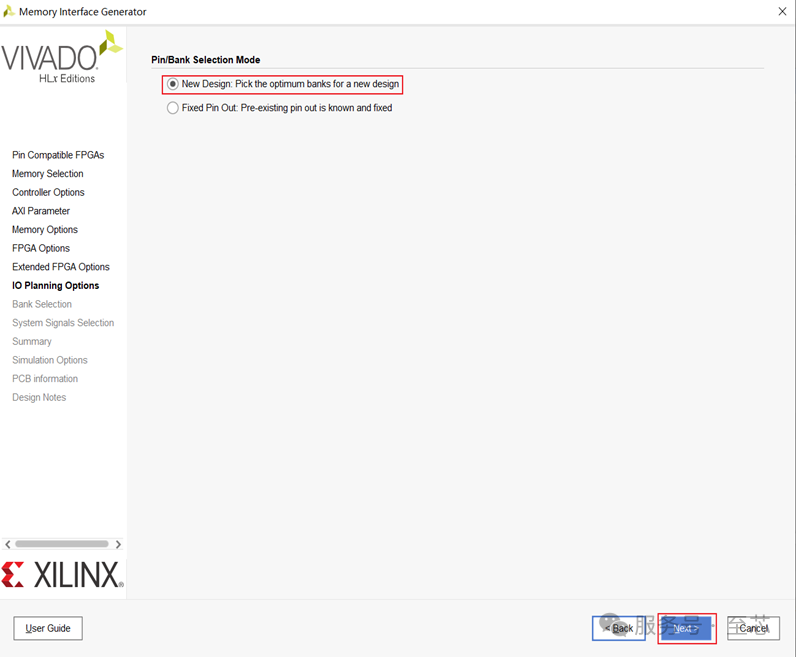

選擇第一種,點擊“Next”,如下圖所示:

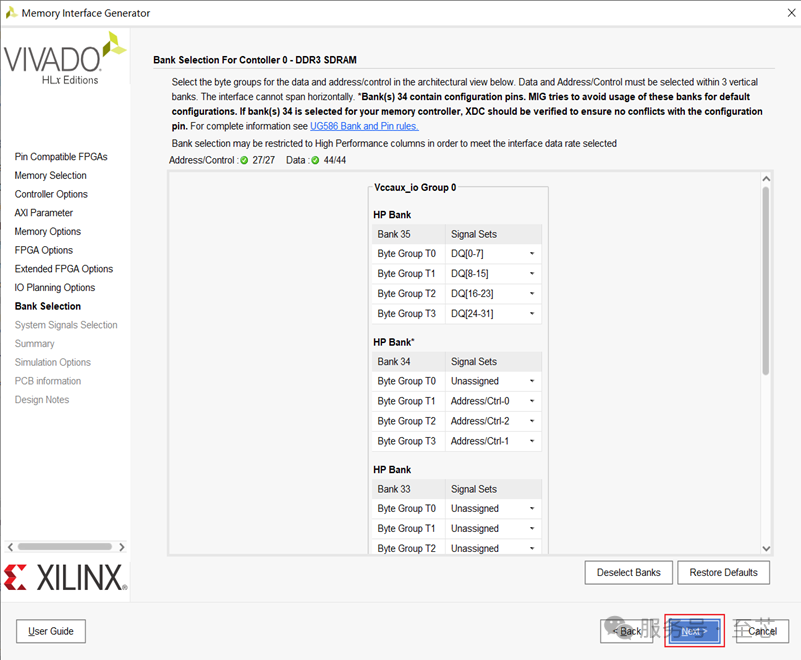

點擊“Next”,如下圖所示:

點擊“Next”,如下圖所示:

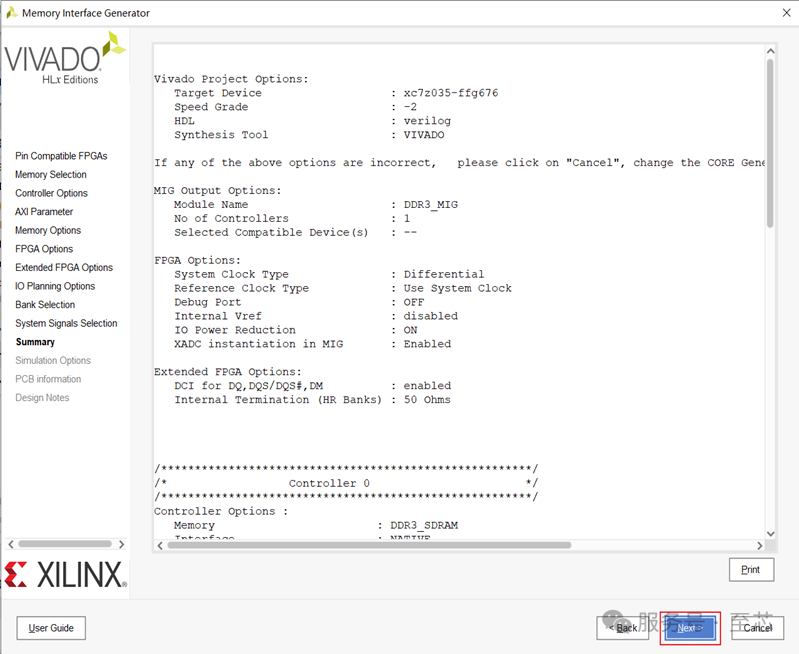

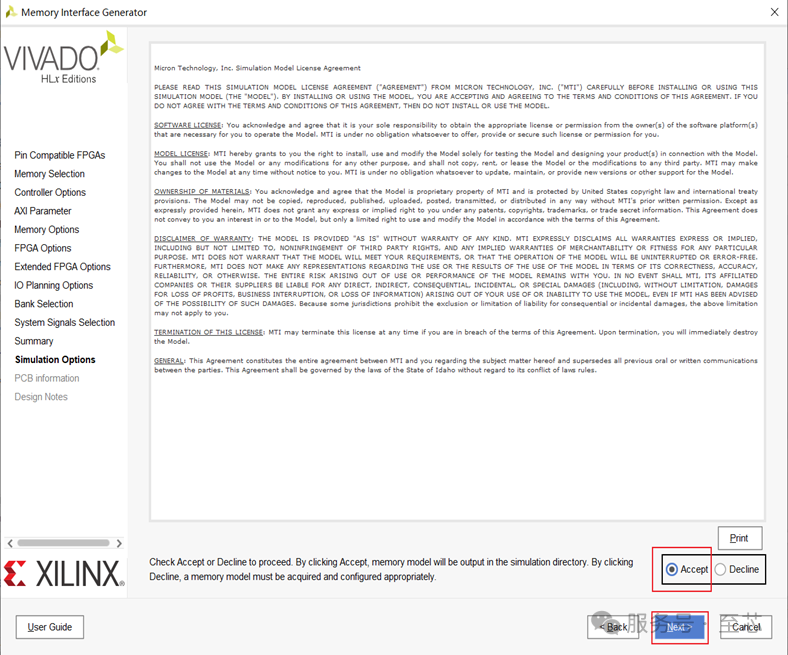

選擇“Accept”,點擊“Next”,如下圖所示:

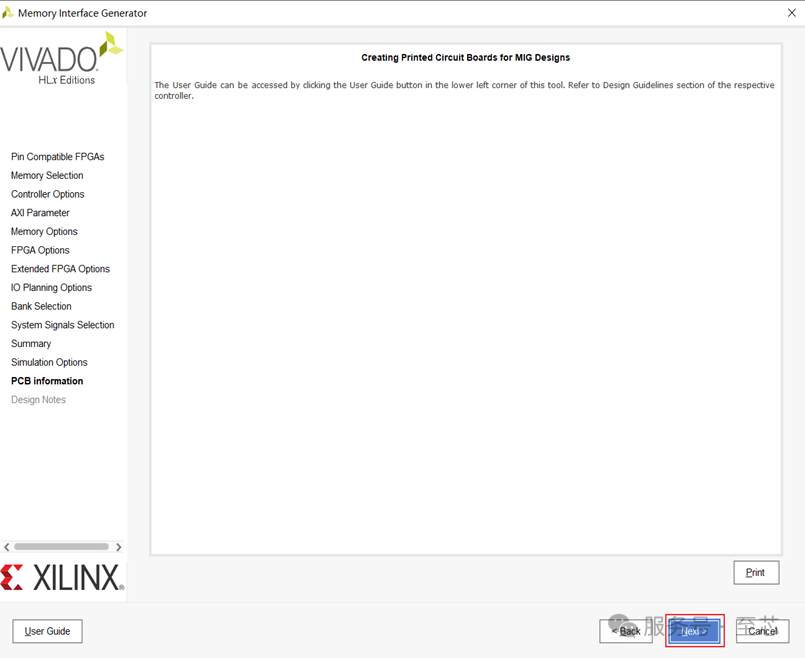

點擊“Next”,如下圖所示:

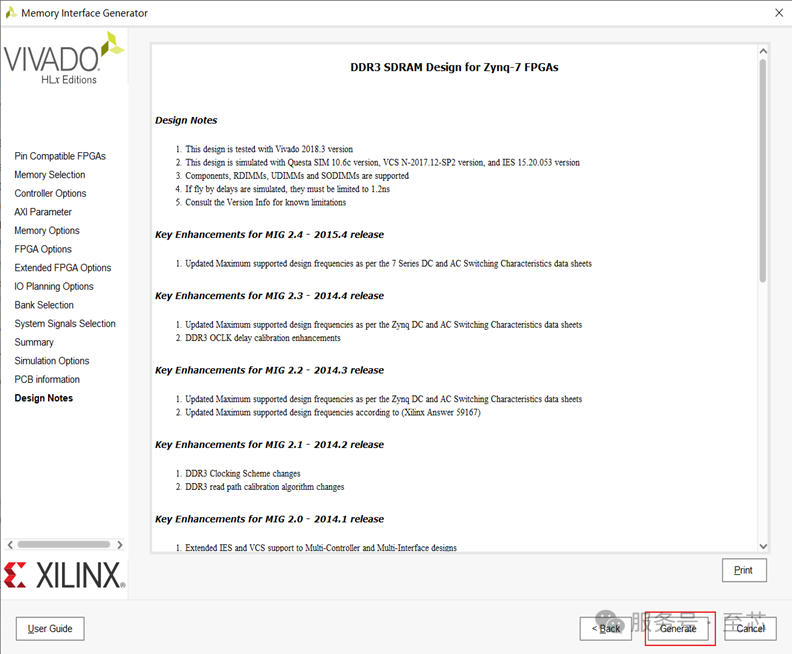

點擊“Generator”,如下圖所示:

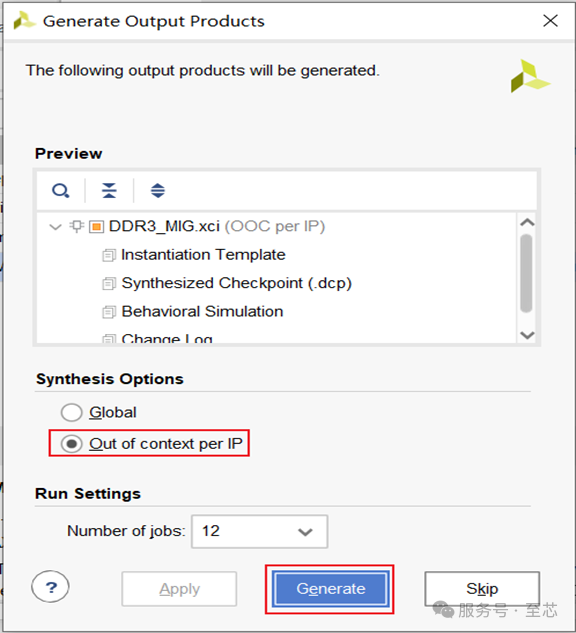

選擇“OOC”模式,點擊“Next”,如下圖所示:

-

芯片

+關注

關注

459文章

52308瀏覽量

437957 -

SDRAM

+關注

關注

7文章

441瀏覽量

56121 -

DDR3

+關注

關注

2文章

283瀏覽量

43006 -

DDR2

+關注

關注

1文章

104瀏覽量

41919

原文標題:DDR3詳細配置步驟

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

DDR3 SDRAM控制器IP核的寫命令和寫數據間關系講解

華邦將持續擴產 DDR3 SDRAM

665x的DDR3配置

ddr3 sdram controller with uniphy 17.1 無法例化

基于Stratix III的DDR3 SDRAM控制器設計

檢驗DDR, DDR2 和DDR3 SDRAM命令和協議

SDRAM,DDR3,DDR2,DDR4,DDR1的區別對比及其特點分析

基于FPGA的DDR3 SDRAM控制器用戶接口設計

DRAM、SDRAM及DDR SDRAM之間的概念詳解

DDR3和DDR4的設計與仿真學習教程免費下載

DDR3 SDRAM的JESD79-3D標準免費下載

DDR3 SDRAM的IP核調取流程

DDR3 SDRAM配置教程

DDR3 SDRAM配置教程

評論