1. 背景

這篇文章主要介紹了DDR3IP核的寫實(shí)現(xiàn)。

2. 寫命令和數(shù)據(jù)總線介紹

DDR3 SDRAM控制器IP核主要預(yù)留了兩組總線,一組可以直接綁定到DDR3 SDRAM芯片端口,一組是留給用戶端使用的,框圖如圖1所示。

如圖1 所示的中間部分為我們調(diào)取的IP 核,user FPGA Logic 為用戶端邏輯,DDR2/DDR3 SDRAM 為存儲(chǔ)芯片。其中IP 核與存儲(chǔ)芯片之間的總線大部分以ddr 作為開頭,這部分總線我們只需要在top 模板設(shè)為端口即可,無需我們控制。用戶端與IP 核之間的總線大部分以app 作為開頭,并且從用戶端輸出到IP 核的信號(hào)線需要我們產(chǎn)生。

在了解了大概的框架之后,下面我們首先通過以app 為開頭的總線實(shí)現(xiàn)對(duì)IP寫控制操作。為了更好的了解相關(guān)的參數(shù),我們可以登錄Xilinx 官網(wǎng)下載UG586手冊(cè),具體的下載地址如下所示: https://www.xilinx.com/support/documentation/ip_documentation/mig_7serie...

通過手冊(cè)我們可以了解到,為了實(shí)現(xiàn)寫,我們需要控制app 端的命令總線和數(shù)據(jù)總線,下面先對(duì)app 端命令總線作解釋,此處的input 和output 均現(xiàn)對(duì)于IP核而言。

| 端口名稱 | 端口名稱 | 端口描述 |

| app_cmd | input | 3bit命令總線,3’b000代表寫,3’b001代表讀。 |

| app_addr | input | 30bit地址總線(位寬根據(jù)芯片不同會(huì)不同)。 |

| app_en | input | 1bit命令使能信號(hào),該信號(hào)有效(高電平),且app_rdy也有效時(shí),IP核才可以接收到用戶端發(fā)送的app_cmd和app_addr。 |

| app_rdy | output | 1bit命令空閑信號(hào),該信號(hào)有效(高電平),且app_en也有效時(shí),IP核才可以接收到用戶端發(fā)送的app_cmd和app_addr。 |

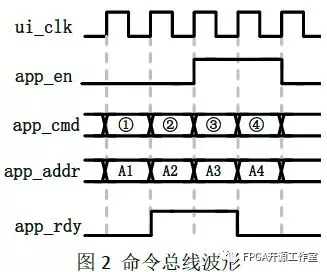

在了解到命令端每一個(gè)信號(hào)的作用后,我們可以給出下圖2 所示的波形,其中①、②、④處的指令均不會(huì)被IP 核接收,只有③處的指令才會(huì)被IP 接收。

app 端寫數(shù)據(jù)總線中的每一根信號(hào)作用如下表所示,此處的input 和output 均現(xiàn)對(duì)于IP 核而言。

| 端口名稱 | 端口名稱 | 端口描述 |

| app_wdf_data | input | 128bit寫數(shù)據(jù)總線(位寬根據(jù)芯片不同會(huì)不同),該數(shù)據(jù)包含8個(gè)需要寫入DDR3芯片的數(shù)據(jù)。 |

| app_wdf_wren | input | 1bit寫數(shù)據(jù)有效標(biāo)志,該信號(hào)有效(高電平),且app_wdf_rdy也有效時(shí),IP核才可以接收到用戶端發(fā)送的app_wdf_data。 |

| app_wdf_rdy | output | 1bit寫數(shù)據(jù)空閑信號(hào),該信號(hào)有效(高電平),且app_wdf_rdy也有效時(shí),IP核才可以接收到用戶端發(fā)送的app_wdf_data。 |

| app_wdf_end | input | 1bit最后一個(gè)寫數(shù)據(jù)的標(biāo)志,該信號(hào)有效(高電平)時(shí),代表對(duì)應(yīng)的app_wdf_data為當(dāng)前寫的最后一個(gè)數(shù)據(jù)。 |

| app_wdf_mask | input | 16bit寫數(shù)據(jù)掩碼(位寬根據(jù)芯片不同會(huì)不同),該信號(hào)為寫數(shù)據(jù)的掩碼。 |

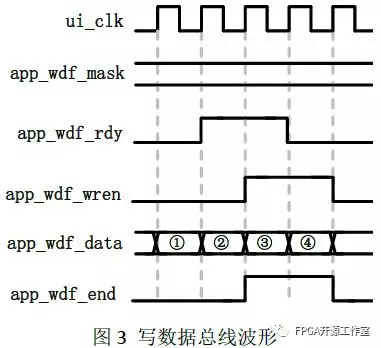

根據(jù)上表所描述,我們可以對(duì)app 端寫時(shí)序所用到的每一根信號(hào)有一點(diǎn)的了解,下面給出寫時(shí)序的波形。圖3 中所示的①、②、④處的數(shù)據(jù)均不會(huì)被寫入到IP 中,只有③處的數(shù)據(jù)才會(huì)被IP 接收。

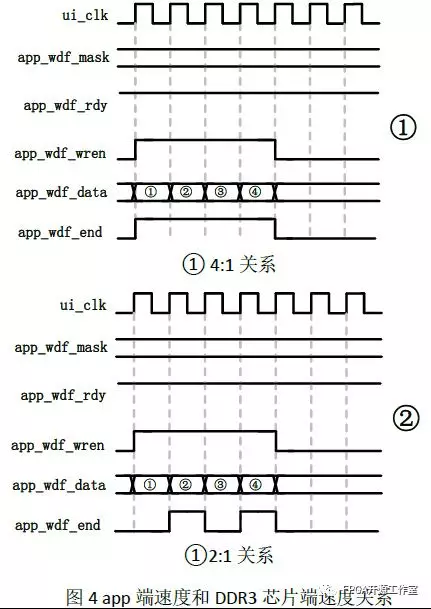

我們對(duì)app_wdf_end 這個(gè)信號(hào)做最進(jìn)一步的講解,該信號(hào)表示的是當(dāng)前突發(fā)寫的最后一個(gè)數(shù)據(jù)。在A7 DDR3 控制器IP 核中,只存在突發(fā)長度為8 這種形式,因此每一次的突發(fā)均為16bit x 8 = 128bit,并且在我們調(diào)取該IP 核時(shí),會(huì)發(fā)現(xiàn)DDR3 的物理層端與用戶端存在兩種速率關(guān)系,即4:1 和2:1。當(dāng)選取速率比例為4:1 時(shí)app_wdf_data 為128bit,此時(shí)每一個(gè)發(fā)送的有效app_wdf_data 數(shù)據(jù)均為當(dāng)前8 突發(fā)的第一個(gè)數(shù)據(jù),同時(shí)也是最后一個(gè)數(shù)據(jù),因此此時(shí)app_wdf_end 信號(hào) 與app_wdf_wren 信號(hào)同步;當(dāng)選取速率比例為2:1 時(shí)app_wdf_data 為64bit,此時(shí)每一個(gè)發(fā)送的有效app_wdf_data 數(shù)據(jù)均為當(dāng)前突發(fā)的4 個(gè)數(shù)據(jù),因此此時(shí)app_wdf_end 信號(hào)與app_wdf_wren 信號(hào)如下圖②所示。

3. 寫命令和寫數(shù)據(jù)間關(guān)系講解

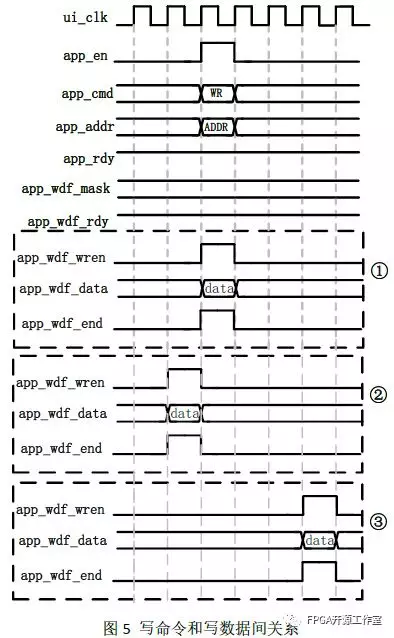

根據(jù)Xilinx UG586 手冊(cè)我們可知,寫命令和寫數(shù)據(jù)直接存在三種邏輯關(guān)系,具體示例如圖5 所示。圖中①狀態(tài)指的是命令和數(shù)據(jù)同時(shí)發(fā)送到IP 核,②狀態(tài)指的是數(shù)據(jù)提前于命令發(fā)送到IP 核,③狀態(tài)指的是命令提前于數(shù)據(jù)發(fā)送到IP 核。第①、②種情況均可穩(wěn)定傳輸,但是第③種情況需要一個(gè)前提條件,即命令提前數(shù)據(jù)的時(shí)間不能超過兩個(gè)用戶端的時(shí)鐘周期。因此,為了更穩(wěn)定的發(fā)送數(shù)據(jù),建議采取第①、②種發(fā)送模式,在本講中,我們采取第②種發(fā)送方式。

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1644文章

21993瀏覽量

615439 -

SDRAM

+關(guān)注

關(guān)注

7文章

441瀏覽量

56121 -

DDR3

+關(guān)注

關(guān)注

2文章

283瀏覽量

43003 -

Xilinx

+關(guān)注

關(guān)注

73文章

2184瀏覽量

124598 -

存儲(chǔ)芯片

+關(guān)注

關(guān)注

11文章

931瀏覽量

44017

發(fā)布評(píng)論請(qǐng)先 登錄

NVMe控制器IP設(shè)計(jì)之接口轉(zhuǎn)換

TPS51116 完整的DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數(shù)據(jù)手冊(cè)

DDR3 SDRAM配置教程

燦芯半導(dǎo)體推出DDR3/4和LPDDR3/4 Combo IP

SDRAM控制器的設(shè)計(jì)——Sdram_Control.v代碼解析(異步FIFO讀寫模塊、讀寫SDRAM過程)

教程!FPGA DDR4讀寫實(shí)驗(yàn)(1)

DDR3、DDR4、DDR5的性能對(duì)比

DDR內(nèi)存與SDRAM的區(qū)別 DDR4內(nèi)存與DDR3內(nèi)存哪個(gè)好

FPGA DDR4讀寫實(shí)驗(yàn)

DDR4 SDRAM控制器的主要特點(diǎn)

DDR3寄存器和PLL數(shù)據(jù)表

DDR3 SDRAM控制器IP核的寫命令和寫數(shù)據(jù)間關(guān)系講解

DDR3 SDRAM控制器IP核的寫命令和寫數(shù)據(jù)間關(guān)系講解

評(píng)論