前言

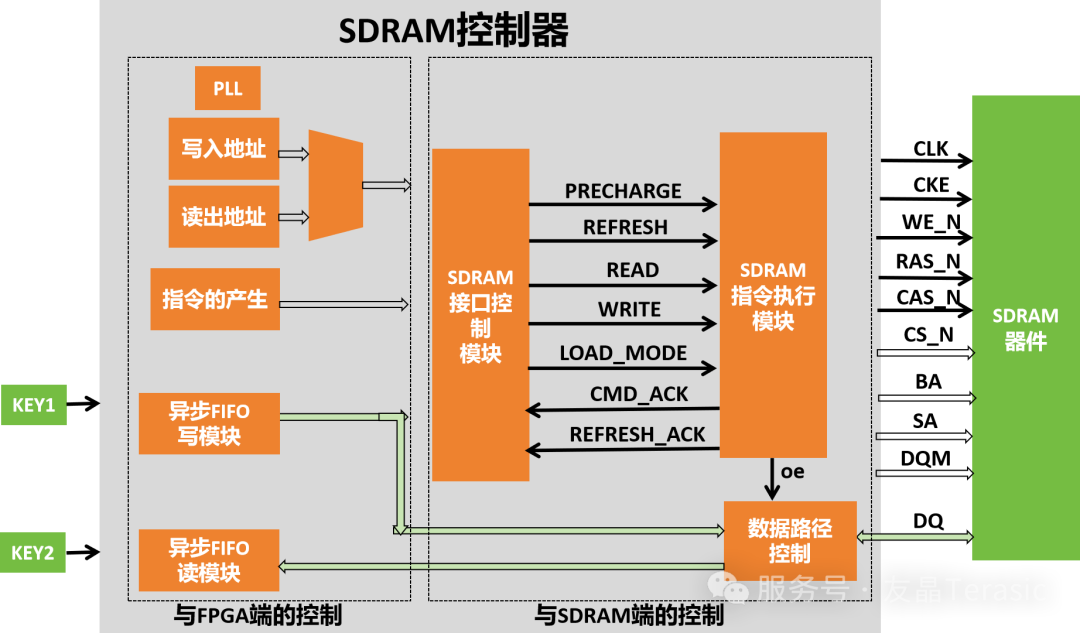

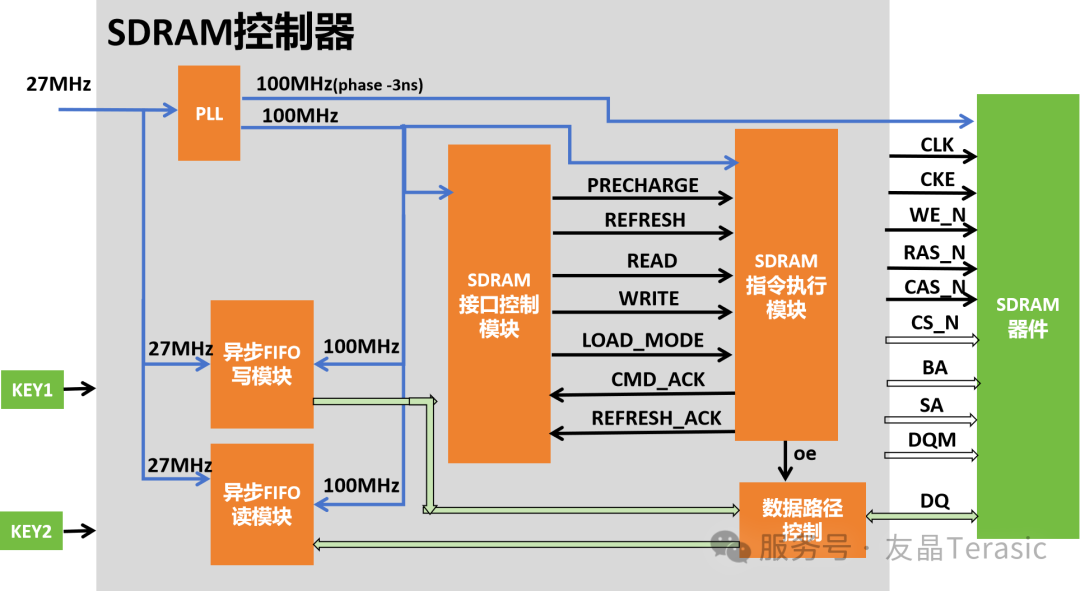

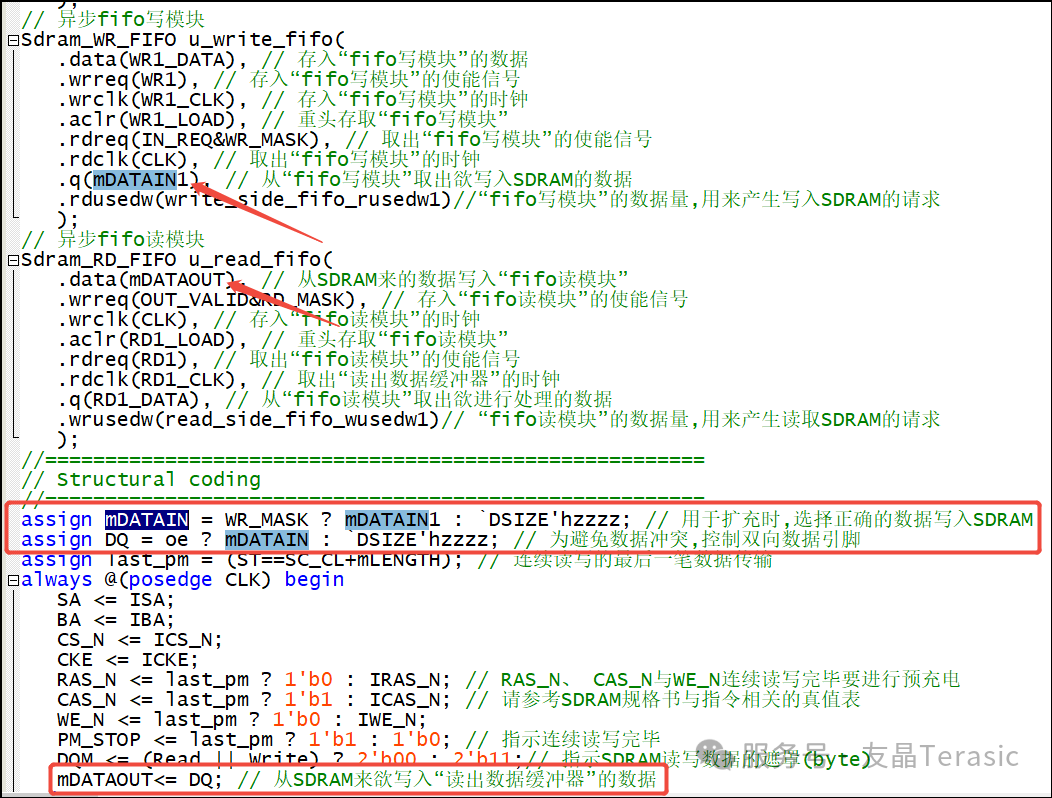

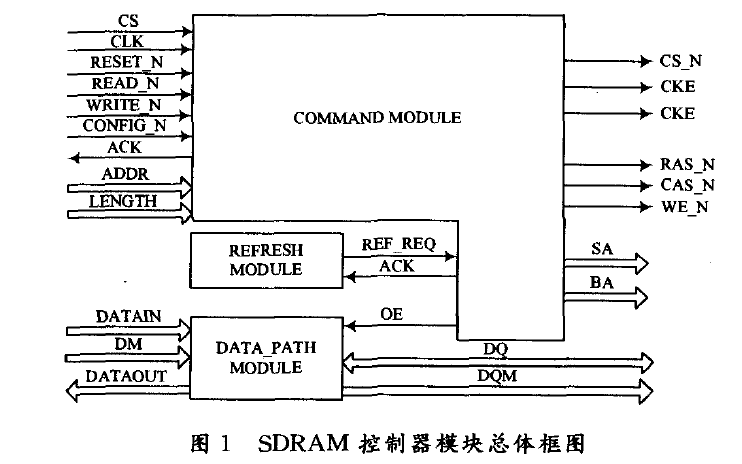

SDRAM控制器里面包含5個(gè)主要的模塊,分別是PLL模塊,異步FIFO 寫模塊,異步FIFO讀模塊,SDRAM接口控制模塊,SDRAM指令執(zhí)行模塊。

其中異步FIFO模塊解讀參考:05-SDRAM控制器的設(shè)計(jì)——異步FIFO的調(diào)用;

http://m.xsypw.cn/d/6468023.html

SDRAM接口控制模塊解讀參考:03-SDRAM控制器的設(shè)計(jì)——control_interface.v代碼解析;

http://m.xsypw.cn/d/6458523.html

SDRAM指令執(zhí)行模塊解讀參考:04-SDRAM控制器的設(shè)計(jì)——command.v代碼解析

http://m.xsypw.cn/d/6466276.html

PLL時(shí)鐘模塊

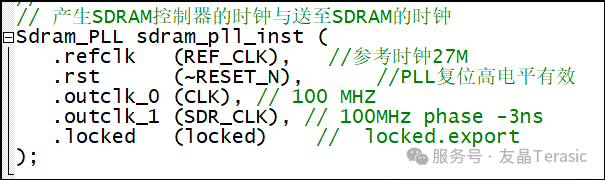

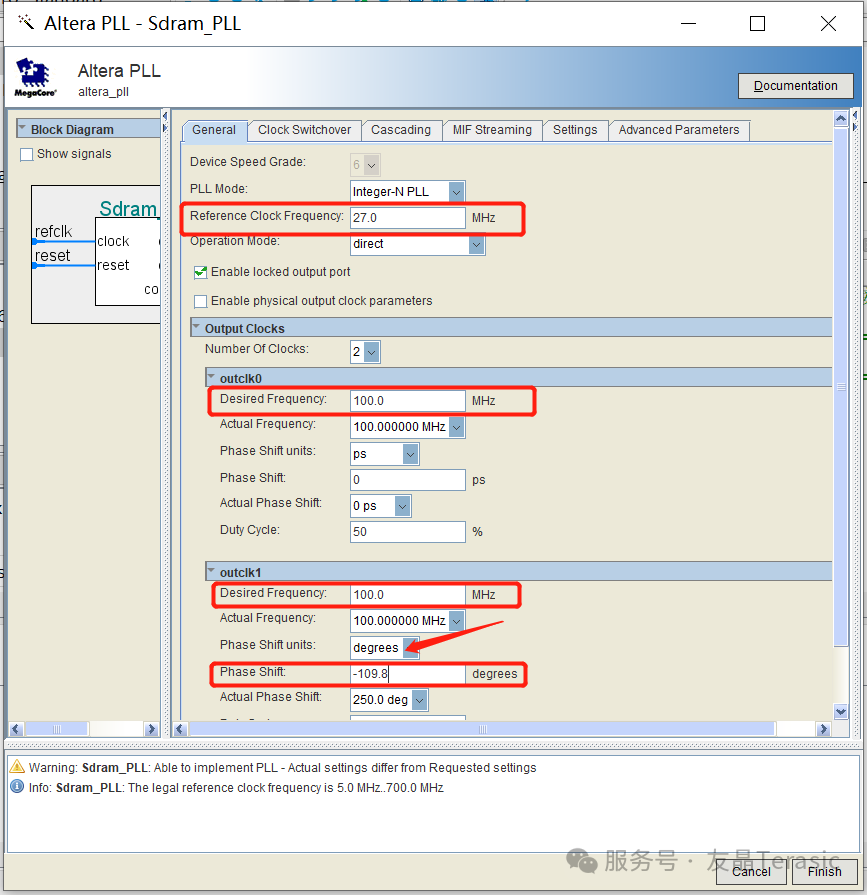

SDRAM控制器模塊里面的PLL將27MHz時(shí)鐘倍頻出2個(gè)100MHz時(shí)鐘,其中一個(gè)100MHz時(shí)鐘給SDRAM里面的模塊使用;另外一個(gè)100MHz時(shí)鐘相移-109.8°以后輸出給SDRAM器件。(相移-109.8°是這個(gè)SDRAM器件在DE10-Standard開發(fā)板上的時(shí)序約束經(jīng)驗(yàn)值)

PLL參數(shù)設(shè)置如下:

關(guān)于Sdram_Control.v模塊時(shí)鐘分布請(qǐng)參考下圖的藍(lán)色走線:

其實(shí)也可以直接從FPGA 的50MHz時(shí)鐘經(jīng)過PLL得到100M時(shí)鐘傳遞給工程里其他模塊工作,這里設(shè)置27M是為了讓大家看看FIFO跨時(shí)鐘域的一個(gè)工作情況。

數(shù)據(jù)路徑控制

SDRAM的數(shù)據(jù)口是一個(gè)inout接口,要做成三態(tài)門控制,控制電路代碼如下:

從command.v傳過來的oe信號(hào)為高時(shí),將數(shù)據(jù)送到DQ端口,此為SDRAM的寫入操作;當(dāng)oe信號(hào)為低時(shí),DQ輸入為高阻,三態(tài)門截止,DQ端口的數(shù)據(jù)送出給讀fifo模塊進(jìn)行緩存,此為SDRAM的讀操作。(關(guān)于oe信號(hào)的控制請(qǐng)參考04-SDRAM控制器的設(shè)計(jì)——command.v代碼解析)

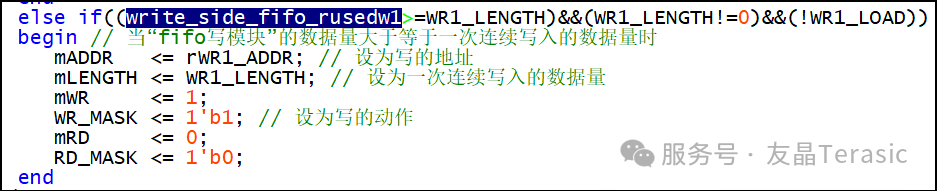

自動(dòng)且連續(xù)的讀寫操作

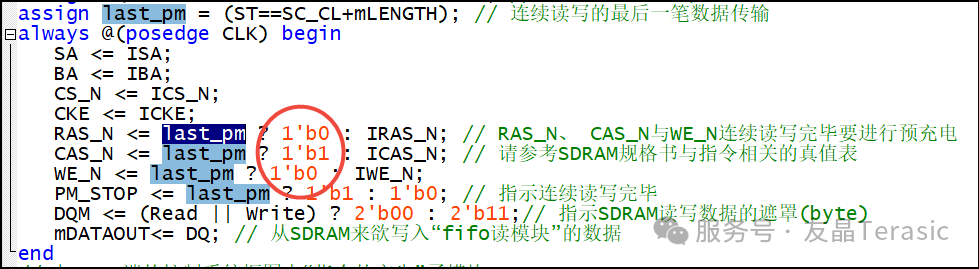

接下來是設(shè)置完成連續(xù)讀寫(64個(gè)數(shù)據(jù))以及進(jìn)行突發(fā)中斷的操作。

command.v模塊里面已經(jīng)設(shè)置突發(fā)長度為整頁(整頁可讀寫數(shù)據(jù)量為1024),所以每次讀寫64個(gè)數(shù)據(jù)后需要提前中斷突發(fā)操作。根據(jù)IS42R16320D手冊(cè)可知下發(fā)突發(fā)中斷命令或者預(yù)充電命令可提前結(jié)束突發(fā)操作。

該案例選擇預(yù)充電命令來結(jié)束突發(fā)操作。參考前面的章節(jié)可知預(yù)充電命令是RAS_N, CAS_N,WE_N組合為010。

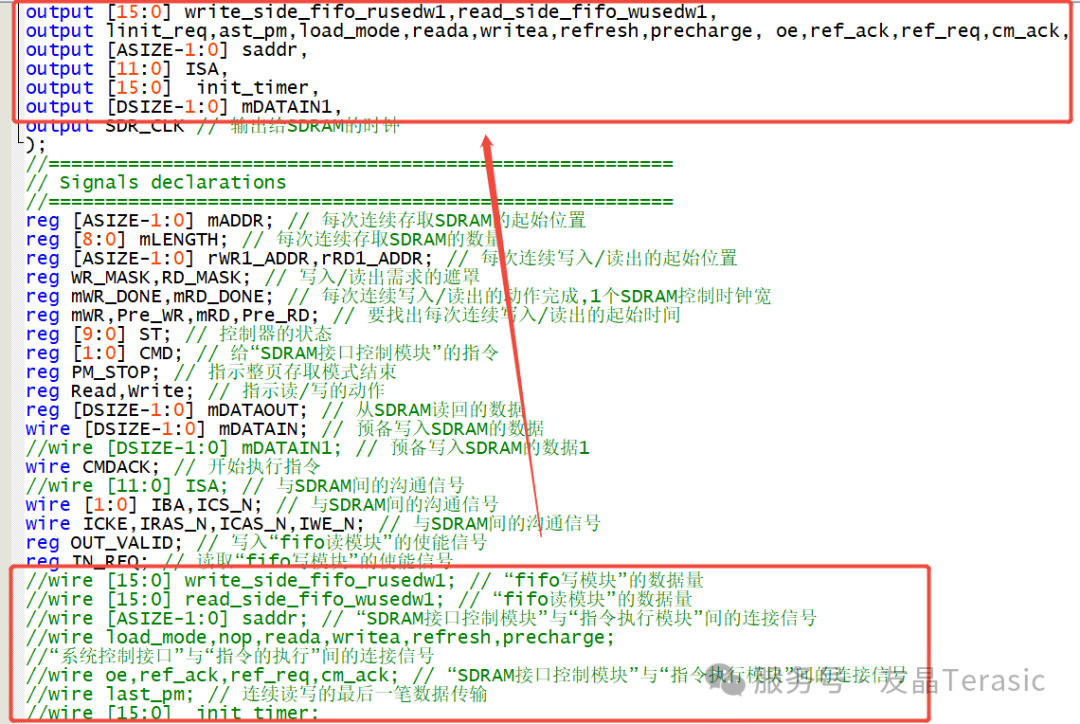

為了拉出相關(guān)信號(hào)查看其波形,先要暫時(shí)把這些信號(hào)輸出,不然這些信號(hào)會(huì)被Quartus在綜合操作時(shí)優(yōu)化掉。

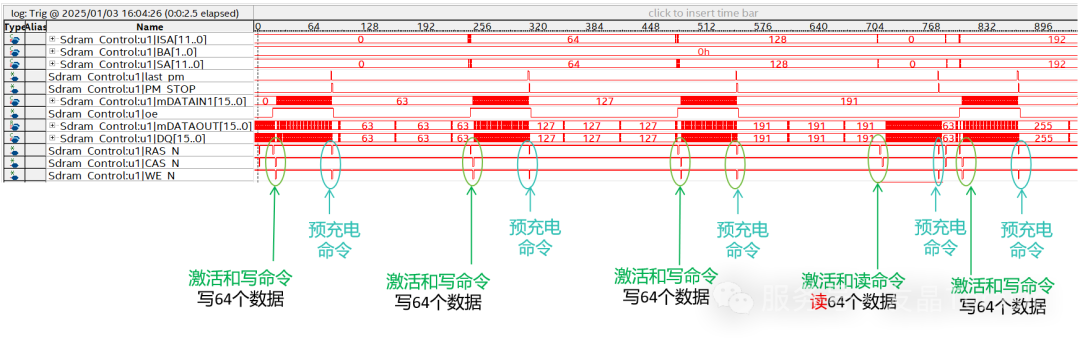

從波形圖可以看到,確實(shí)在每次讀或者寫64個(gè)數(shù)據(jù)后,都會(huì)跟著出現(xiàn)一個(gè)預(yù)充電命令來結(jié)束全頁突發(fā)操作。

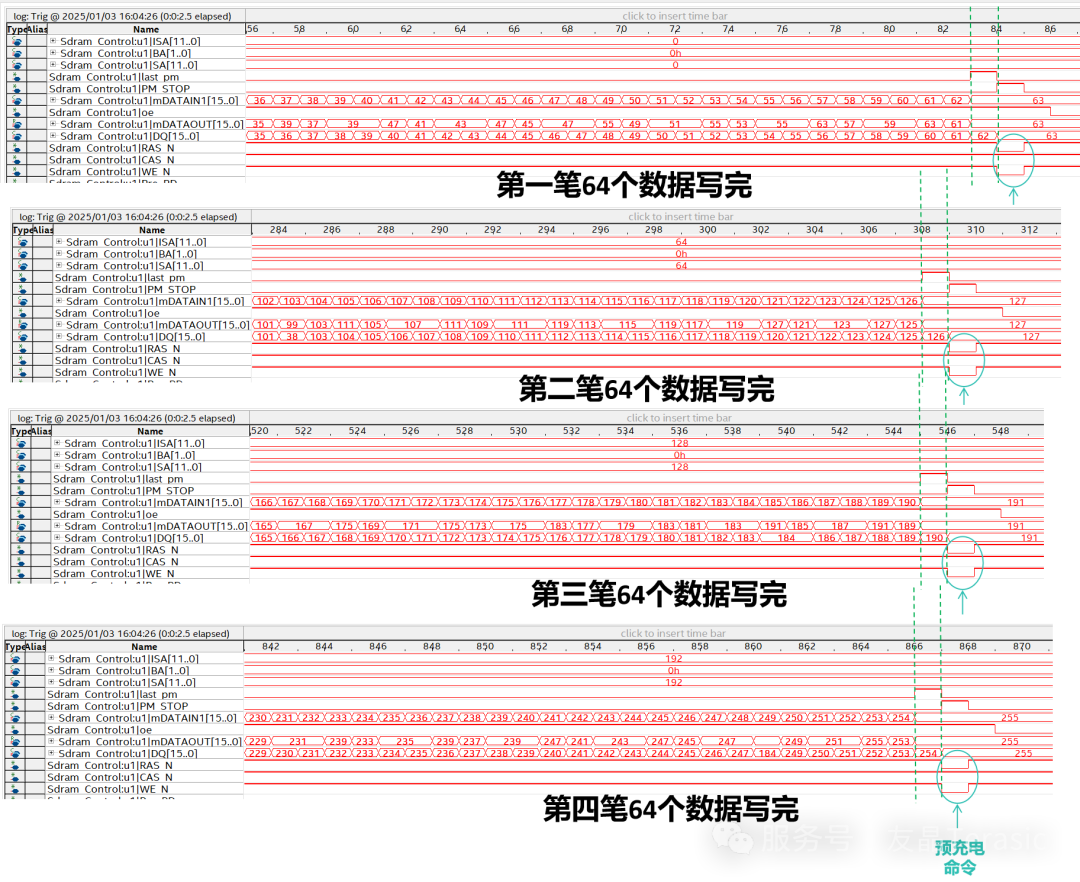

如果上面總體的圖縮小看不清,可以參考下面放大的圖:

可能大家會(huì)疑惑為什么不直接寫256個(gè)數(shù)據(jù),然后讀256個(gè)數(shù)據(jù)?這里設(shè)置64個(gè)數(shù)據(jù)長度是為了讓大家看到多次讀和寫是如何進(jìn)行的。

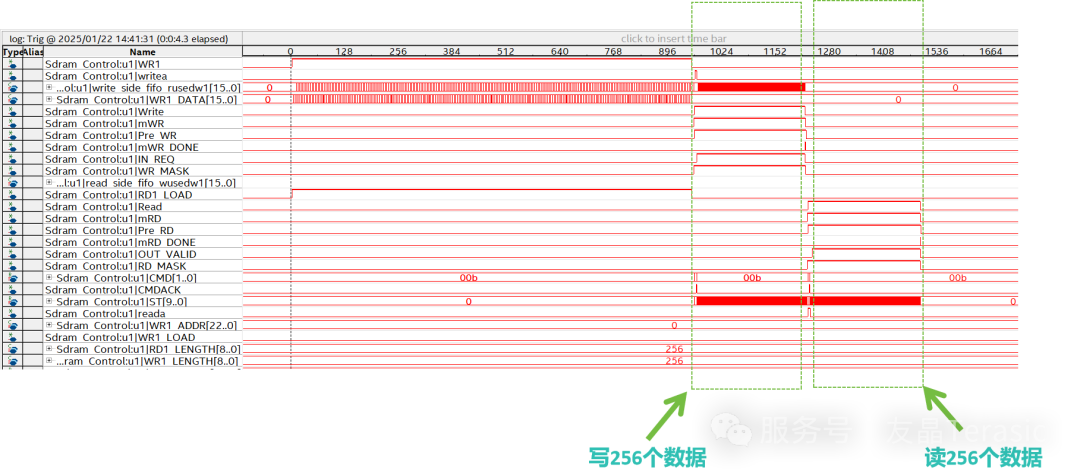

如果想設(shè)置256個(gè)數(shù)據(jù)也是可以的,這時(shí)就把自動(dòng)讀設(shè)計(jì)成寫完256個(gè)數(shù)據(jù)后自動(dòng)進(jìn)行。

此時(shí)的波形圖如圖所示(一次性寫完256個(gè)數(shù)據(jù),一次性讀完256個(gè)數(shù)據(jù)):

指令的產(chǎn)生

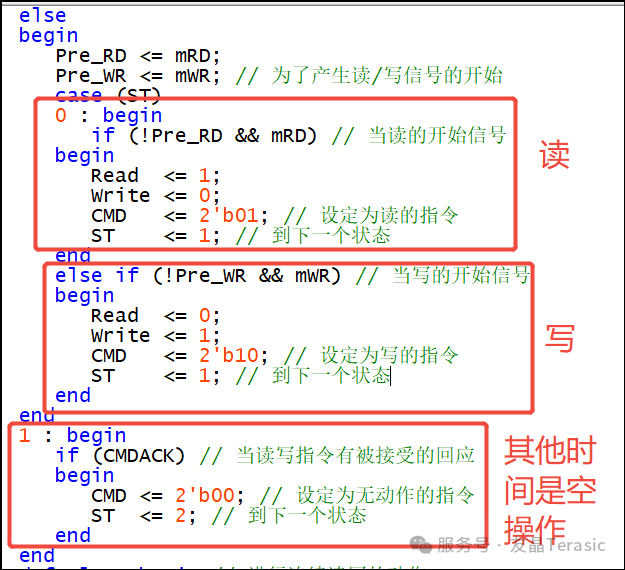

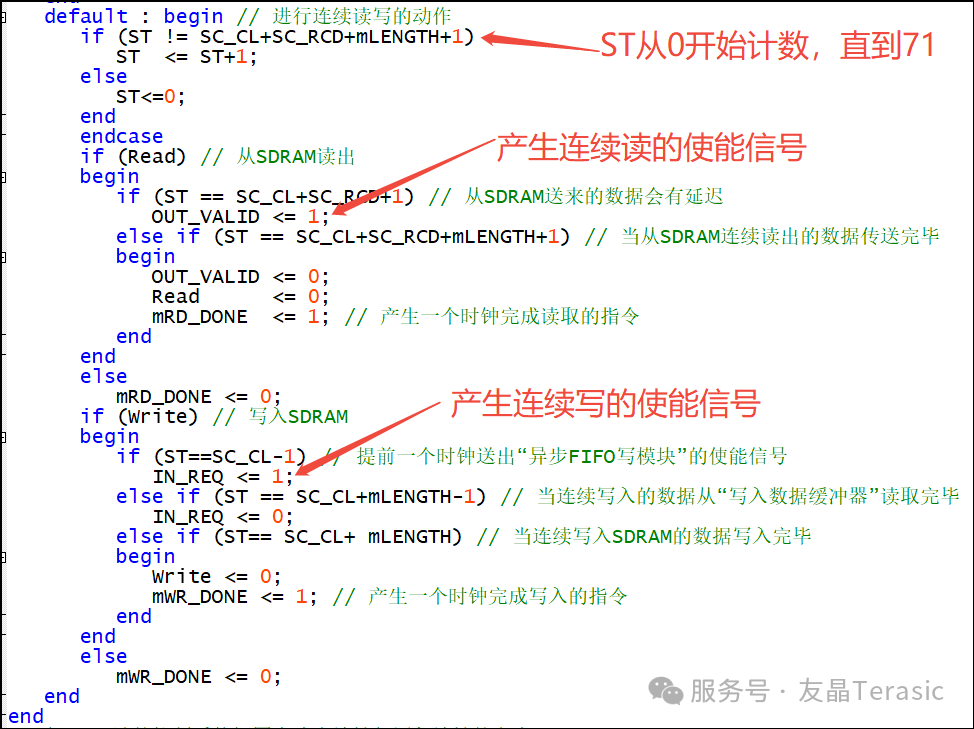

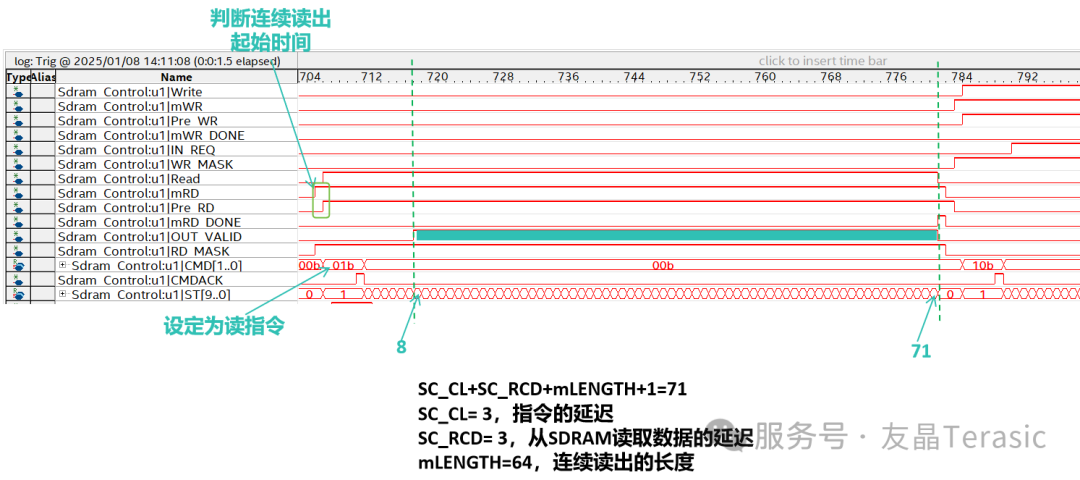

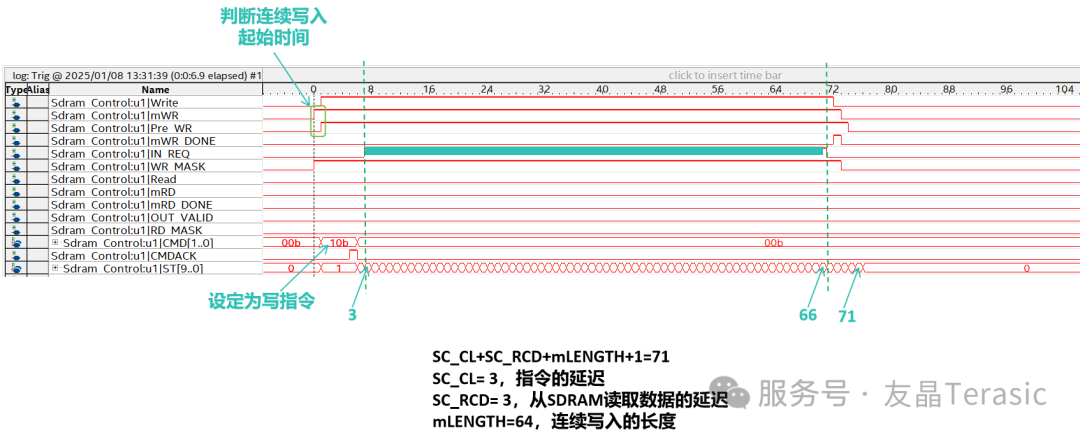

讀過程通過Pre_RD和mRD信號(hào)的組合標(biāo)志出連續(xù)讀的起始時(shí)間,通過Read信號(hào)標(biāo)志出連續(xù)讀的過程。

寫過程通過Pre_WR和mWR信號(hào)的組合標(biāo)志出連續(xù)寫的起始時(shí)間,通過Write信號(hào)標(biāo)志出連續(xù)寫的過程。

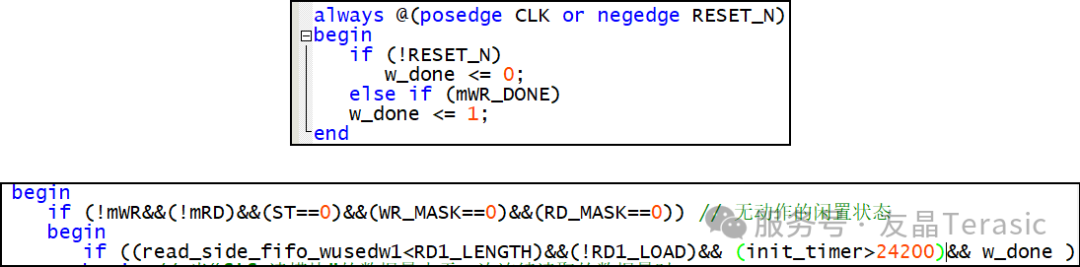

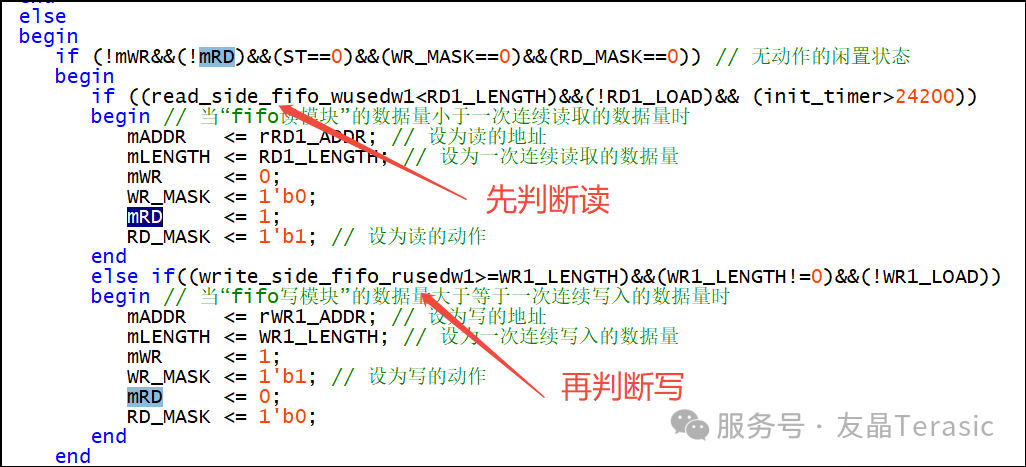

當(dāng)FIFO讀模塊中的數(shù)據(jù)量低于一次需要讀取的數(shù)據(jù)量時(shí),mRD置1;直到連續(xù)讀完成時(shí),mRD才會(huì)清零。即mRD保持為0或1的狀態(tài)都會(huì)持續(xù)多個(gè)周期,因此我們無法通過電平狀態(tài)來判斷是否產(chǎn)生開始讀信號(hào)Read,所以這里采取用寄存器保存mRD的前一狀態(tài),并與當(dāng)前狀態(tài)進(jìn)行比較,當(dāng)前一狀態(tài)為0,當(dāng)前狀態(tài)為1,即產(chǎn)生上升沿時(shí),開始讀信號(hào)Read信號(hào)置1。寫信號(hào)同理。

提前一個(gè)時(shí)鐘送出異步FIFO寫模塊的讀出使能信號(hào)是因?yàn)閷憯?shù)據(jù)沒有延遲,寫命令發(fā)出的當(dāng)拍要準(zhǔn)備好數(shù)據(jù),所以讀使能信號(hào)提前一拍給出。

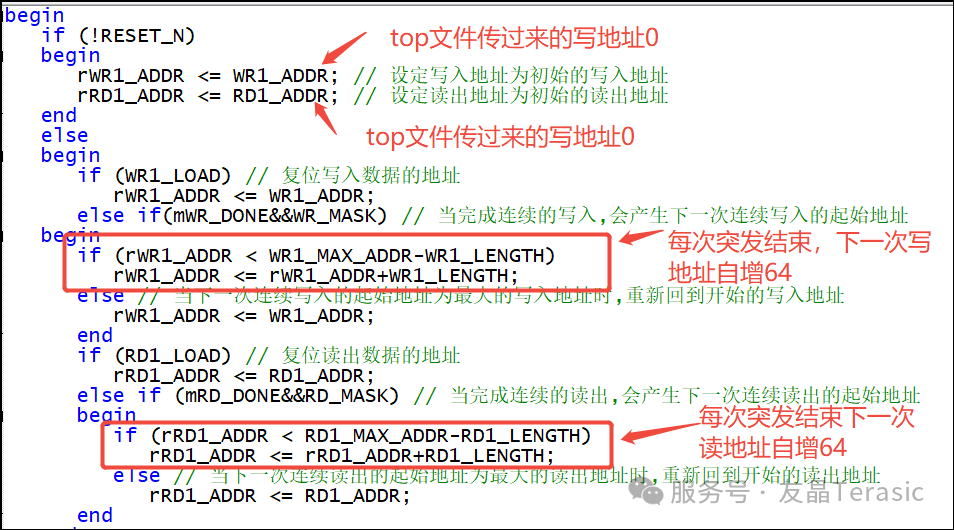

寫入地址和讀出地址

256個(gè)數(shù)據(jù)寫入節(jié)奏是這樣的:

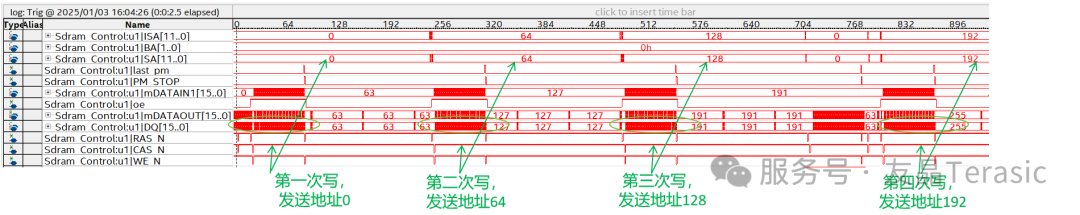

當(dāng)KEY1被按下,觸發(fā)了counter產(chǎn)生數(shù)據(jù)0~255,這個(gè)數(shù)據(jù)同步傳遞給異步FIFO寫模塊進(jìn)行緩存。當(dāng)系統(tǒng)檢測(cè)到write_side_fifo_rusedw1值大于64時(shí),異步FIFO寫模塊的讀出端口會(huì)把FIFO里面的數(shù)據(jù)讀出,傳遞給SDRAM器件進(jìn)行儲(chǔ)存。FIFO一次讀出64個(gè)數(shù)據(jù)。總共會(huì)讀出4次。

從top文件傳遞過來的地址0開始寫SDRAM,一次寫64個(gè)數(shù)據(jù),寫第二筆64個(gè)數(shù)據(jù)時(shí)初始地址是0+64,寫第三筆64個(gè)數(shù)據(jù)時(shí)初始地址是64+64=128,寫第四筆64個(gè)數(shù)據(jù)時(shí)初始地址是128+64=192。

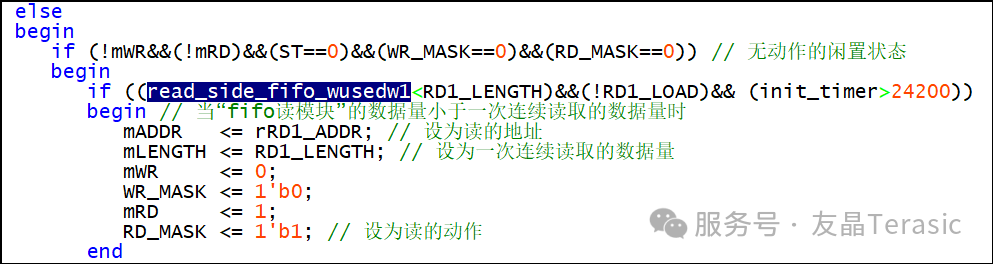

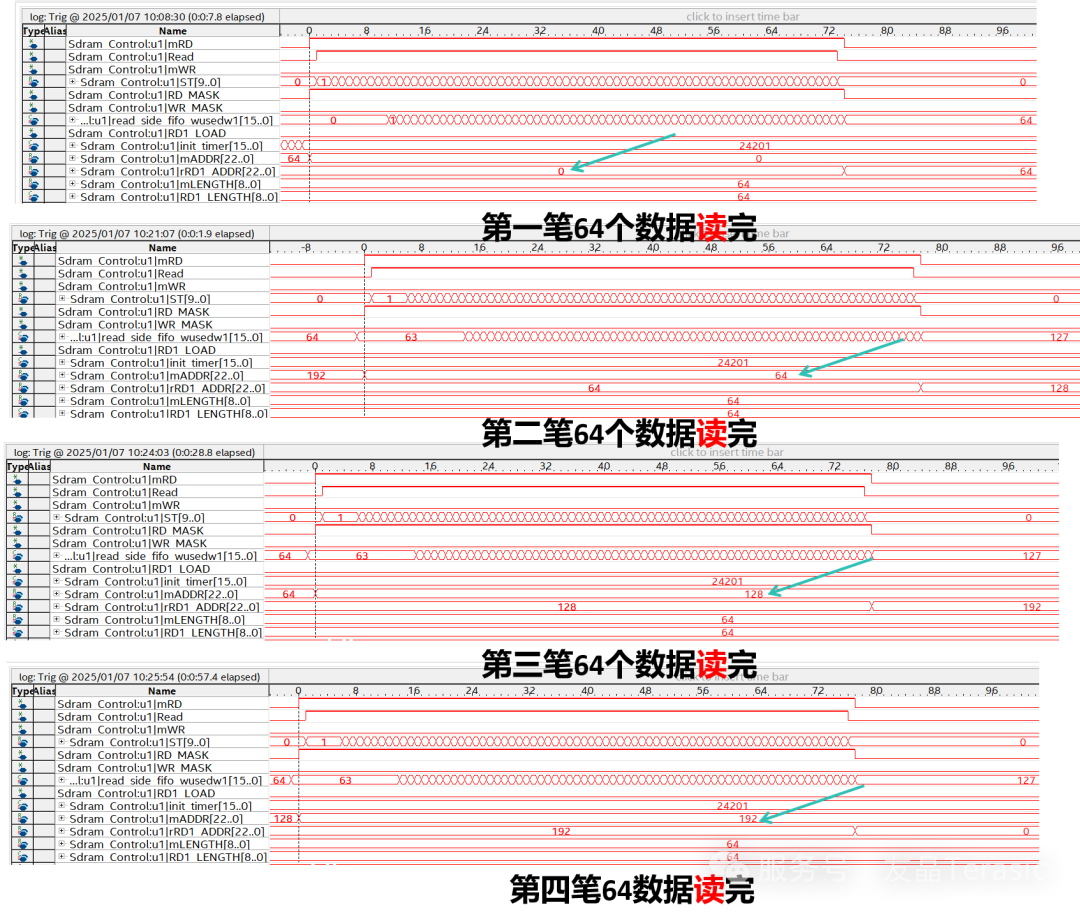

256個(gè)數(shù)據(jù)讀出節(jié)奏是這樣的:

異步FIFO讀模塊從離開初始化狀態(tài)且離開復(fù)位狀態(tài)且檢測(cè)到read_side_fifo_wusedw1小于64時(shí)開始讀取SDRAM器件的數(shù)據(jù)。

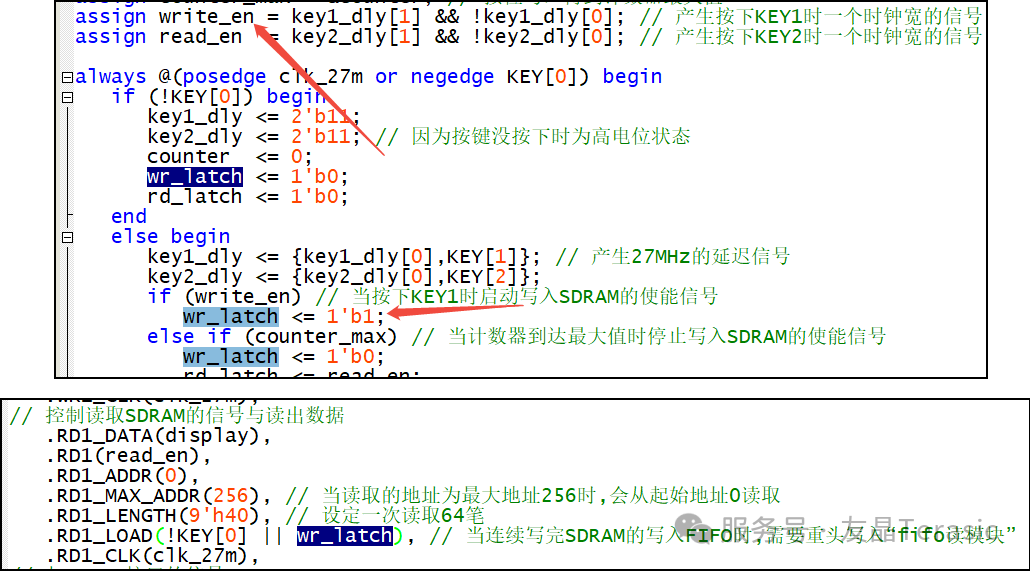

其復(fù)位狀態(tài)的離開主要看KEY0信號(hào)和wr_latch信號(hào):

第一筆64個(gè)數(shù)據(jù)(0~63)是等異步FIFO寫模塊已經(jīng)完成256個(gè)字節(jié)的緩存操作(其中的192個(gè)數(shù)據(jù)已寫入到SDRAM器件了)以后讀出。此時(shí)讀SDRAM的地址送出是0。

第二筆64個(gè)數(shù)據(jù)(64~127)是等異步FIFO讀模塊讀出第一個(gè)數(shù)據(jù)0的下一個(gè)時(shí)鐘節(jié)拍讀出,因?yàn)榇藭r(shí)read_side_fifo_wusedw1的值64-1等于63又小于64。此時(shí)讀SDRAM的地址送出是64。

第三筆64個(gè)數(shù)據(jù)(128~191)是等到異步FIFO讀模塊數(shù)據(jù)又只剩63個(gè)數(shù)據(jù)時(shí)讀出,此時(shí)地址送出是128。

第四筆64個(gè)數(shù)據(jù)(192~255)同樣是等到異步FIFO讀模塊數(shù)據(jù)又只剩63個(gè)數(shù)據(jù)時(shí)讀出,此時(shí)地址送出是192。

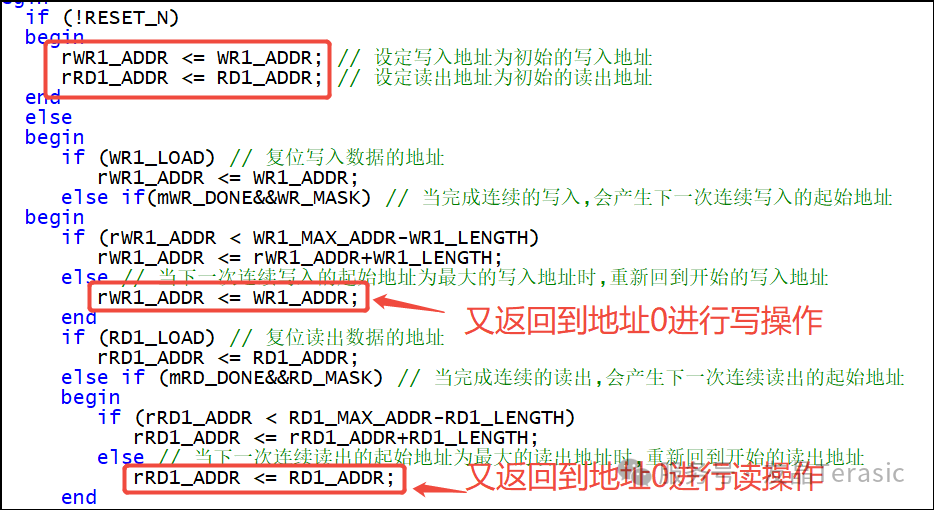

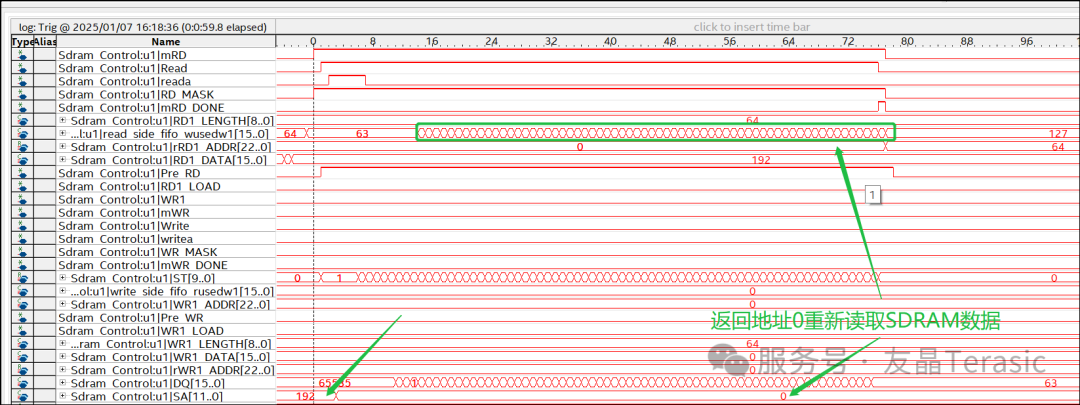

無論是SDRAM寫操作還是讀操作,在讀寫完256個(gè)數(shù)據(jù)后又會(huì)從地址0開始重復(fù)讀寫:

拿SDRAM讀操作來說,當(dāng)讀完256個(gè)數(shù)據(jù)還繼續(xù)觸發(fā)讀操作時(shí)抓取波形圖可以看到:

可能讀者會(huì)有疑惑,當(dāng)異步FIFO寫模塊第四次累計(jì)了64個(gè)數(shù)據(jù)時(shí),為什么沒有馬上寫入SDRAM器件,而是先從SDRAM器件里面讀出64個(gè)數(shù)據(jù)緩存到異步FIFO讀模塊,等這64個(gè)數(shù)據(jù)讀完以后再繼續(xù)往SDRAM里面寫最后的64個(gè)數(shù)據(jù)(192~255)。這里是因?yàn)閕f語句存在優(yōu)先級(jí),電路是先判斷有沒有讀指令,當(dāng)有讀命令時(shí)就先處理讀操作。當(dāng)異步FIFO寫模塊寫入了第四個(gè)64個(gè)數(shù)據(jù)后,異步FIFO讀模塊就離開了復(fù)位狀態(tài),系統(tǒng)會(huì)自動(dòng)發(fā)送讀命令,此時(shí)就開始SDRAM器件數(shù)據(jù)的讀取操作。

PS:

本文的Signaltap波形圖文件對(duì)應(yīng):~sdramcontroloutput_filesSdram_Control.stp

-

fifo

+關(guān)注

關(guān)注

3文章

394瀏覽量

44168 -

代碼

+關(guān)注

關(guān)注

30文章

4859瀏覽量

69649 -

SDRAM控制器

+關(guān)注

關(guān)注

0文章

29瀏覽量

8246

原文標(biāo)題:07-SDRAM控制器的設(shè)計(jì)——Sdram_Control.v代碼解析

文章出處:【微信號(hào):友晶FPGA,微信公眾號(hào):友晶FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【開源騷客】《輕松設(shè)計(jì)SDRAM控制器》第九講—解密讀寫FIFO

多路讀寫的SDRAM接口設(shè)計(jì)

【每周FPGA案例】至簡設(shè)計(jì)系列- SDRAM讀寫控制器

具有時(shí)間隱藏特性的數(shù)據(jù)塊讀寫SDRAM控制器

基于FPGA的高速SDRAM控制器的視頻應(yīng)用

SDRAM控制器簡易化設(shè)計(jì)

NiosII的奇幻漂流-Chap09-SDRAM-v1.0

DDR SDRAM控制器參考設(shè)計(jì)VHDL代碼

華清遠(yuǎn)見FPGA代碼-SDRAM讀寫控制的實(shí)現(xiàn)與Modelsim

SDRAM控制器的設(shè)計(jì)

FPGA讀寫SDRAM的實(shí)例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計(jì)論文

如何使用FPGA設(shè)計(jì)SDRAM控制器

基于SDRAM控制器軟核的Verilog設(shè)計(jì)

SDRAM控制器設(shè)計(jì)之command.v代碼解析

SDRAM控制器的設(shè)計(jì)——Sdram_Control.v代碼解析(異步FIFO讀寫模塊、讀寫SDRAM過程)

SDRAM控制器的設(shè)計(jì)——Sdram_Control.v代碼解析(異步FIFO讀寫模塊、讀寫SDRAM過程)

評(píng)論