前言

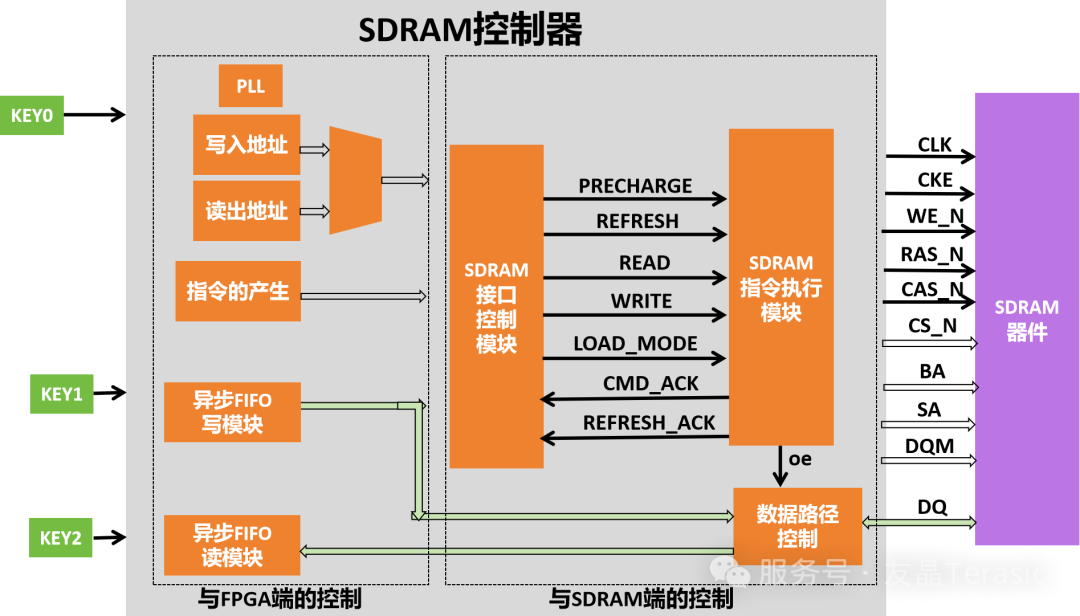

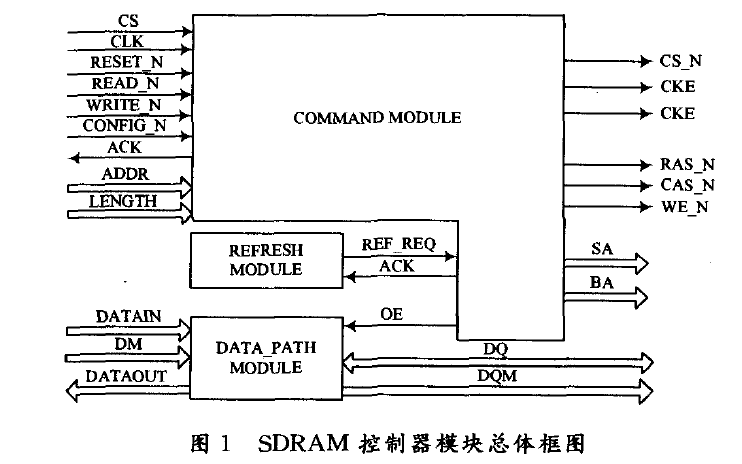

下圖是本案例的功能框圖。

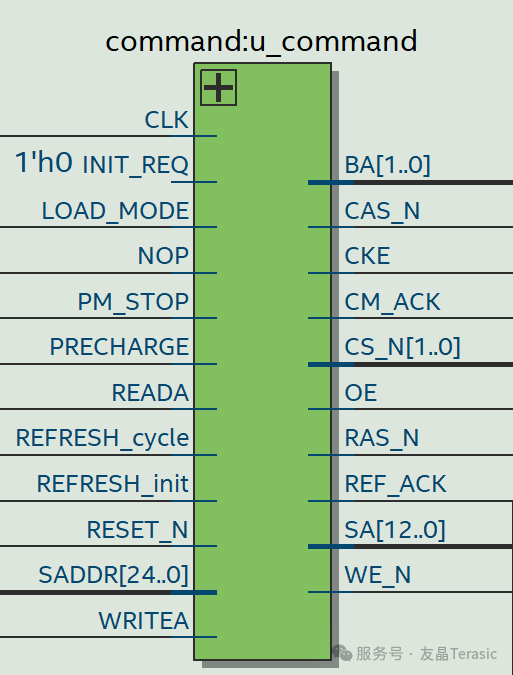

command.v文件對應圖中SDRAM指令執行模塊,它會從SDRAM接口控制模塊接收指令,然后產生控制信號直接輸出到SDRAM器件來完成所接收指令的動作。如下是該模塊的RTL視圖:

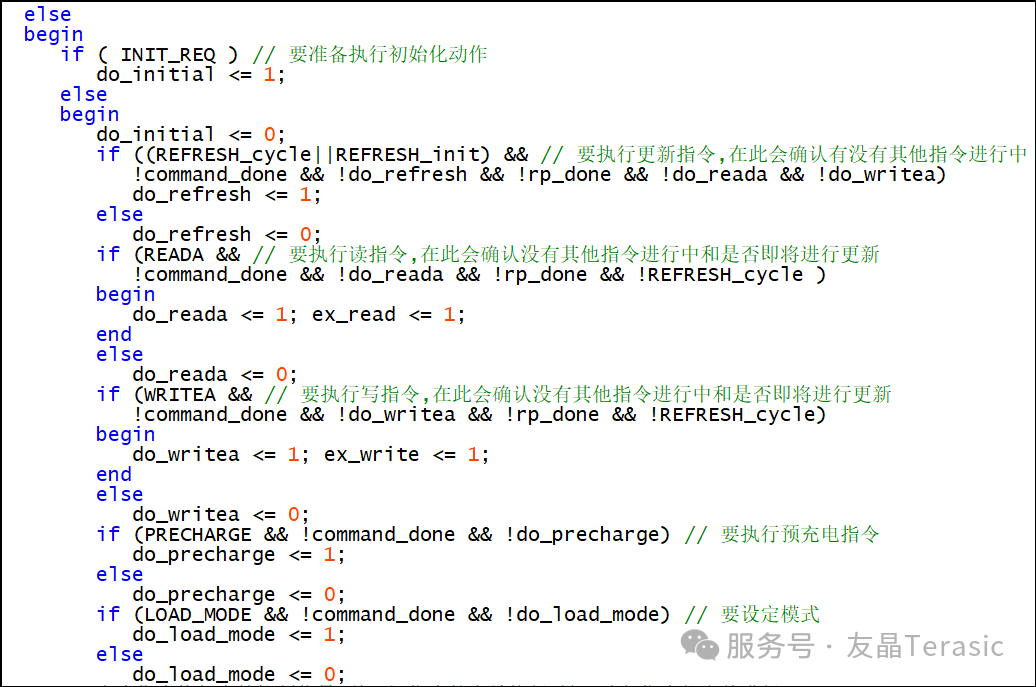

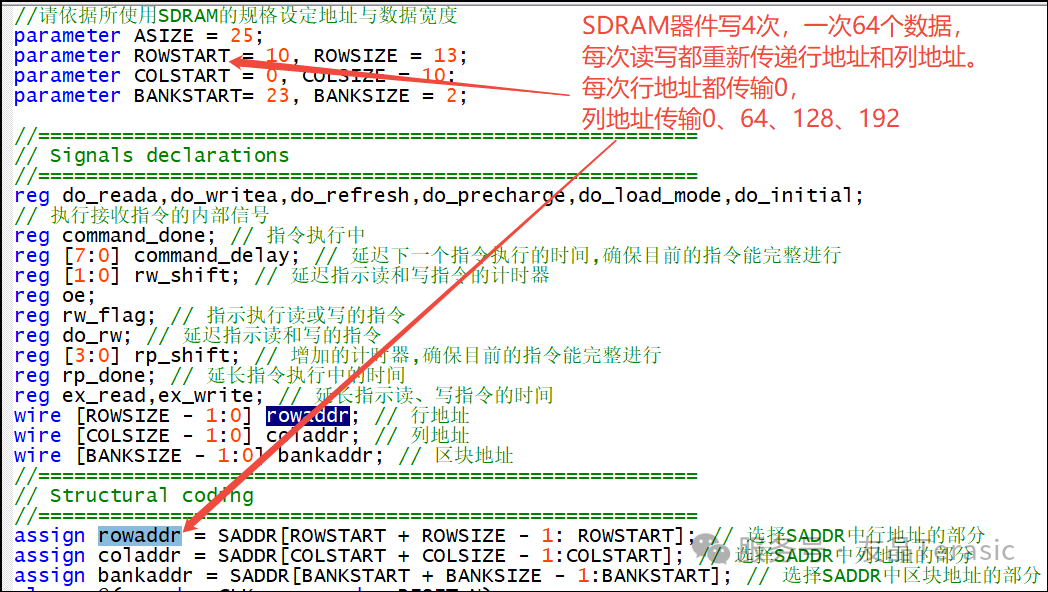

其具體代碼講解如下:

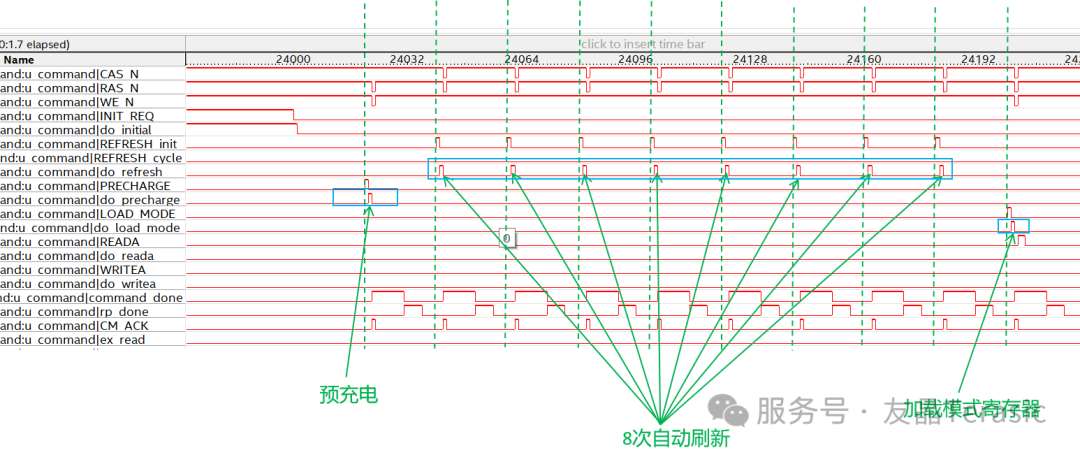

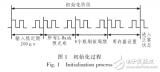

輸入信號INIT_REQ指示的是SDRAM上電等待的24000個時鐘周期,在這期間do_initial信號為高,系統只能發送NOP命令。

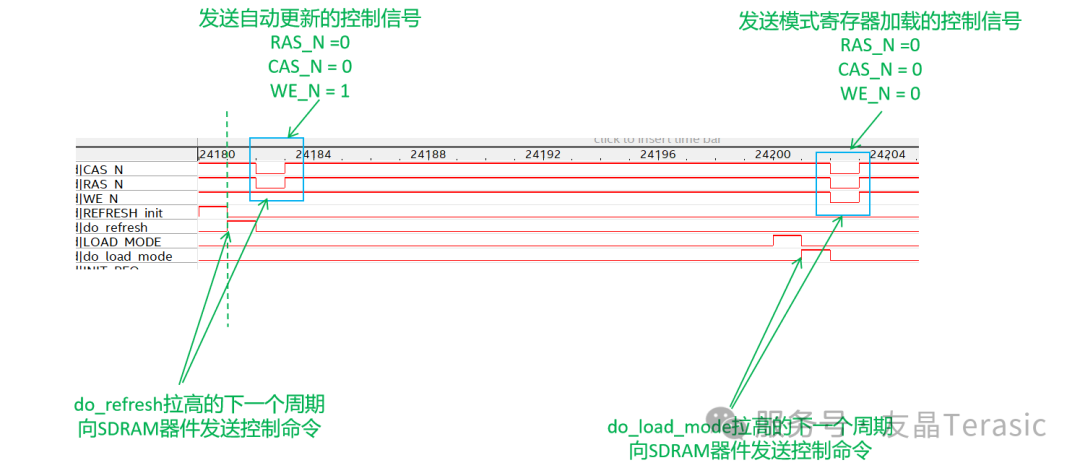

當初始化等待時間結束do_initial被拉低,首先確認在沒有其他指令進行中時,若有刷新請求,則do_refresh信號拉高。

然后確認在沒有其他指令進行中時,有讀請求時,do_reada信號拉高。

然后確認在沒有其他指令進行中時,有寫請求時,do_writea信號拉高。

然后確認在沒有其他指令進行中時,有預充電請求時,do_precharge信號拉高。

然后確認在沒有其他指令進行中時,有模式寄存器加載請求時,do_load_mode信號拉高。

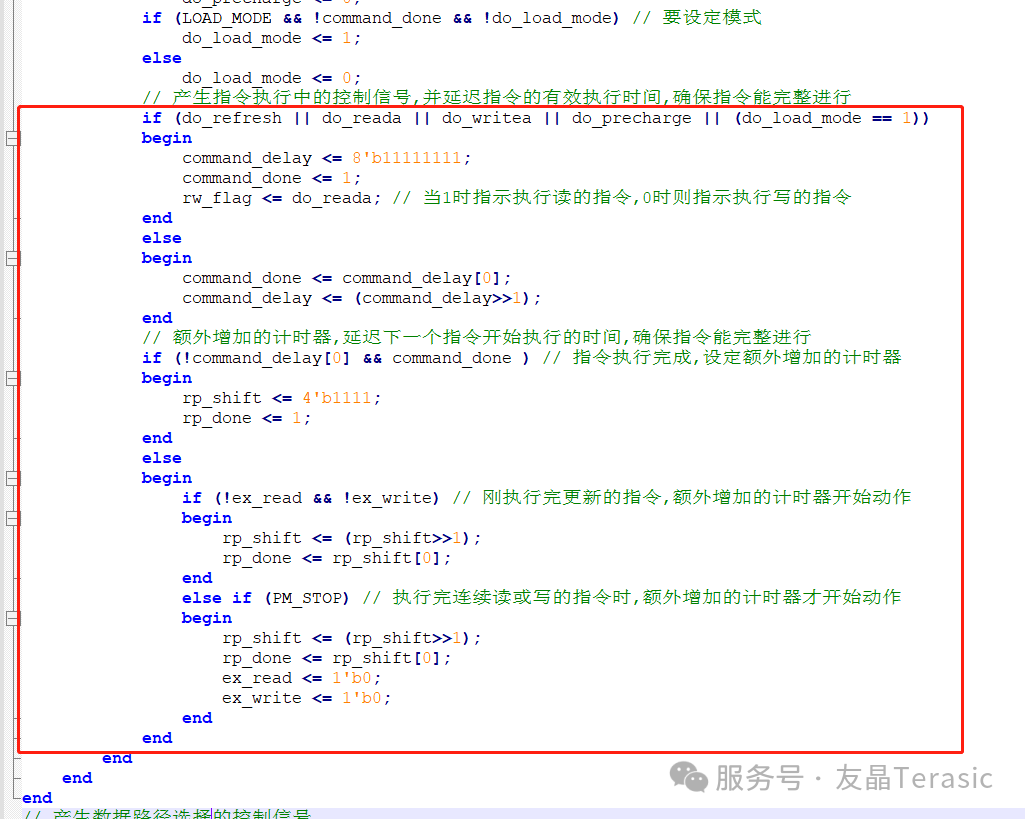

當產生自動刷新命令、讀寫命令、預充電命令和模式加載命令時,系統會通過command_delay來延遲指令的有效執行時間,確保指令能完整進行。除開突發讀/寫的情況,其他每個指令統一延遲8個時鐘周期后再延遲4個周期。

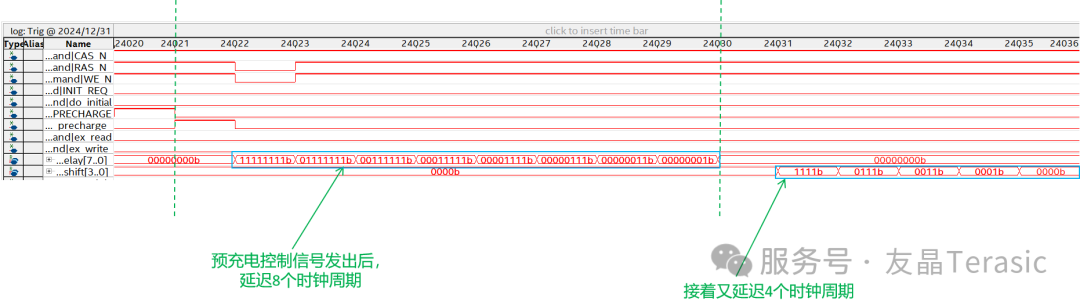

拿預充電命令舉例:

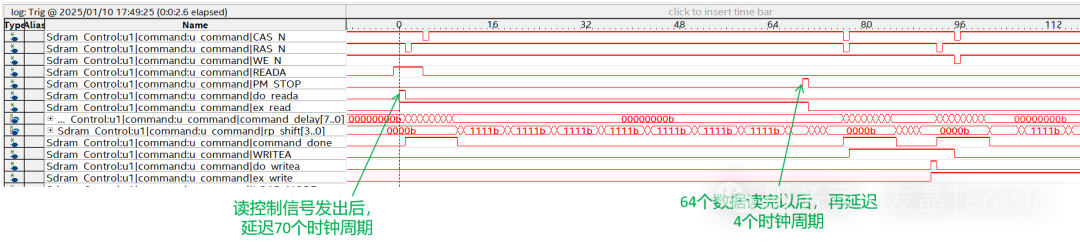

讀寫命令則是等待64個數據連續讀/寫完后,再延遲4個時鐘周期。拿讀命令舉例:

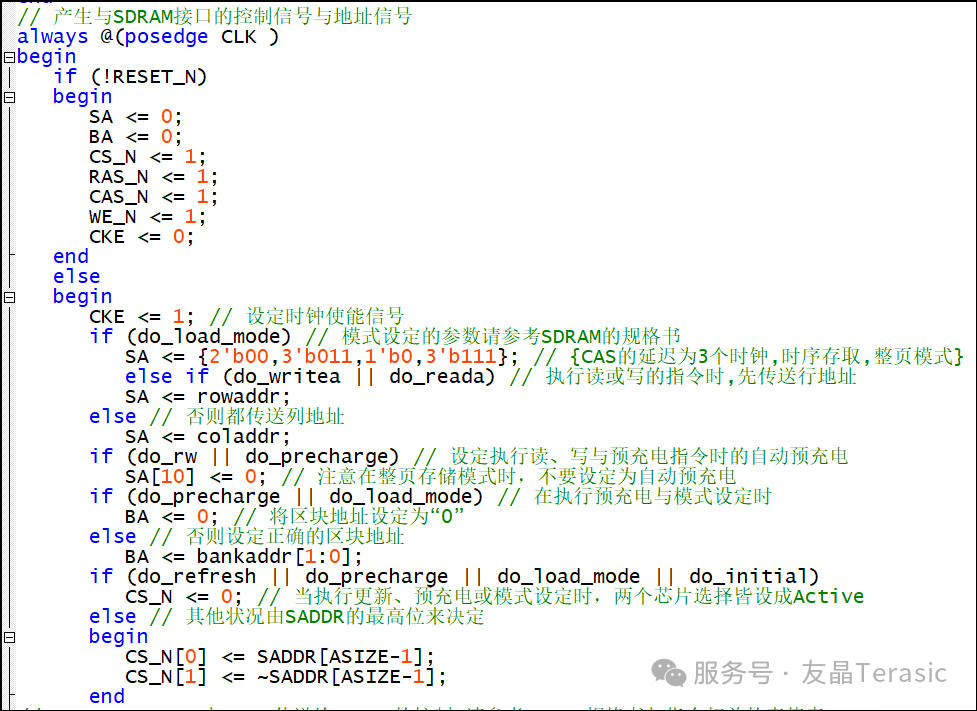

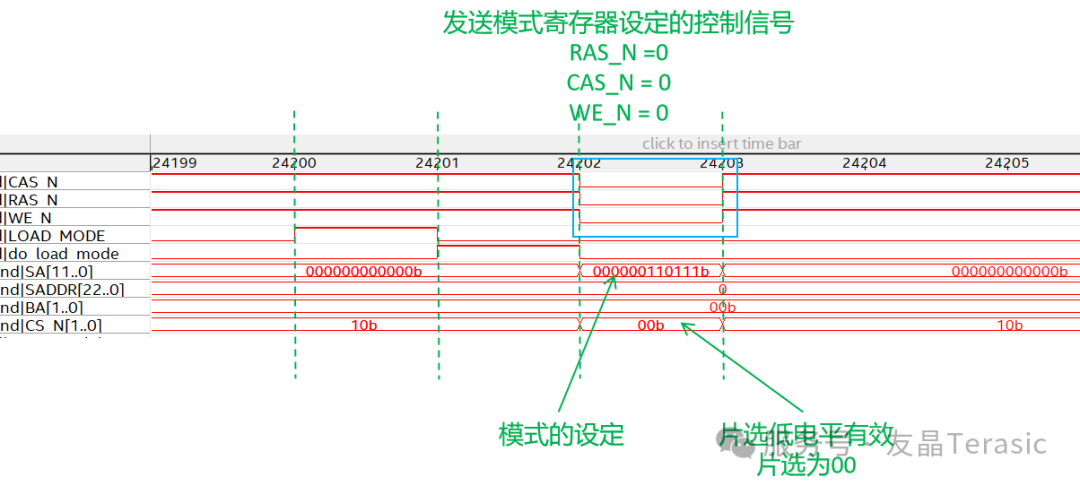

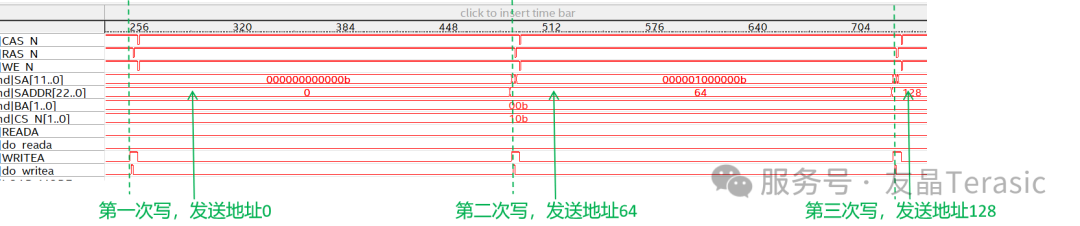

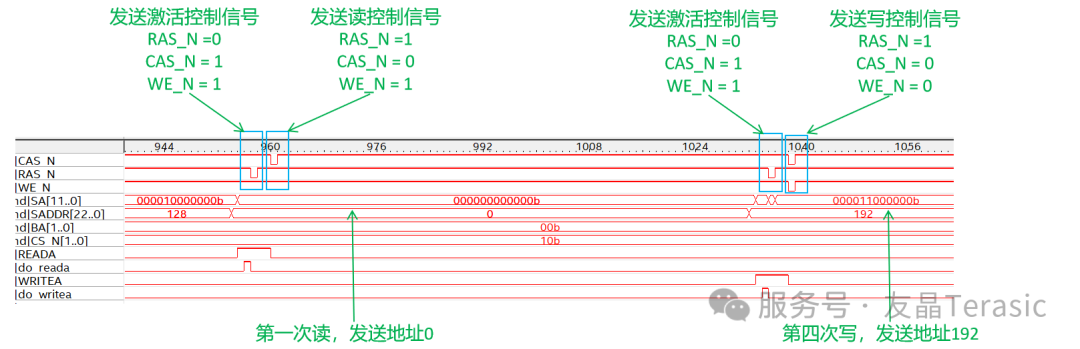

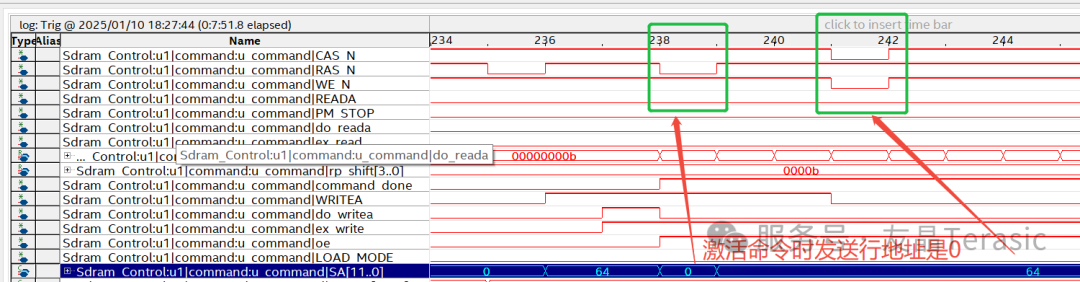

下面是地址端口、bank選擇和片選信號的處理。在初始化狀態,加載模式寄存器時是通過地址端口對寄存器進行賦值的。在激活操作時,地址端口發送行地址;在讀或者寫操作時,地址端口發送列地址。

command.v 模塊里面得到行地址rowaddr和列地址coladdr:

放大地址線SA波形可以看到,在行激活的時候發送的地址確實是0:

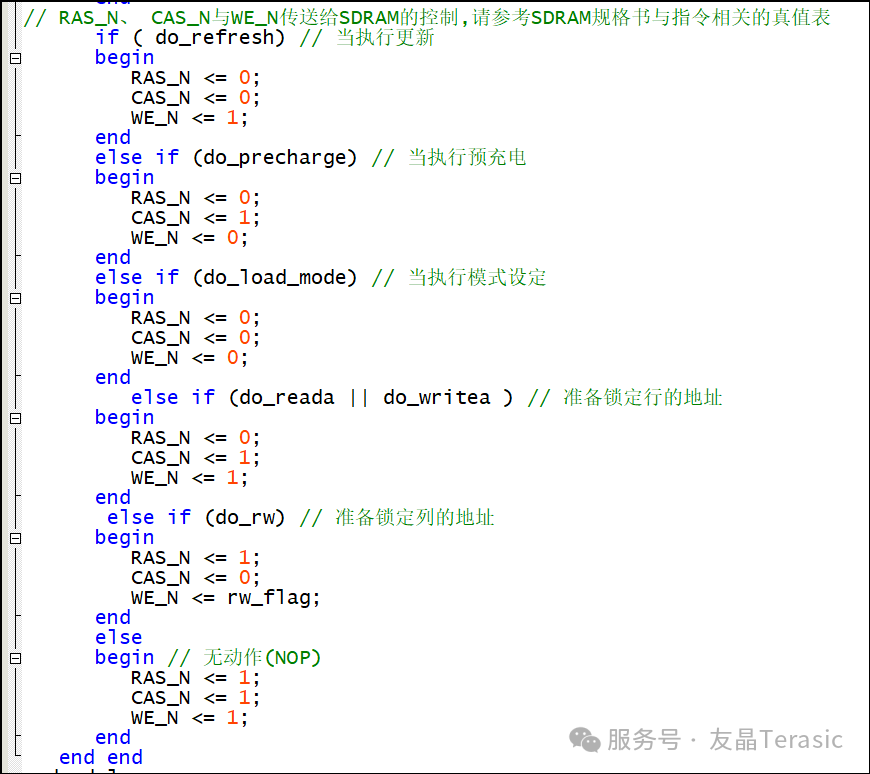

下面是RAS_N、CAS_N、WE_N信號的產生。

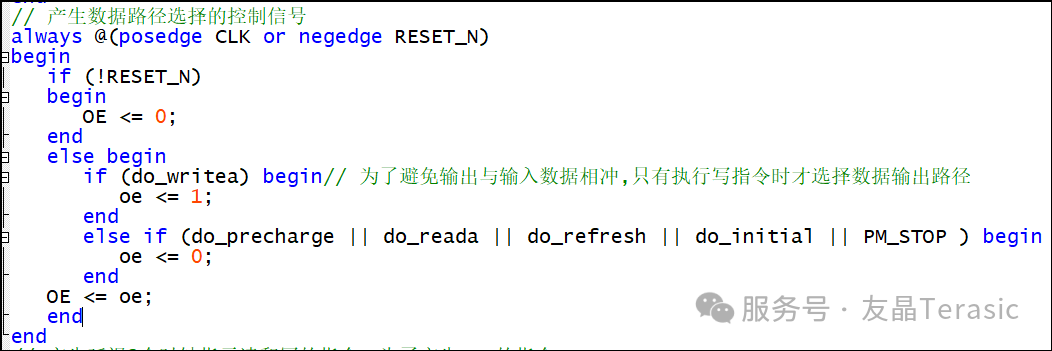

因為寫入 SDRAM 的數據與從 SDRAM 讀出的數據為共用傳輸引腳,為避免存取數據相沖,系統里設計了一個三態門電路(三態門電路的設計參考07-SDRAM控制器的設計——Sdram_Control.v代碼解析(后續發布),通過oe信號控制SDRAM 數據接口的輸入和輸出。oe信號的設計如下:

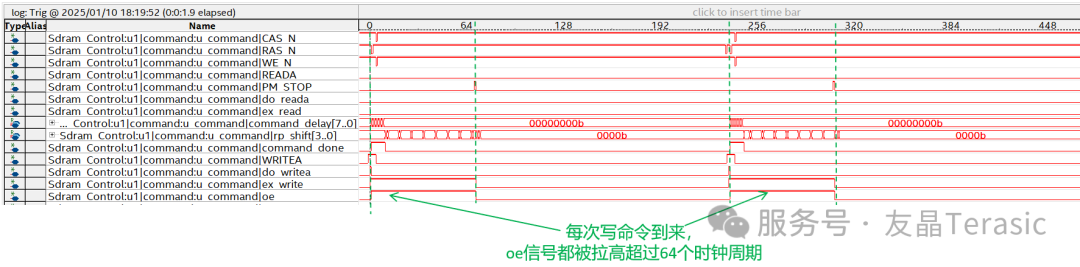

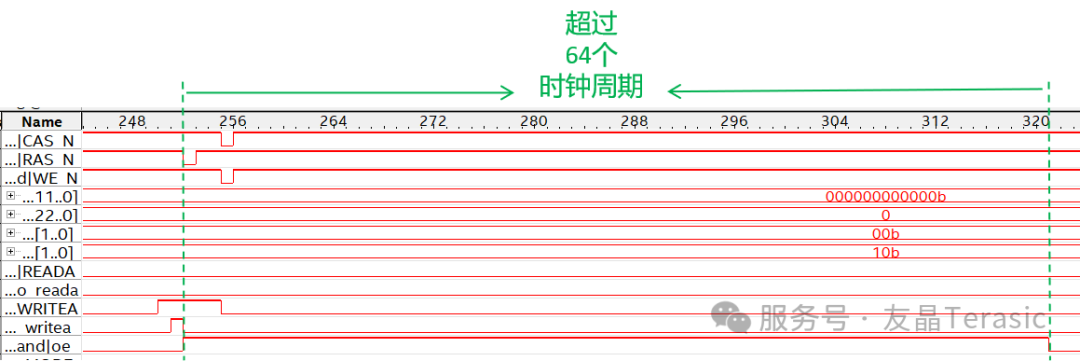

每次oe信號拉高超過64個時鐘周期,確保數據被正確寫入到SDRAM器件當中:

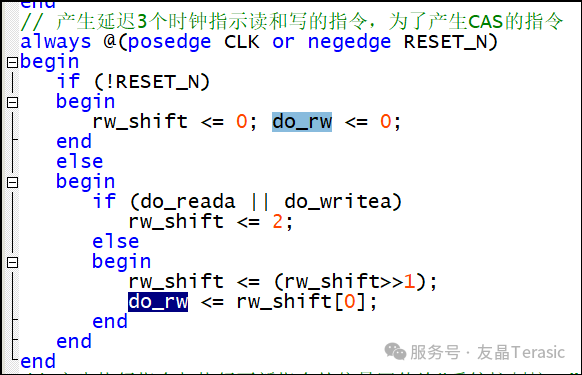

另外,讀命令和寫命令之前要先有激活命令,讀寫命令在激活命令的3個周期后發出,所以這里用個右移計數器計數3個周期:

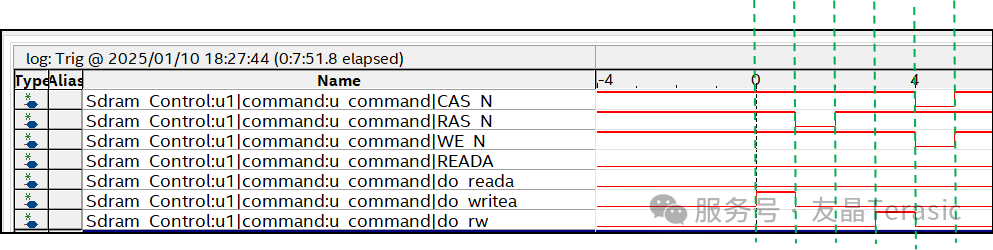

do_wr信號波形如下:

PS: 本文波形來自文件~sdramcontroloutput_filescommand.stp。

-

控制器

+關注

關注

113文章

16551瀏覽量

180245 -

SDRAM

+關注

關注

7文章

437瀏覽量

55509 -

接口

+關注

關注

33文章

8766瀏覽量

152304 -

指令

+關注

關注

1文章

614瀏覽量

35913 -

代碼

+關注

關注

30文章

4856瀏覽量

69435

原文標題:05-SDRAM控制器的設計——command.v代碼解析

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SDRAM控制器的設計——Sdram_Control.v代碼解析(異步FIFO讀寫模塊、讀寫SDRAM過程)

【開源騷客】《輕松設計SDRAM控制器》第八講—命令解析模塊講解

SDRAM控制器參考設計,Lattice提供的VHDL源代碼

使用Verilog實現基于FPGA的SDRAM控制器

SDRAM控制器的設計

FPGA讀寫SDRAM的實例和SDRAM的相關文章及一些SDRAM控制器設計論文

如何使用FPGA設計SDRAM控制器

SDRAM控制器設計之command.v代碼解析

SDRAM控制器設計之command.v代碼解析

評論