DDR內存控制器是一個高度集成的組件,支持多種DDR內存類型(DDR2、DDR3、DDR3L、LPDDR2),并通過精心設計的架構來優化內存訪問效率。

DDR內存控制器架構

AXI內存端口接口(DDRI):該部分負責處理與多個AXI主設備之間的通信。通過四個64位的同步AXI接口,DDRI能夠同時服務多個AXI主設備,每個接口都配備了專用的交易FIFO,以確保數據的高效傳輸和緩存。

核心控制器與事務調度器(DDRC):DDRC是DDR內存控制器的核心,它包含兩個32條目的內容可尋址存儲器(CAMs),用于執行DDR數據服務調度,以最大化DDR內存的效率。此外,它還提供了低延遲的飛線通道(fly-by channel),允許直接訪問DDR內存而無需經過CAM,從而進一步減少延遲。

數字PHY控制器(DDRP):DDRP負責處理來自控制器的讀寫請求,并將這些請求轉換為符合目標DDR內存時序約束的特定信號。這些信號通過數字PHY連接到DDR引腳,最終與DDR設備通過PCB信號跡線直接相連。

訪問機制

AXI端口分配:系統通過DDRI的四個64位AXI內存端口訪問DDR內存。其中,一個端口專用于CPU和ACP的L2緩存,兩個端口專用于AXI_HP接口,第四個端口則由AXI互連上的所有其他主設備共享。

仲裁機制:DDRI負責仲裁來自八個端口(四個讀端口和四個寫端口)的請求。仲裁器基于請求的等待時間、請求的緊急程度以及請求是否與前一個請求在同一頁面內等因素來選擇請求,并將其傳遞給DDR控制器和事務調度器(DDRC)。

讀寫流程:讀寫請求通過DDRC的單一接口傳遞。讀請求包括一個標簽字段,該字段與從DDR返回的數據一起返回,以便于數據的匹配和確認。DDR控制器PHY(DDRP)則負責驅動DDR事務的完成。

整個DDR內存控制器通過精心設計的接口和調度機制,實現了對多種DDR內存類型的支持,并優化了內存訪問的效率和性能。無論是通過AXI接口的并行處理能力,還是通過DDRC和DDRP的精細調度和物理層處理,都確保了系統能夠高效、可靠地訪問DDR內存。

DDRI

DDR Controller System Interface (DDRI) 是一個關鍵組件,它連接了處理器或主設備與DDR內存系統,提供了高效、靈活的數據傳輸和控制機制。以下是DDRI的一些核心特性詳解:

四個相同的64位AXI端口:DDRI提供了四個獨立的64位AXI端口,每個端口都支持INCR(遞增)和WRAP(回環)兩種突發類型。這使得系統能夠同時處理來自多個主設備的讀寫請求,提高了數據傳輸的并行性和效率。

獨立的讀寫端口和32位尋址:每個64位AXI接口都包含獨立的讀寫端口,這有助于優化數據傳輸流程,減少沖突。同時,使用32位尋址允許訪問大量的內存地址空間。

寫數據字節使能支持:對于每個數據節拍(beat),DDRI支持寫數據字節使能(write data byte enable),這意味著可以僅更新數據總線上的特定字節,而不是整個數據字,從而提高了寫操作的靈活性和效率。

復雜的仲裁方案:為了防止數據饑餓(即某些主設備長時間無法獲得訪問權),DDRI采用了復雜的仲裁方案。這些方案可以根據請求的優先級、等待時間等因素來公平地分配訪問權。

低延遲路徑:DDRI提供了一個低延遲路徑,使用緊急位(urgent bit)來繞過仲裁邏輯,允許高優先級的請求快速獲得訪問權。

深度讀寫命令接受能力:DDRI具有深度讀寫命令隊列,能夠同時接受并處理多個讀寫命令,提高了系統的吞吐量和響應速度。

亂序讀數據返回:對于來自不同主設備ID的請求,DDRI可以亂序返回讀數據。這有助于優化數據傳輸流程,減少等待時間。

九位AXI ID信號:所有端口上的AXI ID信號均為九位,這允許系統支持更多的主設備,提高了系統的可擴展性。

靈活的突發長度和大小:DDRI支持從1到16個數據節拍的突發長度,以及1、2、4、8字節每節拍的突發大小。這提供了靈活的數據傳輸選項,以適應不同的應用場景。

不支持鎖定訪問:DDRI不支持從任何AXI端口發起鎖定訪問(locked accesses),這有助于簡化系統設計并減少潛在的沖突。

低延遲讀機制:通過使用HPR(高優先級讀)隊列,DDRI實現了低延遲讀機制,可以更快地響應高優先級讀請求。

特殊緊急信號:DDRI向每個端口發送特殊緊急信號,以便在需要時快速響應高優先級請求。

TrustZone區域可編程:DDRI支持在64MB邊界上編程TrustZone區域,這有助于實現安全分區,保護敏感數據不被未授權訪問。

獨占訪問:對于每個端口,DDRI支持兩個不同ID的獨占訪問。然而,需要注意的是,不支持跨不同端口的獨占訪問,且不支持鎖定事務。

這些特性共同構成了DDRI的強大功能,使得DDR內存系統能夠高效地支持各種復雜的應用場景。

DDRP

DDR Controller PHY (DDRP) 是DDR內存控制器中的物理層接口,它負責處理與DDR內存模塊之間的物理信號傳輸。DDRP 的特性直接關系到內存訪問的速度、穩定性和效率。以下是DDRP的一些關鍵特性:

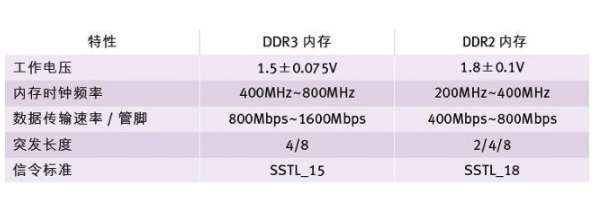

兼容多種DDR I/O電壓:DDRP支持多種DDR接口電壓標準,包括1.2V的LPDDR2、1.8V的DDR2、以及1.5V的DDR3和1.35V的DDR3L。這種兼容性使得DDRP能夠適配不同版本的DDR內存,增強了系統的靈活性和擴展性。

可選的16位和32位數據總線寬度:DDRP支持配置為16位或32位的數據總線寬度。這種靈活性允許系統設計者根據具體的性能需求和內存容量來選擇合適的總線寬度,以達到最佳的系統性能。

可選的ECC在16位數據寬度配置中:在16位數據寬度配置下,DDRP支持可選的錯誤檢查與糾正(ECC)功能。ECC能夠檢測并糾正數據傳輸中的錯誤,提高數據的完整性和可靠性。

軟件控制的自刷新進入和命令到達時的自動退出:DDRP支持通過軟件命令進入自刷新模式,以在不需要訪問內存時降低功耗。當新的命令到達時,DDRP會自動退出自刷新模式,準備處理新的內存訪問請求。

基于可編程空閑周期的自主DDR掉電進入和退出:DDRP能夠根據預設的空閑周期自動進入和退出DDR掉電模式。這種自主管理功能有助于進一步降低系統功耗,特別是在系統負載較低時。

數據讀選通(strobe)自動校準:為了確保數據傳輸的準確性和穩定性,DDRP支持數據讀選通自動校準功能。該功能能夠自動調整讀選通信號的相位和時序,以匹配數據信號的邊緣,從而減少數據傳輸中的錯誤和失真。

這些特性共同構成了DDRP的強大功能,使得DDR內存控制器能夠高效地與DDR內存模塊進行通信,確保數據的快速、準確和可靠傳輸。通過優化DDRP的配置和使用,可以顯著提高系統的整體性能和穩定性。

DDRC

DDR Controller Core and Transaction Scheduler (DDRC) 是DDR控制器中的核心組件,它主要負責管理內存事務的調度和執行,以確保數據的高效傳輸和訪問。

高效的事務調度以優化數據帶寬和延遲

DDRC通過智能地調度內存訪問請求,使得數據能夠在CPU、圖形處理器或其他系統組件之間高效傳輸。它能夠識別并優先處理高優先級或緊急的數據傳輸請求,從而最大化數據帶寬的利用率。通過精細控制事務的執行順序和時間,DDRC能夠減少數據訪問的延遲。它可以根據系統的實時需求動態調整調度策略,確保關鍵數據的快速訪問。

先進的重排序引擎以最大化內存訪問效率

對于連續讀寫操作,DDRC的重排序引擎能夠識別并重新排列內存訪問請求,以減少DRAM的頁面切換和激活延遲。這通過減少不必要的DRAM操作來提高整體訪問效率。

對于隨機讀寫操作,DDRC能夠利用重排序引擎來合并相鄰的內存訪問請求,從而減少內存總線的負載并提高訪問效率。這種優化對于處理來自多個處理器或系統組件的隨機訪問請求尤為重要。

讀寫地址沖突檢測以避免數據損壞

DDRC在調度內存訪問請求時,會檢查讀寫地址是否存在沖突。如果發現沖突(即同一地址在同一時間被不同的讀寫請求訪問),它會暫停或重新調度相關請求,以避免數據損壞或不一致性。除了地址沖突檢測外,DDRC還可能包含其他保護機制,如錯誤糾正碼(ECC)等,以確保數據的完整性和可靠性。

遵守AXI排序規則

DDRC通常與AXI總線接口緊密集成,以支持高級別的數據傳輸和控制。它必須遵守AXI協議的排序規則,以確保不同主設備之間的數據訪問順序一致性和正確性。

在AXI協議中,事務ID(Transaction ID)用于標識和跟蹤內存訪問請求。DDRC需要管理這些事務ID,以確保它們按照正確的順序被處理和返回給請求者。

綜上所述,DDRC及其交易調度器是DDR控制器中的關鍵組件,它們通過高效的事務調度、先進的重排序引擎、讀寫地址沖突檢測以及遵守AXI排序規則等特性,確保了數據的高效傳輸和訪問。這些特性對于提高系統性能、降低延遲和保護數據完整性至關重要。

方框圖

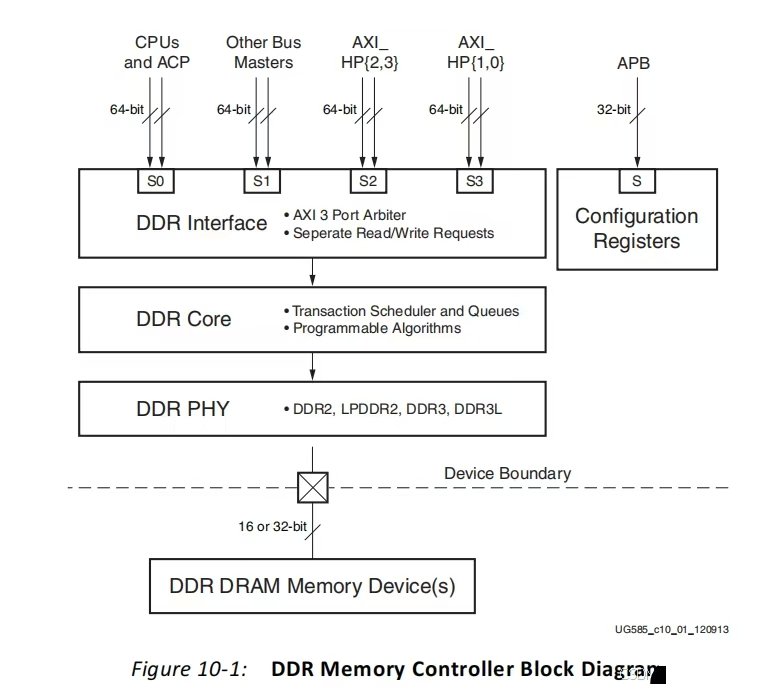

DDR內存控制器的框圖如下圖所示。DDR內存控制器由一個仲裁器、一個帶有事務調度器的內核和DDR內存信號的物理排序組成。

控制器核心和事務調度器中包含兩個32條目的CAMs(內容可尋址存儲器),用于執行DDR數據服務重排序。這種重排序機制旨在最大化DDR內存訪問的效率,特別是對于連續讀寫和隨機讀寫操作。通過重新排列內存訪問請求的順序,可以減少DRAM的頁面切換和激活延遲,從而提高整體性能。除了通過CAM進行重排序外,該控制器還包含一個Fly-by通道,允許某些內存訪問請求繞過CAM進行低延遲訪問。這對于需要快速響應的關鍵任務特別有用,因為它們可以更快地訪問DDR內存而無需等待CAM的重排序過程。

PHY(物理層)負責處理來自控制器的讀寫請求,并將這些請求轉換為符合目標DDR內存時序約束的特定信號。這些信號包括時鐘信號、命令信號、地址信號和數據信號等,它們共同構成了DDR內存操作的完整序列。PHY使用來自控制器的信號來產生內部信號,這些內部信號通過PHY連接到PS的焊盤(pads)。這些焊盤直接通過PCB信號跡線連接到外部內存設備,從而實現DDR內存與處理器系統之間的物理連接。

仲裁器負責跨四個AXI端口進行仲裁,以確定哪個端口可以訪問DDR核心。仲裁是基于優先級的,允許系統根據當前的任務需求和資源利用率來動態調整各個端口的訪問權限。此外,仲裁器還支持通過緊急機制來提升某些任務的優先級,以確保關鍵任務能夠及時獲得DDR內存的訪問權限。

注意事項:

通常情況下,CLG225系列設備支持32位和16位兩種數據總線寬度選項。這意味著大多數CLG225設備可以根據系統需求配置為使用32位或16位的數據總線,以適應不同的數據傳輸速率和帶寬要求。

然而,對于7z007s單核心和7z010雙核心這兩款特定的CLG225設備,它們的數據總線寬度支持受到了限制。這兩款設備僅支持16位數據總線寬度,而不支持32位數據總線。這意味著在設計和使用這兩款設備時,需要特別注意它們的數據傳輸能力和系統接口兼容性,確保它們能夠與其他系統組件正確協作。

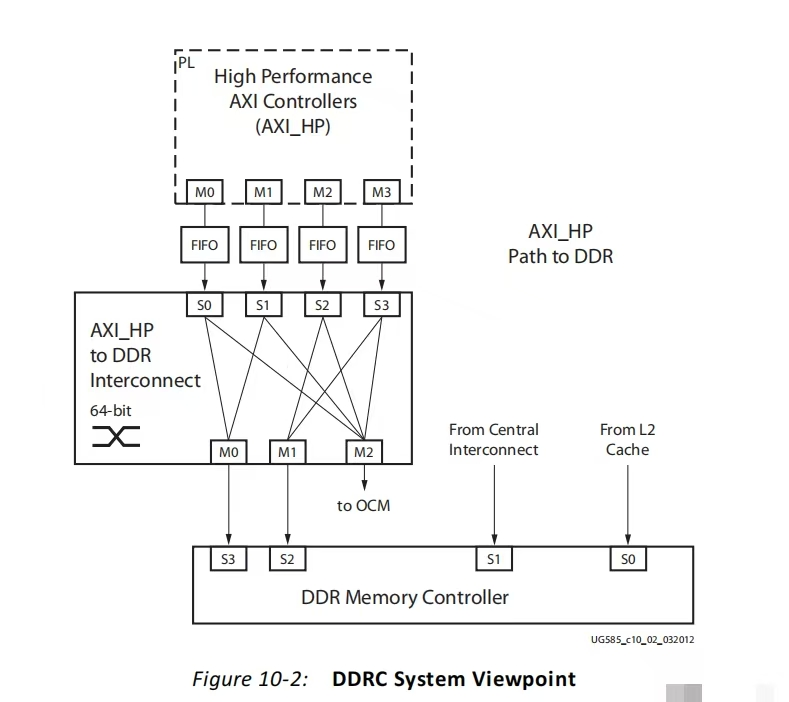

AXI的互聯系統

該系統在處理器與DDR內存之間提供高效的數據傳輸。這里詳細說明了AXI_HP(高性能)接口、DDR內存端口仲裁器、互聯開關、QoS(服務質量)信號以及L2緩存的連接和配置方式。

AXI_HP接口:有四個AXI_HP接口,它們被成對復用,并連接到圖10-2中所示的端口2和端口3。這些端口通常配置為高帶寬流量使用,以支持大量數據的快速傳輸。

DDR內存端口仲裁器:從這四個AXI_HP接口到DDR內存的路徑包括DDR內存端口仲裁器上的兩個端口。互聯開關負責在這兩個端口之間進行雙向仲裁,以決定何時允許哪一側進行數據傳輸。

讀/寫通道分離:在互聯系統中,讀和寫通道是分開操作的,這意味著它們可以獨立地管理數據的讀取和寫入,從而提高數據傳輸的效率。

QoS(服務質量)仲裁:互聯橋接器中的仲裁受到來自每個PL接口的QoS信號的影響。具有更高QoS值的請求者會被互聯橋接器優先處理。這種基于優先級的仲裁機制確保了關鍵任務或高優先級的數據傳輸能夠優先進行。

LRG方案:在QoS值相同的情況下,即出現優先級相同的情況時,會使用LRG(可能是指某種負載均衡或隨機選擇)方案來打破這種平局,確保公平性和系統的穩定性。

L2緩存:L2緩存連接到端口0,并用于服務CPU和PL的ACP(加速器一致性端口)接口。這個端口通常配置為低延遲,以快速響應CPU和ACP的數據請求。

其他AXI主設備:AXI互聯上的其他主設備(如其他處理器或外設)連接到端口1,這些設備通過AXI互聯與DDR內存、L2緩存等資源進行通信。

總的來說,這個互聯系統通過高效的仲裁機制、QoS支持和緩存技術,為處理器和DDR內存之間提供了高性能、低延遲的數據傳輸路徑。

原文連接:https://tencentcloud.csdn.net/678a2060edd0904849a677be.html

-

FPGA

+關注

關注

1644文章

21989瀏覽量

615208 -

控制器

+關注

關注

114文章

17022瀏覽量

183275 -

接口

+關注

關注

33文章

8967瀏覽量

153344 -

Zynq

+關注

關注

10文章

614瀏覽量

48081 -

DDR內存

+關注

關注

0文章

21瀏覽量

7132

原文標題:Zynq7000系列FPGA中的DDR內存控制器

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

PrimeCell DDR2動態內存控制器(PL341)循環模型9.1.0版用戶指南

DDR內存接口的設計與實現

利用DDR控制器讀取重排序緩沖器,將DRAM帶寬提高十倍

基于FPGA的DDR3協議解析邏輯設計

TMS320DM646x數字媒體系統DMSoC的DDR2存儲控制器詳細介紹

DDR SDRAM控制器的設計與實現

完整的DDR、DDR2和DDR3內存電源解決方案同步降壓控制器數據表

完整的DDR2、DDR3和DDR3L內存電源解決方案同步降壓控制器TPS51216數據表

DDR內存控制器的架構解析

DDR內存控制器的架構解析

評論