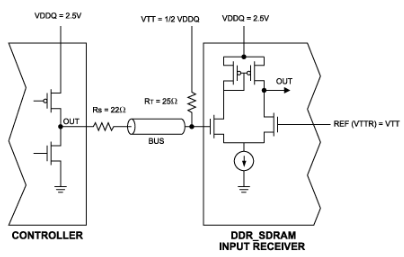

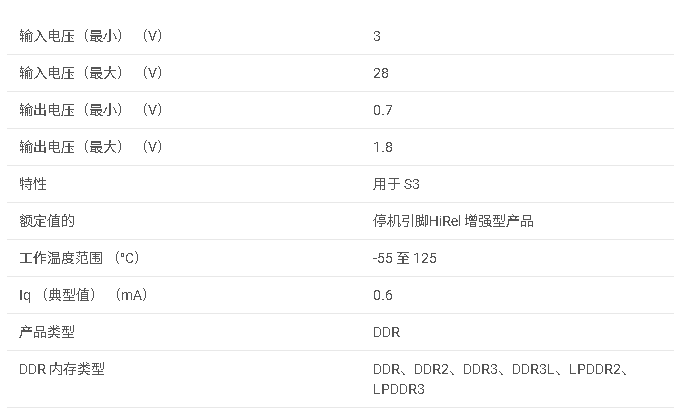

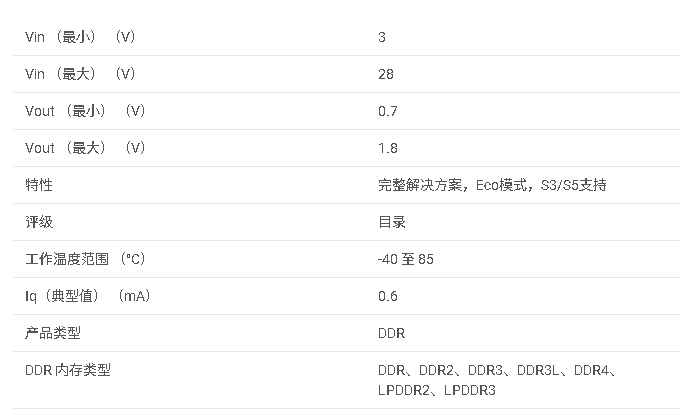

DDR內(nèi)存由于其快速的數(shù)據(jù)傳輸速率和成本而在服務(wù)器和個(gè)人計(jì)算機(jī)中變得非常流行。DDR 內(nèi)存需要主內(nèi)存電源(也稱為 VDD)和跟蹤端接電源 VTT。MAX1917為多功能快速PWM降壓控制器,能夠灌入和拉出高達(dá)25A的電流。本應(yīng)用筆記說(shuō)明了MAX1917用作服務(wù)器DDR存儲(chǔ)器的VDD電源。

MAX1917為PWM控制器,為DDR存儲(chǔ)器產(chǎn)生終止電源(VTT)。在此類應(yīng)用中,輸出電壓 VTT 跟蹤 DDR 內(nèi)存電源電壓 VDD,并將其饋送到 DDR 引腳。

MAX1917還可用于從5V或12V輸入電源產(chǎn)生VDDQ電源電壓,方法是將其基準(zhǔn)電壓連接到DDR引腳。圖1所示為12A輸出電流的原理圖。

圖1.MAX1917用于VDDQ電源電壓應(yīng)用。

MAX1917可用于輸出電壓為1.0V及以上的非跟蹤應(yīng)用,如處理器內(nèi)核電壓和DSP內(nèi)核電壓。MAX1917的優(yōu)點(diǎn)之一是瞬態(tài)響應(yīng)快(在一個(gè)開關(guān)周期內(nèi)響應(yīng)階躍負(fù)載變化)。因此,它適用于高速應(yīng)用。以下應(yīng)用電路的另一個(gè)特點(diǎn)是,通過(guò)改變R200的值,開關(guān)頻率可以在1kHz至6MHz之間設(shè)置。此功能可優(yōu)化外部組件選擇。

表 1 列出了組件信息。

| Comp. | 描述 | 供應(yīng)商 |

| C1 | 1.0μF/25V 陶瓷電容,TMK316BJ105ML,最大 20mΩ ESR。 | Taiyo Yuden |

| C2 | 4X330μF/25V 鋁電容,ZA 系列,最大 26mΩ ESR。 | Rubycon |

| C3 | 4.7μF/10V 陶瓷電容, JMK212BJ475MG, 20mΩ ESR 最大值 | Taiyo Yuden |

| C4 | 0.47μF/10V 陶瓷電容器, LMK107BJ474MA | Taiyo Yuden |

| C5 | 10μF/6.3V 陶瓷電容, JMK316BJ106ML, 最大 ESR 20mΩ | Taiyo Yuden |

| C6 | 每個(gè)電容器 3X560μF、4SP560M、14mΩ 最大 ESR。 | Sanyo |

| C7 | 0.22μF/10V 陶瓷電容器, LMK107BJ224MA | Taiyo Yuden |

| D1 | 30V/100mA肖特基二極管,CMPSH-3 | Central Semi. |

| L1 | 0.75μH/24A, CDEP149-0R7NC, (靜電比, 最大 1.2mΩ) | Sumida |

| 第一季度 | 紅外代碼編號(hào): IRF7822 | IR |

| 第一季度 | 2XIRF7822 | IR |

| 第一季度 | 2N7002K | Siliconix |

| R1 | 400k, 1% | |

| R2 | 5.1k, 5% | |

| R3 | 20k, 5% | |

| R4 | 15k, 0.1% | |

| R5 | 10k, 0.1% | |

| R6* | 1.78k, 1% | |

| *參見公式(2)。 | ||

設(shè)置輸出電壓

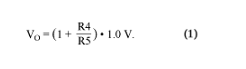

根據(jù)圖1所示的原理圖,反饋基準(zhǔn) 電壓設(shè)置為1.0V。輸出電壓可在 1.0V 和 向上。輸出電壓由下式確定:

設(shè)置開關(guān)頻率

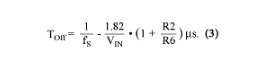

MAX1917/8的開關(guān)頻率可設(shè)置為300kHz 或 550kHz,通過(guò)保持 FSEL 引腳懸空或?qū)⑵浣拥亍?但是,開關(guān)頻率可以設(shè)置在 300kHz 至 1MHz,通過(guò)增加一個(gè)電阻(R6)。給出實(shí)際開關(guān)頻率 由

要使上述公式成立,F(xiàn)SEL引腳應(yīng)接地。相應(yīng)的關(guān)閉時(shí)間由下式給出,

開關(guān)頻率與輸入電壓無(wú)關(guān)。但是,關(guān)斷時(shí)間取決于輸入電壓。MAX1917的最小關(guān)斷時(shí)間為350ns(典型值),最大關(guān)斷時(shí)間為400ns。因此,在低輸入電壓(5V輸入)下選擇開關(guān)頻率時(shí)應(yīng)非常小心,以確保公式3中要求的關(guān)斷時(shí)間至少是滿足瞬態(tài)響應(yīng)要求的最小關(guān)斷時(shí)間的1.4倍。

圖2分別顯示了5V和12V輸入的轉(zhuǎn)換器效率與負(fù)載電流的函數(shù)關(guān)系。很明顯,該轉(zhuǎn)換器在負(fù)載電流小于12A時(shí)表現(xiàn)出非常高的效率。下圖(圖3a和3b)分別顯示了5V和12V輸入的輸出紋波電壓和低壓側(cè)MOSFET漏極至源極電壓波形。對(duì)于 25V 輸入,輸出紋波電壓保持在 5mV 以下,對(duì)于 50V 輸入,紋波電壓保持在 12mV 以下。在1V輸入時(shí),應(yīng)使用大輸出電感器(例如5.125μH,勝美達(dá)CEP1-5R1-H)來(lái)保持紋波電壓低于輸出電壓的12%。

圖2.效率與輸出負(fù)載電流的關(guān)系

圖 3a.輸出紋波電壓和低壓側(cè) MOSFET Vds 波形(輸入電壓為 5V)。

圖 3b.輸出紋波電壓和低側(cè)MOSFET Vds波形(12V輸入)。

審核編輯:郭婷

-

控制器

+關(guān)注

關(guān)注

114文章

17022瀏覽量

183276 -

PWM

+關(guān)注

關(guān)注

116文章

5432瀏覽量

218472 -

服務(wù)器

+關(guān)注

關(guān)注

13文章

9728瀏覽量

87439

發(fā)布評(píng)論請(qǐng)先 登錄

用于服務(wù)器插件卡 ASIC 內(nèi)核電源的 10A 降壓轉(zhuǎn)換器

基于TPS53219的用于服務(wù)器插件卡 ASIC 內(nèi)核電源的10A降壓轉(zhuǎn)換器包含BOM,原理圖和光繪文件

無(wú)處不在的DDR存儲(chǔ)器

回收服務(wù)器內(nèi)存條 收購(gòu)服務(wù)器內(nèi)存條

高價(jià)收購(gòu)服務(wù)器內(nèi)存條,服務(wù)器內(nèi)存條優(yōu)勢(shì)回收

Crucial推出的128GB DDR4內(nèi)存,密度最高的服務(wù)器內(nèi)存模塊

用于DDR-SDRAM終端的電源工作在3V至5.5V輸入電壓

完整的DDR、DDR2和DDR3內(nèi)存電源解決方案同步降壓控制器數(shù)據(jù)表

完整的DDR2、DDR3和DDR3L內(nèi)存電源解決方案同步降壓控制器TPS51216數(shù)據(jù)表

適用于VR13 CPU VCORE 和 DDR內(nèi)存的兩相 D-CAP+? 降壓控制器TPS53627數(shù)據(jù)表

TPS51216-EP 增強(qiáng)型產(chǎn)品 完整的 DDR2、DDR3 和 DDR3L 內(nèi)存電源解決方案 同步降壓控制器數(shù)據(jù)手冊(cè)

TPS51916 DDR2/3/3L/4 內(nèi)存電源解決方案同步降壓控制器數(shù)據(jù)手冊(cè)

VDDQ電源用于使用PWM降壓控制器的服務(wù)器DDR內(nèi)存

VDDQ電源用于使用PWM降壓控制器的服務(wù)器DDR內(nèi)存

評(píng)論