綜合(Synthesis)是指將RTL設(shè)計(jì)轉(zhuǎn)換為門(mén)級(jí)描述。Vivado開(kāi)發(fā)套件中的綜合工具是一款時(shí)序驅(qū)動(dòng)型、專(zhuān)為內(nèi)存使用率和性能優(yōu)化的綜合工具,支持System Verilog 2012、Verilog 2005、VHDL 2008、混合語(yǔ)言中的可綜合子集,以及XDC設(shè)計(jì)約束文件(基于工業(yè)標(biāo)準(zhǔn)的SDC文件),此外還支持RTL屬性來(lái)控制綜合細(xì)節(jié)。

綜合設(shè)置選項(xiàng)

在Flow Navigator中點(diǎn)擊Settings,切換到Synthesis標(biāo)簽中:

1.Constraints部分

選擇用于綜合的約束集,一個(gè)約束集是一組XDC約束文件,默認(rèn)選擇狀態(tài)為active的約束集。設(shè)計(jì)約束分兩種:

物理約束:定義管腳布局、單元(如塊RAM、查找表、觸發(fā)器等)布局的的絕對(duì)或相對(duì)位置;

時(shí)序約束:定義設(shè)計(jì)的頻率需求。如果沒(méi)有時(shí)序約束,Vivado會(huì)根據(jù)布線長(zhǎng)度和布局擁擠度優(yōu)化設(shè)計(jì)。

2.Options部分

選擇綜合運(yùn)行時(shí)使用的策略(strategy)。Vivado提供了幾種預(yù)定義的策略,后文將講述如何創(chuàng)建自定義策略。這里給出綜合策略中每個(gè)設(shè)置選項(xiàng)的含義:

flatten_hierarchy:定義綜合工具如何控制層次結(jié)構(gòu)(比如模塊之間的調(diào)用),選擇將所有層次展開(kāi)融為一體進(jìn)行綜合,還是分別獨(dú)立綜合再連接到一起。

none表示從不展開(kāi)層次結(jié)構(gòu),綜合輸出與原始RTL有相同的層次;

full表示全部展開(kāi)層次結(jié)構(gòu),只留下頂層;

rebuilt讓綜合工具展開(kāi)層次結(jié)構(gòu)后進(jìn)行綜合,綜合后再按原始RTL重建層次結(jié)構(gòu)。這樣既保留了跨界優(yōu)化的好處,又讓最終層次結(jié)構(gòu)與RTL類(lèi)似,便于分析。

gated_clock_conversion:選擇是否將門(mén)控時(shí)鐘轉(zhuǎn)換為使能信號(hào)。設(shè)計(jì)中應(yīng)該避免使用門(mén)控時(shí)鐘,需要的時(shí)鐘信號(hào)應(yīng)盡可能由MMCM/PLL產(chǎn)生。轉(zhuǎn)換過(guò)程需要與RTL屬性配合工作,具體在第24篇介紹。

bufg:設(shè)置綜合工具可以從設(shè)計(jì)中推斷出多少個(gè)BUFG。比如使用默認(rèn)的12時(shí),如果RTL中實(shí)例化了3個(gè)BUFG,那么綜合工具最多還可以推測(cè)出9個(gè)沒(méi)有明確實(shí)例化的BUFG。

fanout_limit:設(shè)置一個(gè)信號(hào)的最大驅(qū)動(dòng)負(fù)載數(shù)量,如果超出了該限制,就會(huì)復(fù)制一個(gè)相同的邏輯來(lái)驅(qū)動(dòng)超出的負(fù)載。這里只是一個(gè)總體設(shè)置,在RTL設(shè)計(jì)中還可以使用RTL屬性進(jìn)行更具體的設(shè)置,具體在第24篇介紹。

directive:設(shè)置Vivado綜合運(yùn)行時(shí)擦愛(ài)去的優(yōu)化方式,具體包括

Default,默認(rèn)設(shè)置。

RuntimeOptimized,執(zhí)行最短時(shí)間的優(yōu)化選項(xiàng),會(huì)忽略一些RTL優(yōu)化來(lái)減少綜合運(yùn)行時(shí)間。

AreaOptimized_high/medium,執(zhí)行一些通用的面積優(yōu)化。

AlternateRoutability,使用算法提高布線能力,減少M(fèi)UXF和CARRY的使用。

AreaMapLargeShiftRegToBRAM,將大型的移位寄存器用塊RAM來(lái)實(shí)現(xiàn)。

AreaMultThresholdDSP,會(huì)更多地使用DSP塊資源。

FewerCarryChains,位寬較大的操作數(shù)使用查找表(LUT)實(shí)現(xiàn),而不用進(jìn)位鏈。

retiming:?jiǎn)⒂迷摴δ埽梢酝ㄟ^(guò)在組合門(mén)和LUT之間移動(dòng)寄存器(達(dá)到寄存器平衡狀態(tài))提高內(nèi)部時(shí)鐘時(shí)序路徑的電路性能。該功能會(huì)保留原來(lái)的功能和電路延遲,也不需要改變RTL源文件。

fsm_extraction:設(shè)置綜合如何從設(shè)計(jì)中提取和映射有限狀態(tài)機(jī),具體在第24篇介紹。

keep_equivalent_registers:阻止合并有相同輸入邏輯的寄存器。

resource_sharing:設(shè)置不同信號(hào)間共享算數(shù)操作符,選擇為auto時(shí)設(shè)計(jì)會(huì)根據(jù)設(shè)計(jì)時(shí)序判斷是否進(jìn)行資源共享。

no_lc:選中會(huì)關(guān)閉LUT組合。

no_srlextract:選中該選項(xiàng)時(shí),移位寄存器會(huì)用普通的寄存器實(shí)現(xiàn),而不用FPGA內(nèi)部專(zhuān)用的SRL資源。

max_bram:設(shè)置設(shè)計(jì)中運(yùn)行使用的最大塊RAM數(shù)量。通常當(dāng)設(shè)計(jì)中有黑盒子或第三方網(wǎng)表時(shí),使用該選項(xiàng)來(lái)節(jié)省空間。默認(rèn)值為-1,表示允許使用該FPGA中所有的塊RAM。

max_uram:設(shè)置設(shè)計(jì)中運(yùn)行使用的最大UltraRAM數(shù)量(對(duì)于UltraScale架構(gòu)FPGA而言)。-1,表示允許使用該FPGA中所有的UltraRAM。

max_dsp:設(shè)置設(shè)計(jì)中運(yùn)行使用的最大DSP塊數(shù)量。通常當(dāng)設(shè)計(jì)中有黑盒子或第三方網(wǎng)表時(shí),使用該選項(xiàng)來(lái)節(jié)省空間。默認(rèn)值為-1,表示允許使用該FPGA中所有的DSP資源。

max_bram_cascade_height:設(shè)置可以將BRAM級(jí)聯(lián)在一起的最大數(shù)量。

max_uram_cascade_height:設(shè)置可以將URAM級(jí)聯(lián)在一起的最大數(shù)量。

cascade_dsp:設(shè)置在求DSP塊輸出總數(shù)時(shí)使用多少個(gè)加法器,默認(rèn)計(jì)算時(shí)會(huì)使用塊內(nèi)部的加法器鏈。設(shè)置為tree會(huì)強(qiáng)制將該計(jì)算在fabric結(jié)構(gòu)中實(shí)現(xiàn)。

no_timing_driven:禁用默認(rèn)的時(shí)序驅(qū)動(dòng)綜合算法,這樣可以減少綜合運(yùn)行時(shí)間,但會(huì)忽略綜合中時(shí)序的影響。

sfcu:在單文件編譯單元模式下運(yùn)行綜合。

assert:將VHDL中的assert狀態(tài)納入評(píng)估。失敗或錯(cuò)誤級(jí)別會(huì)停止綜合進(jìn)程并產(chǎn)生一個(gè)錯(cuò)誤信息;警報(bào)級(jí)別會(huì)產(chǎn)生一個(gè)警告信息。

tcl.pre/tcl.post:選擇tcl文件,在綜合前和綜合后會(huì)自動(dòng)運(yùn)行其中的命令。這兩個(gè)文件應(yīng)該放在相應(yīng)的運(yùn)行目錄下,如project/project.runs/run_name。

創(chuàng)建綜合策略

除了Vivado提供的配置好的綜合策略外,還可以自行配置。在Settings中根據(jù)需要修改了設(shè)置選項(xiàng)后,點(diǎn)擊右側(cè)的Save strategy as按鈕(如下圖紅框),會(huì)彈出窗口,填寫(xiě)策略名稱(chēng)和相關(guān)描述,即可保存為用戶自定義的綜合策略。綜合策略列表的User defined strategies中即會(huì)出現(xiàn)自定義的綜合策略。

在Settings->Tool Settings->Strategies中也可以設(shè)置綜合策略,點(diǎn)擊“+”即可新建策略。如果想在已有策略的基礎(chǔ)上修改,則選中一個(gè)策略,點(diǎn)擊上方的Copy Strategy按鈕,User Defined Strategies中就會(huì)出現(xiàn)備份以供修改(Vivado提供的策略是不能修改的)。點(diǎn)擊Apply應(yīng)用配置后,綜合策略列表中就會(huì)出現(xiàn)自定義的策略。

控制文件編譯順序

綜合時(shí)必須選取合適的編譯順序,比如一個(gè)文件需要用到另一個(gè)文件中的相關(guān)申明。Vivado按照RTL文件的層次化結(jié)構(gòu)編譯文件,相關(guān)順序顯示在Sources窗口的Compile Order子窗口中(在底部選擇切換)。

Vivado可以自動(dòng)識(shí)別和設(shè)置最佳的頂層模塊,同時(shí)自動(dòng)管理編譯順序。頂層模塊文件和該層次結(jié)構(gòu)下所有的文件,都會(huì)以正確的順序用于綜合和仿真。Sources窗口的右鍵菜單->Hierarchy Update命令用于設(shè)置Vivado如何處理設(shè)計(jì)中文件的改動(dòng)。

Automatic Update and Compile Order設(shè)定當(dāng)源文件發(fā)生改動(dòng)時(shí),工具自動(dòng)管理編譯順序,Compile Order窗口中將顯示編譯順序,Hierarchy窗口中顯示文件是否在層次結(jié)構(gòu)中使用以及所處的位置。

Automatic Update, Manual Compile Order設(shè)定Vivado可以自動(dòng)決定最佳頂層模塊,但是允許人工設(shè)定編譯順序。在Compile Order窗口中拖動(dòng)文件所處位置即可完成修改。

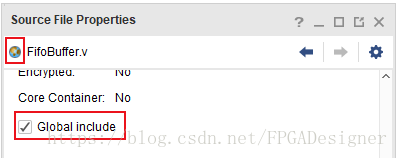

Vivado支持將Verilog(.v)或Verilog Header(.vh)文件作為全局`include文件。Vivado會(huì)在其它源文件前優(yōu)先處理此類(lèi)文件。選中需要添加的文件,右鍵->Set Global Include即可,或者在屬性窗口中選中相應(yīng)復(fù)選框。

編輯:hfy

-

vhdl

+關(guān)注

關(guān)注

30文章

819瀏覽量

129642 -

RTL

+關(guān)注

關(guān)注

1文章

388瀏覽量

60779 -

Vivado

+關(guān)注

關(guān)注

19文章

833瀏覽量

68365

發(fā)布評(píng)論請(qǐng)先 登錄

適用于Versal的AMD Vivado 加快FPGA開(kāi)發(fā)完成Versal自適應(yīng)SoC設(shè)計(jì)

電機(jī)大范圍調(diào)速的綜合電壓調(diào)制策略

軟件定義汽車(chē)(SDV)開(kāi)發(fā)有哪些挑戰(zhàn)?SDV開(kāi)發(fā)策略分享:福特汽車(chē)采用Jama Connect提升開(kāi)發(fā)效率與質(zhì)量

軟件定義汽車(chē)(SDV)開(kāi)發(fā)有哪些挑戰(zhàn)?SDV開(kāi)發(fā)策略分享:福特汽車(chē)采用Jama Connect提升開(kāi)發(fā)效率與質(zhì)量

Triton編譯器如何提升編程效率

Triton編譯器與其他編譯器的比較

Triton編譯器功能介紹 Triton編譯器使用教程

每次Vivado編譯的結(jié)果都一樣嗎

Vivado使用小技巧

淺談Vivado編譯時(shí)間

Vivado 2024.1版本的新特性(2)

Vivado開(kāi)發(fā)技巧:綜合策略與合適的編譯順序

Vivado開(kāi)發(fā)技巧:綜合策略與合適的編譯順序

評(píng)論