設計、編譯、交付,輕松搞定。更快更高效。

Vivado 設計套件提供經過優化的設計流程,讓傳統 FPGA 開發人員能夠加快完成 Versal 自適應 SoC 設計。

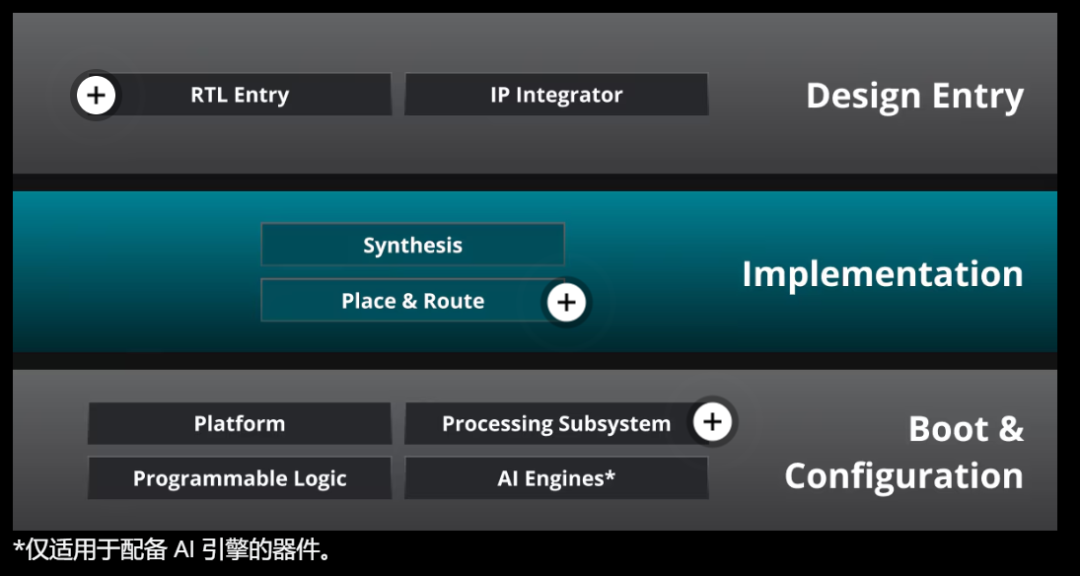

面向硬件開發人員的精簡設計流程

- 頂層 RTL 流程 -

通過使用頂層 RTL,用戶能夠像配置片上網絡和收發器一樣配置關鍵的硬核 IP,從而獲得類似于傳統 FPGA 設計的體驗。

- 快速編譯 -

全新“高級流程”實現算法融合了分層設計優化和并行執行機制,可有效解決擁塞、可布線性和運行時等問題。

- 優先啟動處理子系統 -

優先啟動處理子系統以加快操作系統初始化,同時支持多種啟動順序,并且可選擇關閉可編程邏輯并在需要時重新開啟。

滿足 FMAX 目標

Versal 自適應 SoC 雖然采用經過實踐檢驗的 FPGA 方法,但開創了一種全新的系統設計范式。Versal 架構和 Vivado 設計套件中的以下功能有助于實現時序收斂:

?

優化的編譯流程,旨在減少布線擁塞

?

時鐘區域自動校準功能,旨在充分消減時鐘偏移

?

全新時鐘緩沖器技術,旨在實現時鐘偏移消減目標

?

經過增強的裸片間連接能力,適用于基于 SSIT 的器件

借助 Vivado 工具中的全新增強功能以及內置芯片功能,實現自動化和用戶控制,從而加快完成時序收斂。

快速編譯和靈活啟動

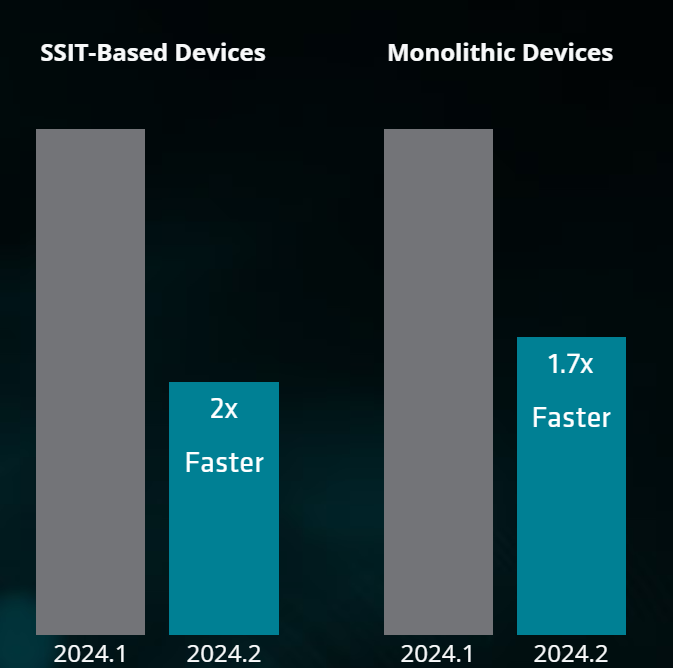

編譯速度

提升

編譯速度提升最高可達 2 倍1,2

Versal 自適應 SoC 提供更多邏輯資源和硬核 IP,可勝任更為復雜的設計。然而,更為復雜的設計可能需要更長的編譯時間。Vivado 設計套件現推出“高級流程”,在每個實現階段都進行了優化改進,與先前版本相比,編譯速度提升最高可達 2 倍:

自動分區以實現并行布局布線

布局更智能以充分減少擁塞

高級布線算法加快時序收斂

靈活的處理器啟動方式

對于需要快速啟動操作系統、嚴格控制電源排序、動態重配置 PL 而不中斷軟件運行時的應用,Vivado Design Suite 提供了多個選項,支持將處理系統配置為優先啟動。全新的分段配置流程:

?

優先啟動處理器、存儲器和操作系統

?

將 PL 配置推遲到后續階段

?

在運行時通過 Linux 或 U-Boot 交付 PL PDI(配置文件)

分段配置在 2024.2 版中作為搶先體驗( EA )功能推出。更多詳情,可參閱 GitHub 教程。

頂層 RTL 流程

對于 Versal 自適應 SoC,硬件開發人員可以使用 IP Integrator 通過基于模塊的系統方法來映射設計,或者繼續使用頂層 RTL 以便通過以下兩項新功能輕松遷移上一代 FPGA 設計:

?

模塊化 NoC 流程采用系統級方法,支持通過 RTL 和 IP integrator 環境進行例化處理,從而簡化設計輸入。

?

新增的 Versal 收發器向導提供基于 GT 原語創建的 RTL 封裝,支持進行基本的自定義設置。

在 Versal 自適應 SoC 設計流程中,IP integrator 仍可用于構建各種 IP 塊,而通過頂層 RTL 流程可靈活導入具有復雜拓撲的設計。

1.基于 AMD 于 2024 年 12 月進行的一項測試,該測試分別使用 Vivado Design Suite 2024.2 和 Vivado Design Suite 2024.1 處理 124 個 Versal 堆疊芯片互聯 (SSI) 技術器件的設計工作,以衡量平均編譯時間(小時/分鐘)。測出的編譯時間因器件、設計、配置和其他因素而異。(VIV-011)

2.基于 AMD 于 2024 年 12 月進行的一項測試,該測試分別使用 Vivado Design Suite 2024.2 和 Vivado Design Suite 2024.1 處理 151 個 Versal 單片器件的設計工作,以衡量平均編譯時間(小時/分鐘)。測出的編譯時間因器件、設計、配置和其他因素而異。(VIV-010)

-

FPGA

+關注

關注

1645文章

22049瀏覽量

618338 -

amd

+關注

關注

25文章

5587瀏覽量

136350 -

soc

+關注

關注

38文章

4387瀏覽量

222732 -

Vivado

+關注

關注

19文章

835瀏覽量

68749 -

Versal

+關注

關注

1文章

169瀏覽量

8101

原文標題:適用于 Versal 的 AMD Vivado

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

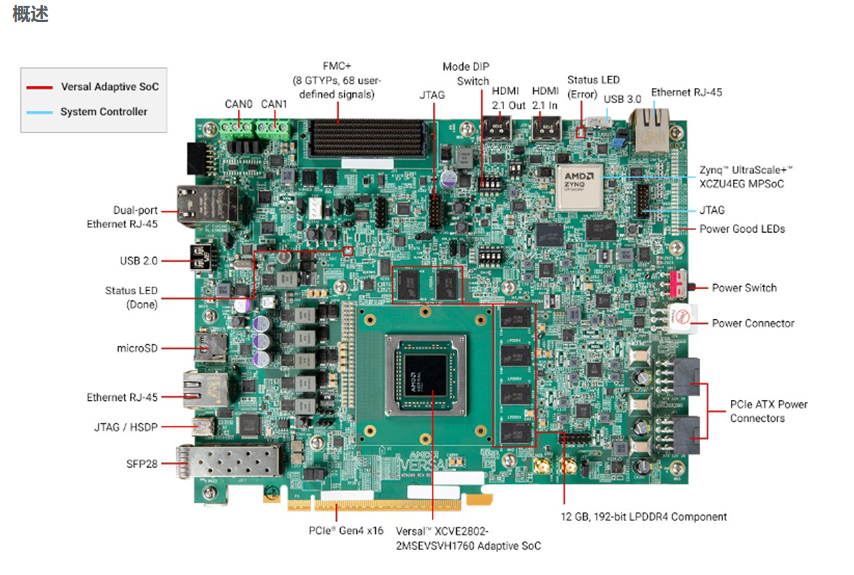

利用AMD VERSAL自適應SoC的設計基線策略

Versal 600G DCMAC Subsystem LogiCORE IP產品指南

第二代AMD Versal Premium系列SoC滿足各種CXL應用需求

面向AI與機器學習應用的開發平臺 AMD/Xilinx Versal? AI Edge VEK280

AMD Versal自適應SoC器件Advanced Flow概覽(下)

AMD Versal自適應SoC器件Advanced Flow概覽(上)

AMD Versal自適應SoC DDRMC如何使用Micron仿真模型進行仿真

AMD Vivado Design Suite 2024.2全新推出

AMD Versal自適應SoC GTM如何用XSIM仿真和觀察PAM4信號

貿澤開售適用于AI和機器學習應用的 AMD Versal AI Edge VEK280評估套件

拓展AI數據中心內存,第二代AMD Versal Premium系列自適應SoC,首發支持CXL 3.1、 PCIe Gen6

AMD推出第二代Versal Premium系列

AMD第二代Versal自適應SoC的主要特色

AMD Versal自適應SoC CPM5 QDMA的Tandem PCIe啟動流程介紹

第二代AMD Versal Prime系列自適應SoC的亮點

適用于Versal的AMD Vivado 加快FPGA開發完成Versal自適應SoC設計

適用于Versal的AMD Vivado 加快FPGA開發完成Versal自適應SoC設計

評論