一 前言

對于系統設計人員來說,模數混合電路中最困難的地方在于模擬部分的設計,其中最具代表性的就是我們經常要面對的物理層收發器(PHY)及其收發回路和匹配網絡的設計。即使對于應用比較成熟的以太網物理層設計而言,DAC驅動電流的基準偏置,差分信號線對的走線,乃至于匹配電阻的位置,都有可能影響到其物理層的信號質量并通過接口技術指標測試暴露出來。

二 以太網口信號質量測試分析

1 100Base-TX接口測試環境及其設置

100Base-TX接口測試原理

100Base-TX接口的測試采用業內比較通用的誘導發包的方法來引導DUT發出擾碼后的IDLE進行測試,更多細節請參考美國力科公司《Ethernet solution-QualiPHY》專項技術文檔,

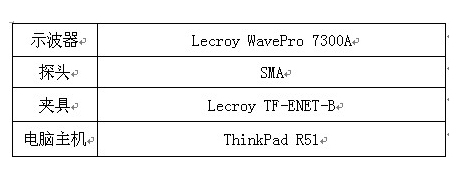

測試設備:

測試拓撲如圖1:

圖1 Ethernet接口指標測試連接框圖

2 測試中出現的問題

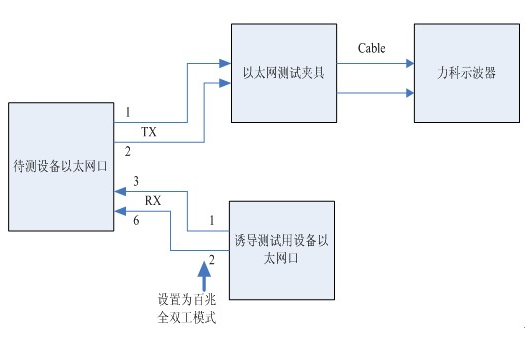

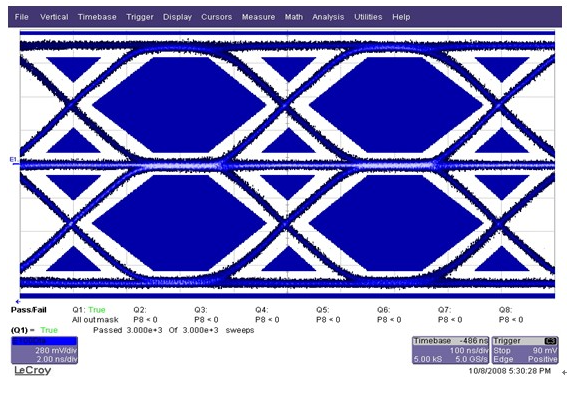

本次測試將主要驗證產品上4個以太網100Base-TX接口的技術指標。對于其中比較直觀的100Base-TX物理層的眼圖模板,《ANSI+X3_263-1995》標準中有著明確的眼圖模板定義見圖2。

圖2 100Base-TX 眼圖模板

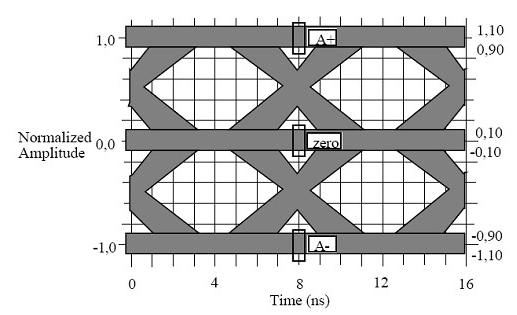

關于100Base-TX接口技術指標的測試方法,《IEEE Std 802.3-2000》標準中也有詳細的說明, 工程師按照誘導發包的測試方法進行了網口眼圖的測試,測試過程中發現測試網口出現了信號波形碰觸模板的問題,波形見圖3:

圖3 以太網口測試眼圖_FAIL

3 問題分析解決

從眼圖初步分析來看,發送信號的幅度應該是滿足要求的。但是可以明顯的發現信號邊沿還是比較緩,而且從單個波形來看邊沿有不單調的問題。方案的原廠是一家通訊業內專注于IP寬帶解決方案的國際型大公司,其以太網模塊部分應該經過詳細驗證過。最大的可能是二次開發過程中板級系統設計時的一些關鍵技術參數的配合問題。工程師在進行了信號幅度以及上升下降時間等細節指標的測試之后證明了之前的判斷,信號的幅度是滿足要求的,但信號的上升下降時間與其他的方案相比確實大了(此方案的信號上升下降時間在4.3nS~4.6nS區間,雖然滿足標準中要求的3~5nS。但根據系統容差設計原則,芯片設計人員通常會將Slew Rate調整在4nS左右,確保上下區間調整地最大容限。)。如何改進需要信號的發送接收回路進行一個系統的分析了。通過對網口技術指標的量測分析,目前最主要的問題在于信號的邊沿比較緩,并且存在不單調的問題,最可能的原因是傳輸回路容性負載過大以及驅動不足。可以從這兩個方面入手解決。

1)信號差分線對及阻抗匹配,網口的差分走線的阻抗控制和耦合處理我司在Layout這一塊的應該已經很成熟了,而且此款方案采用芯片內部匹配網絡,沒有外部匹配元件。所以暫不進行這一塊的分析。

2)傳輸變壓器,工程師將一款測試通過的產品的Transformer與當前單板的Transformer進行互換后測試結果一致,眼圖測試依然不通過。(請注意這里并沒有對變壓器進行變比以及差損,回損等技術指標的測試)

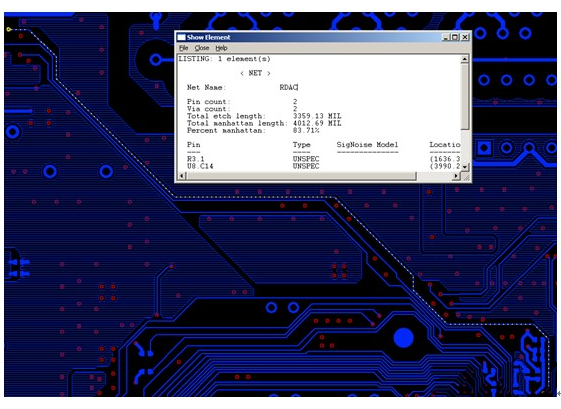

3)收發器驅動偏置電阻,也就是我們經常會看到的RDAC,也有叫RSET或其他的。這是原廠為開發人員提供的設定收發器驅動電流大小的硬配置節點,可以根據實際的單板設計和元件參數進行調整以實現對于標準的擬合。這是對信號波形影響最大的部分,在不對設計進行大的變動的情況下,通過調整驅動電流的大小可以用最小的變動來實現我們對于信號波形的調整。在查看產品PCB的同時我們還發現了另一個問題,RDAC電阻并沒有放置在輸入PIN附近,而是放到了遠端的USB部分,之間的走線長達4000MIL。從事過PHY設計的工程師都知道,對于驅動偏置電阻的處理,應該最大限度的接近輸入PIN,并保證地的干凈,原廠的Layout Guide 也會進行重點說明。這也許不是造成輸出信號邊沿過緩的直接原因,但肯定會影響到信號波形的穩定性和單調性。是需要慎重處理的。

圖4 RDAC走線連接圖

收發器驅動偏置機理分析:

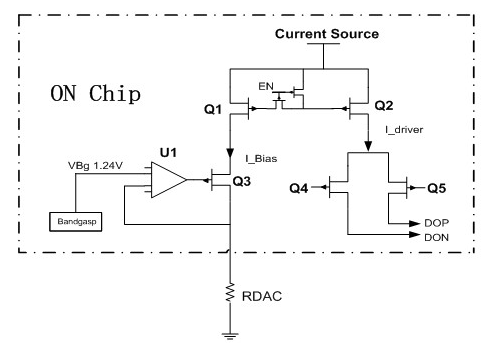

系統設計人員都知道,以太網收發器的輸出采用的是差分電流驅動,從收發器驅動偏置原理框圖,見圖5,可以進一步展開分析,收發器驅動電流可以通過帶隙電壓源與外部設定基準的比較來設定。收發器驅動電流(I_driver) 是從內部帶隙和外部基準鏡像過來。U1/Q3/RDAC/Bandgap組成了一個簡單的比較控制環路實現基準單位電流的設定,例如帶隙基準電壓設定為Vbg=1.24V,RDAC取值為1.24K。這時通過比較器U1以及MOS管Q3反饋環路是確保穩定1mA(I_bias)的基準電流。而Q1/Q2/Current _Source組成了比例鏡像電流源。可以通過設計保證I_driver=N*I_bias,N是設定的比例鏡像因子。我們假定為20,通過公式可以計算I_driver=20*I_bias=20mA,這就是我們差分驅動的輸出電流了。介紹到這里,大家都應該清楚了,我們可以通過調整RDAC的電阻大小實現基準單位電流的設定,進而達到調整差分驅動電流的目的。例如我們將RDAC調整為1K,則基準單位電流則變為I_Bias=1.24mA,同步的I_driver變為20*1.24mA=24.8mA,輸出信號電平的幅度也會增大。實際的調測結果也是這樣,可以解決信號邊沿碰觸模板的問題。

圖5 收發器驅動偏置原理框圖

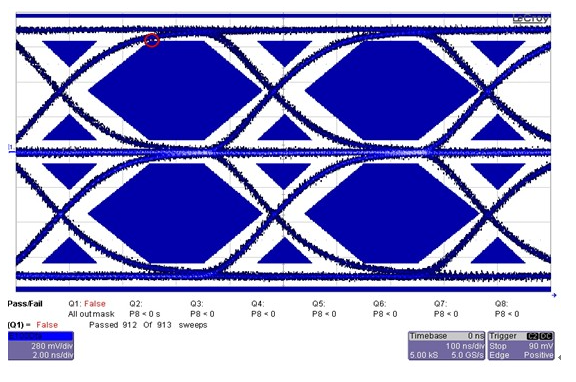

經過研發與測試工程師的討論,在目前不改動系統設計的前提下,采用微調RDAC電阻的方法來增大信號輸出電平幅度以解決信號眼圖的問題。經過調整后,眼圖測試通過,波形見圖6。

圖6 以太網口測試眼圖_PASS

三 測試總結

(1) 作為系統設計人員,對子系統功能的了解以及信號回路模型的理解是我們進行系統定性分析的根本,而對于內部電路的深入研究是我們進行系統指標設計量化的基礎。這對于我們的工程師提出了更高更深入的要求。

(2) 對于PHY收發器的設計,其驅動偏置電阻應盡量靠近設定管腳擺放,避免出現基準不穩定和誤差的出現

以太網電路設計對于我們來說是比較常規和熟悉的設計,但我們真的理解和掌握了其內部原理以及架構嗎。想要更深入,將會遇到更多的挑戰,希望本文可以給到我們的系統設計人員一些啟發。

[參考文獻]

1:以太網收發器工作原理及其信號質量測試,ShenZhen GongJin Electronic Co.

2:Ethernet solution-QualiPHY ,LeCroy Corporation

編輯:hfy

-

變壓器

+關注

關注

162文章

7787瀏覽量

139429 -

收發器

+關注

關注

10文章

3672瀏覽量

107950 -

以太網

+關注

關注

41文章

5635瀏覽量

175940 -

差分信號

+關注

關注

4文章

394瀏覽量

28323

發布評論請先 登錄

WiFi和以太網哪個更快

是德科技與KD合作推進車載以太網測試

交換機與以太網怎么連接

TOSUN 車載以太網仿真測試解決方案

以太網協議的種類和特點

工業以太網的應用場景分析

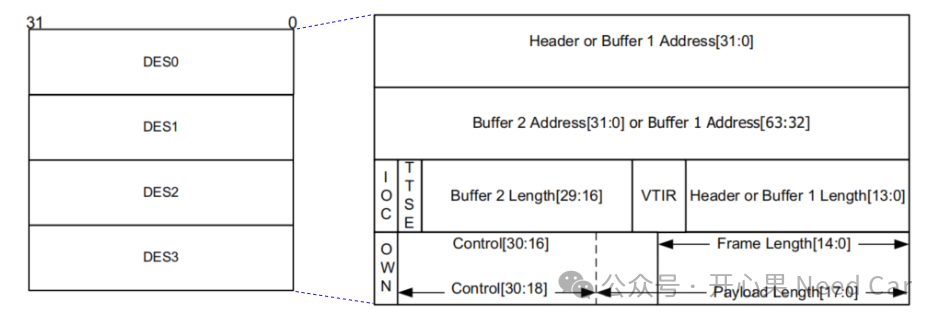

聊一聊以太網發送描述符

以太網幀格式和功能詳解

以太網幀結構是怎樣的

以太網口信號質量測試分析 DAC驅動偏置機理的探討

以太網口信號質量測試分析 DAC驅動偏置機理的探討

評論