VARON是一款針對Soc開發(fā)的硬件仿真進(jìn)行優(yōu)化的軟件,運行于Cent OS Linux系統(tǒng),需要有一定的VCS使用基礎(chǔ),適用于集成度偏高的Soc開發(fā)。VARON通過自主研發(fā)的IP連接到開發(fā)系統(tǒng),并監(jiān)視AXI總線上的多種屬性和性能,從而使開發(fā)者能夠更直觀的觀測系統(tǒng)的運行情況,從而有針對性的進(jìn)行優(yōu)化調(diào)整。

背景

1.芯片現(xiàn)狀:

1)許多IP嵌入

2)更復(fù)雜的交互

3)準(zhǔn)確的性能分析至關(guān)重要

2.開發(fā)會遇到的問題

1)需要驗證IP用于模擬和仿真,以及豐富的調(diào)試工具 2)學(xué)習(xí)如何使用驗證IP和調(diào)試工具是一個很大的挑戰(zhàn) 3)沒有性能分析方面的專業(yè)知識,也不知道從哪里開始 4)想用運行軟件調(diào)試FPGA或ASIC芯片的性能,但主要廠商不提供 5)處理大量信號級數(shù)據(jù)的速度慢 6)用于性能分析工具和工作的總成本很高

3.市面上大多數(shù)分析儀

1)性能低下: ①需要驗證IP用于模擬和仿真,以及豐富的調(diào)試工具 ②不支持FPGA和ASIC ③處理大量信號級數(shù)據(jù)的耗時 ④勞動力成本高 2)難以使用: ①手動實施驗證IP ②需要性能分析方面的專業(yè)知識,使用有限類型的圖表和使用工具的訣竅

VARON分析儀

1.高性能:

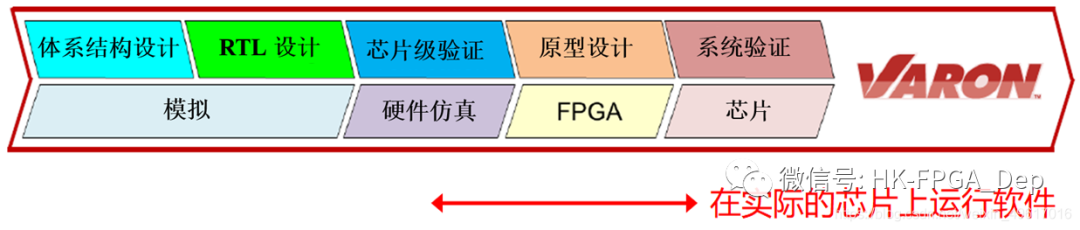

1)一個完整的產(chǎn)品,帶有可配置的片上驗證IP和專有圖形用戶界面 2)支持模擬仿真、FPGA和ASIC

3)專用于事務(wù)級數(shù)據(jù)的性能分析非常快速

4)勞動成本低,實現(xiàn)時間短

2.易于使用:

1)自動引導(dǎo)驗證IP的配置

2)通過豐富的圖表和工具提示引導(dǎo)分析

VARON的優(yōu)勢

1.涵蓋LSI設(shè)計驗證的整個過程

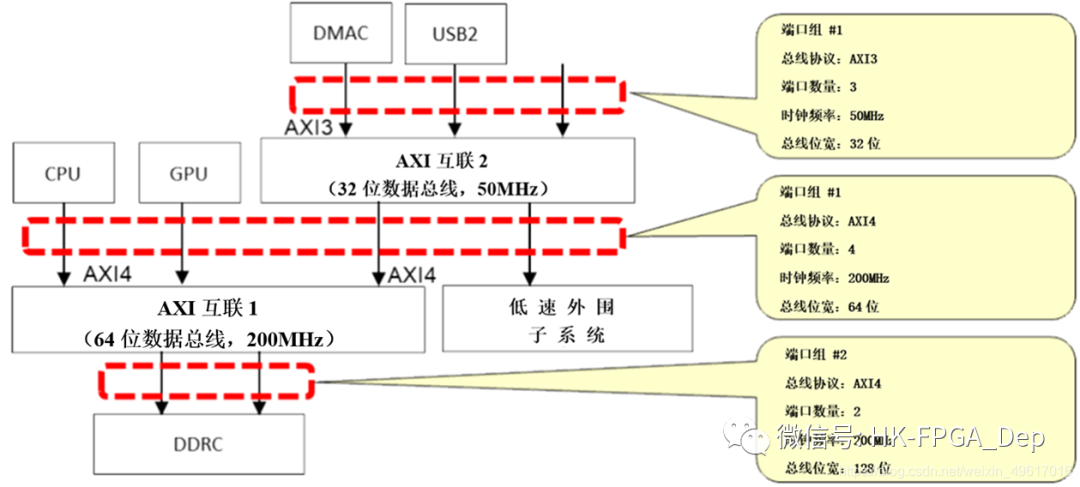

2.完全可配置的驗證IP滿足用戶需求

1)按端口組進(jìn)行獨立配置 2)易于分析系統(tǒng)中跨總線級聯(lián)的事務(wù)

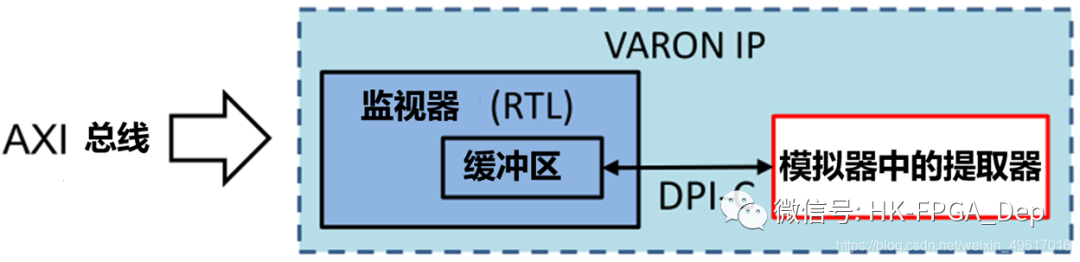

3.針對硬件仿真器進(jìn)行了優(yōu)化,以最大限度地提高速度

1)硬件IP將AXI數(shù)據(jù)緩沖到模擬器 2)監(jiān)視器和緩沖區(qū)都是可綜合的

4.分析時間短,數(shù)據(jù)處理速度快

1)在事務(wù)級別監(jiān)視AXI 2)快速顯示所有性能圖表,不依賴于設(shè)計尺寸

| AXI周期 | 1,000,000 | 10,000,000 | |

| 分析時間(秒) | 8 | 95 | |

| 文件大小(字節(jié)) | 47,955,968 | 480,460,800 | |

| 處理數(shù)量 | 讀 | 377,007 | 3,776,145 |

| 寫 | 381,075 | 3,820,338 | |

| 數(shù)據(jù)傳輸總量(字節(jié)) | 讀 | 9,186,842 | 92,111,540 |

| 寫 | 9,291,924 | 93,326,480 |

5.通過豐富的性能圖表組合進(jìn)行非常簡單的分析

1)每個端口組20個圖表 2)通過6種圖表類型了解2個分析目標(biāo)的5個關(guān)鍵設(shè)計標(biāo)準(zhǔn)

| 目標(biāo) | 設(shè)計準(zhǔn)則 | 圖表類型 | 備注 |

| 響應(yīng)時間 | 按端口或ID列出的延遲 | 直方圖 | 延遲分布 |

| 最大值/最小值/均值 | |||

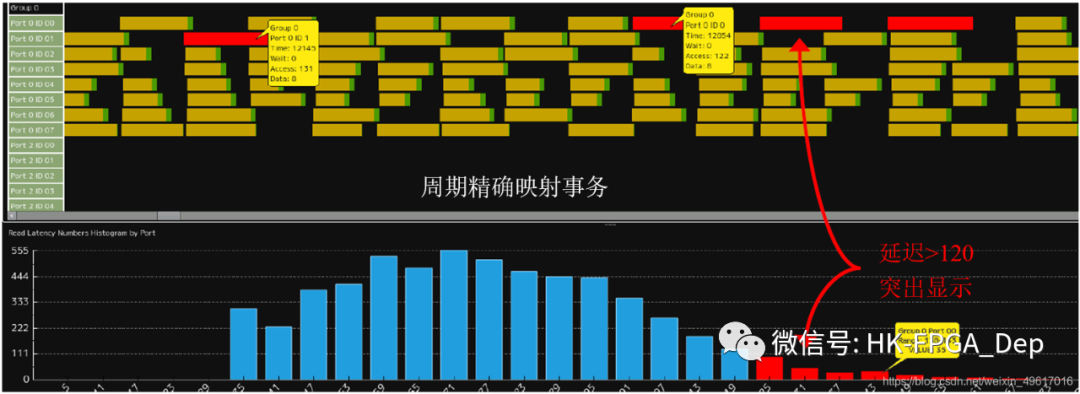

| 按端口或ID列出的事務(wù) | 時間圖 | 隨著時間的推移,循環(huán)準(zhǔn)確地映射事務(wù) | |

| 總線使用效率 | 按端口或ID列出的數(shù)據(jù)傳輸總量 | 圓形分格統(tǒng)計圖表 | 空閑周期—>總線利用率 |

| 條形圖 | 端口或ID之間的比較 | ||

| 按端口或ID的突發(fā)長度 | 直方圖 | 突發(fā)長度分布 | |

| 按端口或ID列出的單位時間的數(shù)據(jù)傳輸量 | 堆疊時序圖 | 一段時間內(nèi)所有端口或所有ID的總數(shù)據(jù)傳輸量 | |

| 條形時序圖 | 每個端口或ID隨時間的數(shù)據(jù)傳輸量 | ||

| 最大值/最小值/均值 | |||

| 直方圖 | 數(shù)據(jù)傳輸量分布 |

6.工具幫助用戶進(jìn)行詳細(xì)的調(diào)試

1)放大/縮小以驗證整體趨勢 2)放大/正常大小,跳轉(zhuǎn)到時間和工具提示來檢查本地數(shù)據(jù)

單位時間的數(shù)據(jù)傳輸量:正常大小(左)、放大(右)

3)水平能夠同步顯示3個時序圖,以在一個時間窗口內(nèi)驗證相關(guān)數(shù)據(jù)

按條形圖顯示單位時間的數(shù)據(jù)傳輸量(上)

堆疊視圖顯示單位時間的數(shù)據(jù)傳輸量(中)

事務(wù)時間表(下)

4)找出超出范圍來突出顯示5個圖表中超出預(yù)期的數(shù)據(jù)

延遲直方圖、事務(wù)時序圖、堆疊/條形圖時序圖和單位時間數(shù)據(jù)傳輸周期直方圖

事務(wù)時間表(上)

延遲直方圖(下)

5)由圖表設(shè)計的工具提示,用于感興趣的詳細(xì)數(shù)據(jù) ①左鍵單擊出現(xiàn),右鍵單擊鎖定/移動/刪除 ②上圖例子:

延遲直方圖:在端口0有35個事務(wù),延遲為138–143

事務(wù)時序圖:端口0: ID 01事務(wù)開始于時間12和145,具有0等待、131訪問(延遲)和8字傳輸

介紹完功能后,下篇文章我們根據(jù)實際案例來具體分析。

責(zé)任編輯:xj

原文標(biāo)題:AXI總線高性能分析儀——VARON(一)

文章出處:【微信公眾號:FPGA技術(shù)支持】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

分析儀

+關(guān)注

關(guān)注

0文章

1544瀏覽量

52266 -

soc

+關(guān)注

關(guān)注

38文章

4208瀏覽量

219133 -

Linux

+關(guān)注

關(guān)注

87文章

11350瀏覽量

210446 -

仿真

+關(guān)注

關(guān)注

50文章

4125瀏覽量

134020 -

AXI

+關(guān)注

關(guān)注

1文章

128瀏覽量

16719

原文標(biāo)題:AXI總線高性能分析儀——VARON(一)

文章出處:【微信號:HK-FPGA_Dep,微信公眾號:FPGA技術(shù)支持】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Simcenter FLOEFD 熱仿真分析軟件

【產(chǎn)品介紹】Simcenter Amesim系統(tǒng)仿真軟件

Simcenter HEEDS設(shè)計空間探索和優(yōu)化軟件

這些電源常用仿真軟件,你都知道嗎?

這些電源常用仿真軟件,你都知道嗎?

一款針對Soc開發(fā)的硬件仿真進(jìn)行優(yōu)化的軟件VARON

一款針對Soc開發(fā)的硬件仿真進(jìn)行優(yōu)化的軟件VARON

評論