以下文章來源于學(xué)習(xí)那些事,作者小陳婆婆

2.5D封裝

關(guān)于2.5D封裝的關(guān)鍵工藝,特別是凸塊制作技術(shù),我們可以進(jìn)一步詳細(xì)闡述如下:

封裝關(guān)鍵工藝概述

銅柱凸塊簡介及關(guān)鍵工藝分析

金凸塊(Au-Bump)工藝

1封裝關(guān)鍵工藝概述

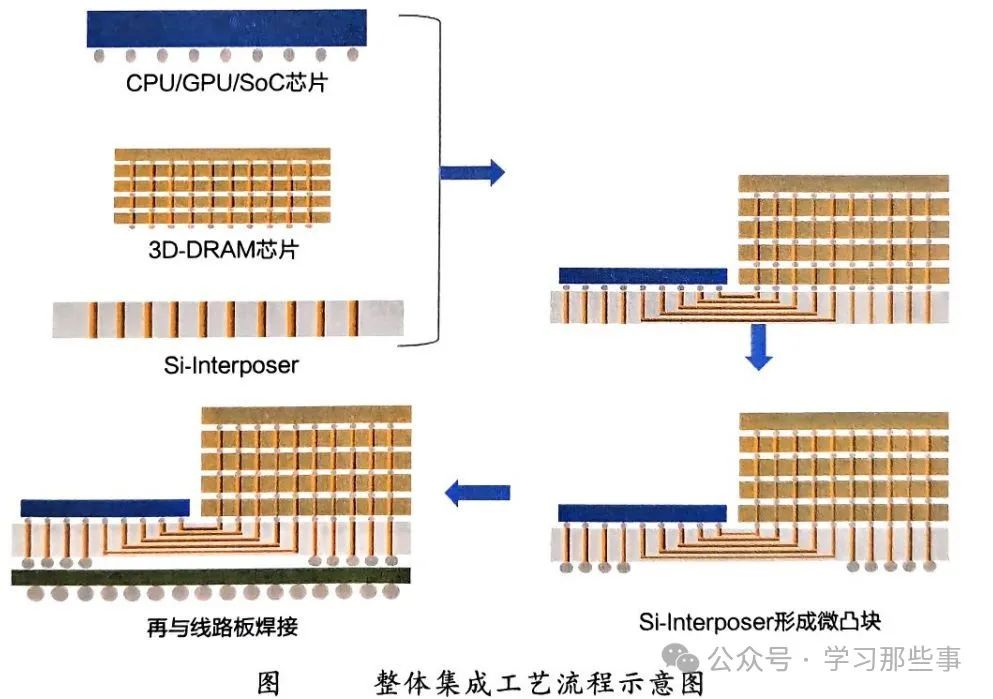

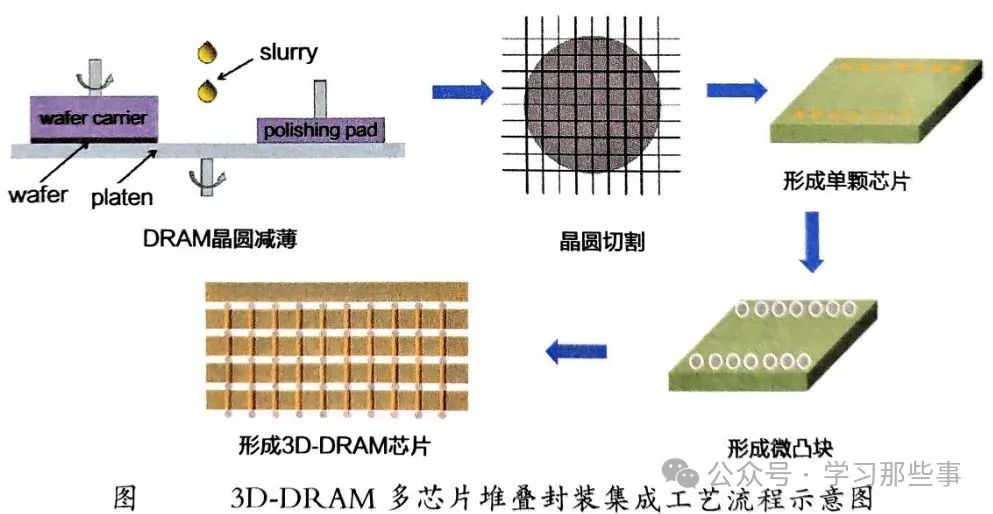

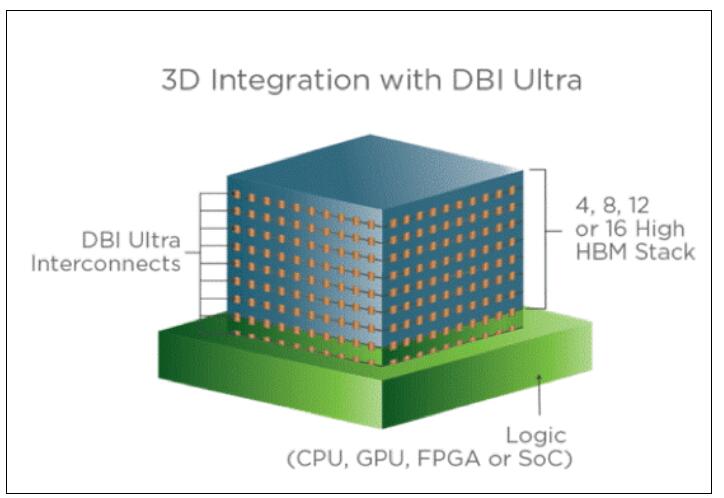

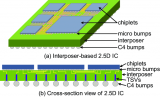

2.5D封裝工藝是一種先進(jìn)的半導(dǎo)體封裝技術(shù),它通過中介層(Interposer)將多個功能芯片在垂直方向上連接起來,從而減小封裝尺寸面積,減少芯片縱向間互連的距離,并提高芯片的電氣性能指標(biāo)。這種工藝的關(guān)鍵步驟包括形成3D-DRAM芯片集成、形成Si-Interposer,以及將芯片與Si-Interposer集成。

凸塊是在倒裝芯片或帶TSV(硅通孔)的多個部件之間疊加焊接所需的焊盤上添加的凸點。它在2.5D和3D封裝工藝中扮演著至關(guān)重要的角色,因為它提供了芯片與中介層或線路板之間的電氣連接。

凸塊制作的主要方法

電鍍法:電鍍法是目前應(yīng)用最廣泛的凸塊制作方法。它通過在鍍液中施加電流,使金屬離子在鍍件表面還原沉積形成金屬鍍層。電鍍法可以制作尺寸小、生產(chǎn)效率高、可靠性好的凸塊。

化學(xué)鍍法:化學(xué)鍍法是一種無電解的鍍金屬過程,它利用還原劑將溶液中的金屬離子還原成金屬原子并沉積在鍍件表面。這種方法適用于復(fù)雜形狀和難以電鍍的部件。

蒸發(fā)法:蒸發(fā)法是通過加熱金屬使其蒸發(fā),然后在鍍件表面冷凝形成金屬鍍層。這種方法適用于制作高純度和高附著力的凸塊。

錫膏印刷法:錫膏印刷法是將含有金屬顆粒的錫膏通過印刷方式涂覆在焊盤上。這種方法適用于大規(guī)模生產(chǎn)和自動化生產(chǎn)。

凸塊制作技術(shù)的優(yōu)點與挑戰(zhàn)

優(yōu)點:凸塊制作技術(shù)提供了芯片與中介層或線路板之間的高可靠性電氣連接;有助于減小封裝尺寸和提高封裝密度;凸塊制作技術(shù)還可以提高芯片的散熱性能。

挑戰(zhàn):凸塊制作過程中需要精確控制凸塊的高度、形狀和位置;對于高密度封裝,凸塊之間的間距越來越小,這對制作精度提出了更高的要求;凸塊制作過程中還需要考慮金屬材料的選擇、鍍液的穩(wěn)定性和環(huán)保性等問題。

2銅柱凸塊簡介及關(guān)鍵工藝分析

凸塊制作技術(shù)是2.5D封裝工藝中的關(guān)鍵步驟之一。通過選擇合適的凸塊制作方法和優(yōu)化制作工藝參數(shù),可以制作出高質(zhì)量、高可靠性的凸塊,從而滿足2.5D封裝對電氣連接、封裝密度和散熱性能等方面的要求。

銅柱凸塊的主要構(gòu)成及作用

銅柱凸塊主要由電鍍銅柱、電鍍鎳阻擋層和電鍍錫合金凸塊三部分組成。

電鍍銅柱提供良好的導(dǎo)電功能,鎳層作為阻擋層防止銅和錫的擴(kuò)散,而錫合金凸塊則通過回流焊與其他部件進(jìn)行焊接連通。

電鍍銅柱的關(guān)鍵性能要求

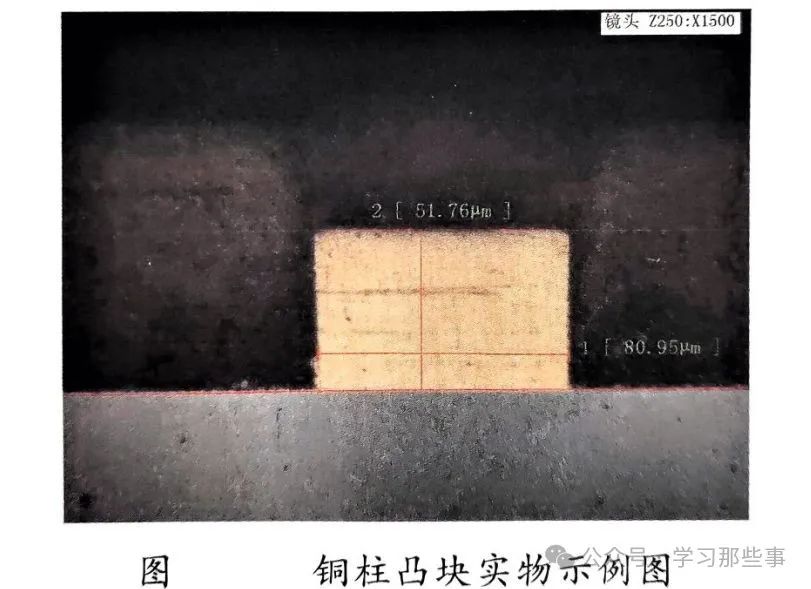

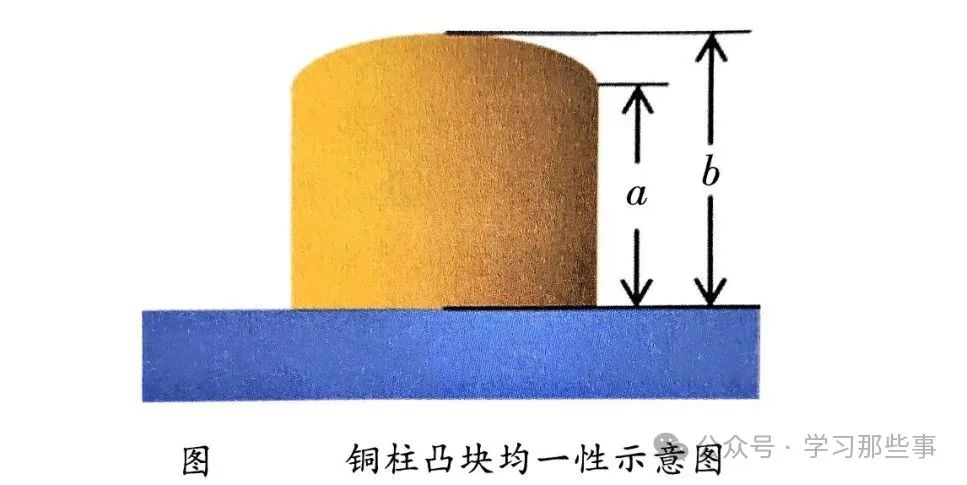

單顆銅柱的均一性:要求單顆銅柱的高度均勻性在±5%范圍內(nèi),以確保凸塊連接的穩(wěn)定性和可靠性。

高電流密度操作能力:為了提高生產(chǎn)效率,電鍍銅柱需要具備在高電流密度(如10ASD以上)下穩(wěn)定操作的能力。這要求電鍍液和設(shè)備具有較高的銅離子補(bǔ)充能力和藥水運(yùn)動能力。

是否需要電鍍鎳:根據(jù)產(chǎn)品要求決定是否需要電鍍鎳作為阻擋層。無鎳阻擋層時,需確保銅柱和錫凸塊老化后不會出現(xiàn)柯肯達(dá)爾空洞(KV)缺陷。

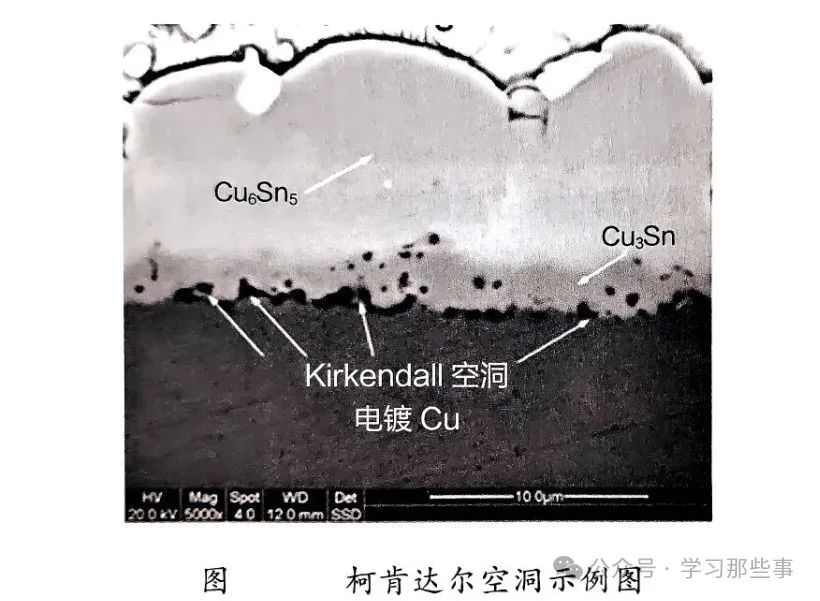

柯肯達(dá)爾空洞(KV)的影響及消除措施

柯肯達(dá)爾空洞是銅柱和錫凸塊之間界面層出現(xiàn)的一種空洞缺陷,會嚴(yán)重影響凸塊連接的電學(xué)和力學(xué)可靠性。

KV與銅鍍層結(jié)晶有很大關(guān)系,合適的電鍍?nèi)芤汉凸に噮?shù)是消除KV的關(guān)鍵。通過調(diào)整電鍍?nèi)芤褐械柠u素、硫化物濃度等參數(shù),可以優(yōu)化銅柱的晶粒大小,從而減少或消除KV。

電鍍鎳阻擋層的作用及特殊情況

電鍍鎳一般作為阻擋層使用,其厚度為2~5微米,可以大幅降低銅和錫合金凸塊之間的擴(kuò)散。然而,在特殊應(yīng)用場合,如擔(dān)心鎳層對半導(dǎo)體器件性能的影響時,會拒絕使用鎳鍍層。此時,需要采取其他措施來防止銅和錫的擴(kuò)散。

電鍍錫銀凸塊的無鉛化趨勢

電鍍錫銀凸塊是目前電鍍凸塊工藝中最主要的鍍種之一,其銀含量通常在1.8%±0.5%范圍內(nèi)。隨著環(huán)保意識的提高,無鉛化成為凸塊工藝的重要趨勢。然而,焊料合金中存在的容易發(fā)生阿爾法衰變的重金屬元素(如鉛、鉍等)會引起半導(dǎo)體器件的單粒子效應(yīng),導(dǎo)致數(shù)據(jù)丟失、功能中斷等危害。因此,在凸塊工藝中需要關(guān)注焊料合金的阿爾法射線問題,并采取相應(yīng)措施來降低其影響。

銅柱凸塊作為倒裝芯片技術(shù)中的關(guān)鍵組成部分,其性能和質(zhì)量對半導(dǎo)體器件的可靠性和性能具有重要影響。通過優(yōu)化電鍍銅柱的工藝參數(shù)和溶液配方、選擇合適的阻擋層材料、關(guān)注焊料合金的阿爾法射線問題等措施,可以進(jìn)一步提高銅柱凸塊的質(zhì)量和可靠性。隨著半導(dǎo)體技術(shù)的不斷發(fā)展,銅柱凸塊工藝將繼續(xù)向著更高密度、更高性能的方向發(fā)展。

3金凸塊(Au-Bump)工藝

金凸塊是指在芯片的焊盤上通過電鍍或其他技術(shù)形成的微小金屬凸點,這些凸點作為芯片與封裝基板之間電路導(dǎo)通的橋梁。

除了單純的金凸塊外,還有銅鎳金凸塊等衍生結(jié)構(gòu),它們以銅、鎳取代一部分的金,以提高凸塊整體硬度,降低與基板結(jié)合受力而變形的風(fēng)險,同時減少金的用量和降低成本。

性能特點

導(dǎo)電、導(dǎo)熱能力強(qiáng):金凸塊具有優(yōu)秀的導(dǎo)電和導(dǎo)熱能力,能夠確保芯片與封裝基板之間穩(wěn)定而高效的信號傳輸和熱量傳遞。

硬度高:通過添加銅、鎳等元素,金凸塊的硬度得到提升,從而增強(qiáng)了其在使用過程中的穩(wěn)定性和可靠性。

抗氧化能力強(qiáng):金具有良好的抗氧化性能,能夠保護(hù)凸塊免受氧化腐蝕的影響,延長使用壽命。

尺寸小、密度高:金凸塊的尺寸通常很小,且能夠在有限的空間內(nèi)實現(xiàn)高密度的電路連接,滿足現(xiàn)代電子產(chǎn)品對小型化和高性能的需求。

金凸塊主要應(yīng)用于以下領(lǐng)域:

顯示器驅(qū)動芯片:金凸塊是顯示驅(qū)動芯片封測核心量產(chǎn)工藝之一,其市場需求隨著手機(jī)、電腦等終端市場的快速發(fā)展而不斷增加。

射頻芯片:在射頻芯片封裝中,金凸塊能夠提供穩(wěn)定的電路連接和信號傳輸,確保射頻信號的準(zhǔn)確性和穩(wěn)定性。

攝像頭芯片:攝像頭芯片對電路連接的穩(wěn)定性和信號傳輸?shù)馁|(zhì)量要求較高,金凸塊能夠滿足這些要求,因此被廣泛應(yīng)用于攝像頭芯片的封裝中。

指紋識別系統(tǒng):指紋識別系統(tǒng)需要高精度的電路連接和信號傳輸,金凸塊以其優(yōu)異的性能成為指紋識別系統(tǒng)封裝的優(yōu)選方案。

金凸塊的電鍍工藝流程通常包括以下幾個步驟:

清洗:使用等離子體等技術(shù)清洗晶圓表面,去除有機(jī)物、氧化物等污染物,為后續(xù)的沉積過程提供一個干凈、無污染的基底。

濺射:在清洗后的焊盤上沉積一層鈦鎢(TiW)作為粘附層,再沉積一層金(Au)作為種子層,為后續(xù)的電鍍工序提供導(dǎo)電通道。

涂布光刻膠:在晶圓表面涂布一層較厚的光刻膠,其厚度設(shè)計需高于最終金凸點的高度。

光刻:通過曝光、顯影等步驟,將設(shè)計好的電路圖案轉(zhuǎn)移到光刻膠上,露出需要電鍍的部分。

電鍍:在已暴露的金屬區(qū)域進(jìn)行電鍍,沉積一層金形成微小的金屬凸點。

剝離光刻膠:去除晶圓表面的光刻膠,暴露出底層的鈦鎢/金層。

刻蝕:使用濕法刻蝕工藝去除未覆蓋電鍍層的多余鈦鎢和金層,保留已經(jīng)形成的金凸點。

退火:通過退火處理使電鍍的金凸點結(jié)構(gòu)更加堅硬,提高機(jī)械強(qiáng)度和穩(wěn)定性。

-

芯片

+關(guān)注

關(guān)注

459文章

52291瀏覽量

437597 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28694瀏覽量

234030 -

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

576瀏覽量

68481 -

2.5D封裝

+關(guān)注

關(guān)注

0文章

24瀏覽量

324

原文標(biāo)題:2.5D封裝的關(guān)鍵工藝詳述

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

新型封裝工藝介紹

IC封裝工藝測試流程的詳細(xì)資料詳解

新型2.5D和3D封裝技術(shù)的挑戰(zhàn)

研發(fā)的銅混合鍵合工藝正推動下一代2.5D和3D封裝技術(shù)

3D封裝與2.5D封裝比較

2.5D封裝應(yīng)力翹曲設(shè)計過程

2.5D和3D封裝的差異和應(yīng)用

一文理解2.5D和3D封裝技術(shù)

深入剖析2.5D封裝技術(shù)優(yōu)勢及應(yīng)用

2.5D封裝的熱力挑戰(zhàn)

技術(shù)資訊 | 2.5D 與 3D 封裝

SK海力士考慮提供2.5D后端工藝服務(wù)

2.5D封裝為何成為AI芯片的“寵兒”?

一文詳解2.5D封裝工藝

一文詳解2.5D封裝工藝

評論