代工廠、設備供應商、研發(fā)機構等都在研發(fā)一種稱之為銅混合鍵合(Hybrid bonding)工藝,這項技術正在推動下一代2.5D和3D封裝技術。

與現(xiàn)有的堆疊和鍵合方法相比,混合鍵合可以提供更高的帶寬和更低的功耗,但混合鍵合技術也更難實現(xiàn)。

異構集成是銅混合鍵合的主要優(yōu)勢

銅混合鍵合并不是新鮮事,從2016年開始,CMOS圖像傳感器開始使用晶圓間(Wafer-to-Wafer)的混合鍵合技術制造產(chǎn)品。具體而言,供應商會先生產(chǎn)一個邏輯晶圓,然后生產(chǎn)一個用于像素處理的單獨晶圓,之后使用銅互連技術將兩個晶圓結(jié)合在一起,再將各芯片切成小片,形成CMOS圖像傳感器。

混合鍵合與先進封裝的工作方式幾乎相同,但前者更復雜。供應商正在開發(fā)另一種不同的變體,稱為裸片對晶圓(Die-to-Wafer)的鍵合,可以在內(nèi)插器或者其他裸片上堆疊和鍵合裸片。KLA的行銷高級總監(jiān)Stephen Hiebert表示:“我們能觀察到裸片對晶圓的混合鍵合發(fā)展強勁,其主要優(yōu)勢在于它能夠?qū)崿F(xiàn)不同尺寸芯片的異構集成。”

這一方案將先進封裝提高到一個新的水平,在當今先進封裝案例中,供應商可以在封裝中集成多裸片的DRAM堆棧,并使用現(xiàn)有的互連方案連接裸片。通過混合鍵合,DRAM裸片可以使用銅互連的方法提供更高的帶寬,這種方法也可以用在內(nèi)存堆棧和其他高級組合的邏輯中。

Xperi的杰出工程師Guilian Gao在最近的演講中說:“它具有適用于不同應用的潛力,包括3D DRAM,異構集成和芯片分解。”

不過這是一項極具挑戰(zhàn)性的工作。裸片對晶圓的混合鍵合需要原始的芯片、先進的設備和完美的集成方案,但是如果供應商能夠滿足這些要求,那么該項技術將成為高級芯片設計的誘人選擇。

傳統(tǒng)上,為改進設計,業(yè)界開發(fā)了片上系統(tǒng)(SoC),可以縮小每個具有不同功能的節(jié)點,然后在將它們封裝到同一裸片上,但是隨著單個節(jié)點正變得越來越復雜和昂貴,更多的人轉(zhuǎn)向?qū)ふ倚碌奶娲桨浮T趥鹘y(tǒng)的先進封裝中組裝復雜的芯片可以擴展節(jié)點,使用混合鍵合的先進封裝則是另一種選擇。

GlobalFoundry、英特爾、三星、臺積電和聯(lián)電都在致力于銅混合鍵合封裝技術,Imec和Leti也是如此。此外,Xperi正在開發(fā)一種混合鍵合技術,并將該技術許可給其他公司。

已有IC封裝技術的特色

IC封裝類型眾多,細分封裝市場的互連類型,包括引線鍵合、倒裝芯片、晶圓級封裝(WLP)和直通硅通孔(TSV)。互連是將一個芯片連接到封裝中的另一個芯片,TSV的I/O數(shù)量最高,其次是WLP、倒裝芯片和引線鍵合,混合互連比TSV密度更高。

TechSearch稱 ,當今的封裝大約有75%至80%是基于引線鍵合,即使用焊線機細線將一個芯片接到另一個芯片或基板上,引線鍵合多用于商品包裝和存儲器裸片堆疊。

在倒裝芯片中,使用各種工藝步驟在芯片頂部形成大量的焊料凸塊或微小的銅凸塊,然后將器件翻轉(zhuǎn)并安裝在單獨的芯片或板上。凸塊落在銅焊盤上,形成點連接,稱之為晶圓鍵合機的系統(tǒng)鍵合裸片。

WLP是直接在晶圓上進行封裝測試,之后再切割成單顆組件。扇出晶圓級封裝(Fan-out WLP)也是晶圓級封裝中的一種。Veeco的一位科學家Cliff McCold在ECTC的演講中說,“采用WLP能夠進行較小的二維連接,從而將硅芯片重新分派到更大的面積上,為現(xiàn)代設備提供更高的I/O密度,更高的帶寬和性能。”

TSV用于高端2.5D/3D封裝。在2.5D封裝中,裸片堆疊在內(nèi)插器上,內(nèi)插器中包含TSV,中間層是連接芯片和電路板之間的橋梁,可提供更多的I/O和帶寬。

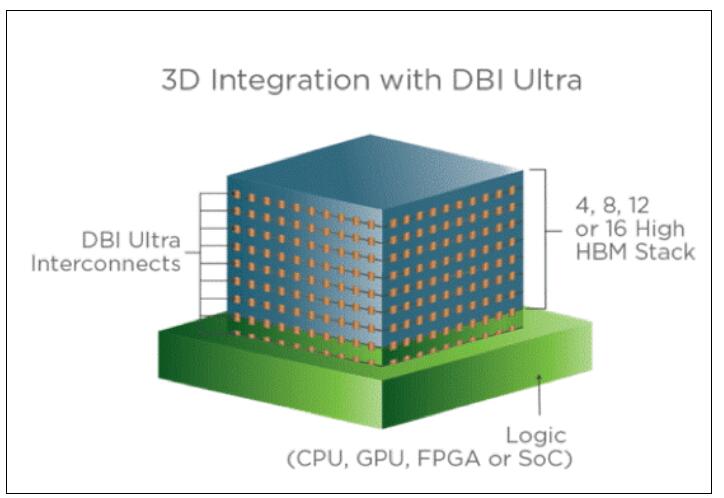

2.5D封裝和3D封裝的類型眾多,高帶寬存儲器(HBM)就是一種3D封裝類型,這一方法是將DRAM裸片堆疊在一起。將邏輯堆疊在邏輯上或?qū)⑦壿嬛糜趦?nèi)存上的方法也正在出現(xiàn)。英特爾產(chǎn)品集成總監(jiān)Ramune Nagisetty表示,邏輯堆疊在邏輯上的方法還沒有普及,邏輯堆疊在內(nèi)存上的方法目前正在興起。

在封裝中,目前備受關注的是小芯片。小芯片本身不是一種封裝類型,但芯片制造商的庫中可以擁有一個模塊化裸片或多種小芯片,客戶可以混合搭配這些芯片,并使用封裝中裸片對裸片(Die-to-Die)的互連方案進行連接。

小芯片可以存在于現(xiàn)有的封裝類型或新的體系架構中。“這是一種架構方法,” UMC(聯(lián)華電子)負責業(yè)務開發(fā)的副總裁Walter Ng說,“它正在為任務需求優(yōu)化解決方案,這些需求包括速度、熱量、功率等性能,有時還需要考慮成本因素。”

當下最先進的2.5D封裝和3D封裝是供應商所使用的現(xiàn)有互連方案和晶圓鍵合器。在這些封裝中,使用銅凸塊或銅柱堆疊和連接裸片,基于焊接材料,凸塊和支柱在不同的設備之間提供小而快速的電氣連接。

最先進的微型凸塊的間距是40μm至36μm,這里的間距包括一定的空間距離,例如40μm間距就是25μm的銅柱加上15微米的空間距離。

對于細間距的要求,業(yè)界使用熱壓縮連接(TCB)。用一個TCB鍵合器取出一塊裸片,并將其凸塊與另一塊裸片的凸塊對齊,再用壓力和熱力將凸塊鍵合起來。不過,TCB過程緩慢,且銅凸塊也正在逼近物理極限。一般而言,視極限間距為20μm,但也有一部分人在嘗試延伸凸點間距。

Imec正在開發(fā)一種使用TCB實現(xiàn)的10μm間距技術,7μm和5μm也正在研發(fā)中。“40μm凸塊間距有足夠的焊接材料來補償電流變化。當縮放到10μm或更小的間距時,情況將會發(fā)生變化,” Imec的高級科學家Jaber Derakhshandeh在最近的ECTC會議上的一篇論文中說,“在細間距的微泵中,電流量和良好的連接取決于TCB工具的精度、錯位、傾斜以及焊料的變形量。”

為了延長微型凸塊的發(fā)展壽命,Imec開發(fā)了一種金屬墊板工藝,同以前一樣,裸片上仍然有微型凸塊,不同的是,在Imec工藝中,裸片上還有假金屬微凸塊,這類凸塊類似于支撐架構的小梁。

Derakhshandeh說:“在3D裸片對晶圓的堆疊中引入了一個假金屬微凸塊,以減小TCB工具的傾斜誤差,并控制焊料變形,從而使粘合裸片不同位置的電阻和成形接頭的質(zhì)量相同。”。

混合鍵合是TCB的補充

在某些時候,微型凸塊/支柱和TCB可能會用光,這時候就需要混合鍵合,它可以用在微凸技術碰壁后或者在此前插入。

不過微型凸塊不會很快在市場上消失,微型凸塊和混合鍵合技術都將在市場上占據(jù)一席之地,這取決于具體的應用。

目前混合鍵合技術正在發(fā)展,臺積電最有發(fā)言權,其正在研究一種叫做集成芯片系統(tǒng)(SoIC)的技術。使用混合鍵合,臺積電的SoIC技術可以實現(xiàn)低于微米的鍵合間距。據(jù)悉,SoIC的緩沖墊間距是現(xiàn)有方案的0.25倍。高密度版本可以實現(xiàn)10倍以上的芯片到芯片的通信速度,高達近2000倍的帶寬密度和20倍的能源效率。

臺積電的SoIC計劃于2021年投入生產(chǎn),可以實現(xiàn)小間距HBM和SRAM存儲立方體以及類似3D的芯片架構。臺積電研究員MF Chen在最近的一篇論文中說,與當今HBM相比,“繼承了SoIC的DRAM存儲器立方體可以提供更高的存儲器密度、帶寬和功率效率。”

臺積電正在開發(fā)芯片對晶圓(Chip-to-Wafer)的混合鍵合技術。晶圓鍵合已經(jīng)在微機電系統(tǒng)(MEMS)和其他應用中使用多年,且類型眾多。“微電子和微機電系統(tǒng)的制造和封裝依賴于兩個基板或晶片的鍵合,” Brewer Science的高級研究化學家Xiao Liu說道,“在微機電系統(tǒng)的制造過程中,器件晶圓將被粘合到另一個晶圓上,以保護敏感的MEMS結(jié)構。直接鍵合技術(例如熔融鍵合和陽極鍵合)或間接鍵合技術(例如金屬共晶、熱壓鍵合和膠粘劑鍵合)都是常用的方法。使用膠粘劑作為兩個基板之間的中間層,處理會更加靈活。”

銅混合鍵合最早出現(xiàn)在2016年,當時索尼將這項技術用于CMOS圖像傳感器, 索尼從現(xiàn)在屬于Xperi的Ziptronix獲得了該技術的許可。

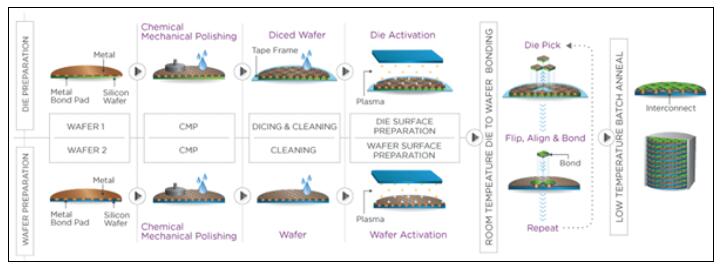

Xperi的技術稱為直接綁定互連(DBI),DBI在傳統(tǒng)的晶圓廠中進行,并應用于晶圓對晶圓的鍵合工藝,在這一過程中,先對晶圓進行處理,然后將金屬焊盤凹入表面,使表面變得平滑。

分離晶圓也經(jīng)歷類似的過程,晶片使用兩步工藝鍵合,首先是電介質(zhì)互連,然后是金屬互連。

EV Group業(yè)務發(fā)展總監(jiān)Thomas Uhrmann表示:“總體而言,晶圓對晶圓是設備制造的首選方法,在整個工藝流程中,晶圓都保留在前端晶圓廠環(huán)境中。在這種情況下,用于混合鍵合的晶圓制備在界面設計規(guī)則、清潔度、材料選擇以及激活和對準方面面臨諸多挑戰(zhàn)。氧化物表面上的任何顆粒都會產(chǎn)生比顆粒本身大100至1,000倍的空隙。”

盡管如此,該技術已被證明可用于圖像傳感器,其他設備正在研究開發(fā)中。Uhrmann說:“計劃進一步推出諸如堆疊SRAM到處理器芯片之類的器件。”

混合鍵合的3D集成,圖片源自:Xperi

銅混合鍵合推動先進封裝

對于先進芯片封裝,業(yè)界還致力于裸片對晶圓和裸片對裸片的銅混合鍵合,即將裸片堆疊在晶圓上、將裸片堆疊在中介層上或?qū)⒙闫询B在裸片上。

這比晶圓間鍵合更加困難。“對于裸片對晶圓的混合鍵合而言,處理不帶顆粒的裸片的基礎設施以及鍵合裸片的能力成為一項重大挑戰(zhàn)。” Uhrmann說,“雖然可以從晶圓級復制或改寫芯片級的界面設計和預處理,但在芯片處理方面仍存在許多挑戰(zhàn)。通常,后端工藝(例如切塊、裸片處理和在薄膜框架上的裸片傳輸)必須適應前端清潔級別,才能在裸片級別獲得較高的粘合率。”

Uhrmann說,“晶圓對晶圓的鍵合方式正在發(fā)展,當我看到這種方式的過程時,看到工具開發(fā)的方向時,我認為這是一項非常復雜的集成任務,但是臺積電這樣的公司正在推動這個行業(yè)的發(fā)展,我們可以對其抱有期待。”

封裝的混合鍵合與傳統(tǒng)的IC封裝在某些方面是不同的。傳統(tǒng)上,IC封裝是在一個OSAT(Outsourced Semiconductor Assembly and Test,委外封測代工廠)或封裝廠中進行的,而銅混合鍵合卻是在晶圓廠的潔凈室中進行,而不是OSAT中。與傳統(tǒng)封裝處理尺寸缺陷不同,混合鍵合對微小的納米級缺陷非常敏感,需要工廠級的潔凈室來防止微小缺陷干擾生產(chǎn)過程。

缺陷控制至關重要。賽博光學研發(fā)副總裁Tim Skunes說,“考慮到這些工藝使用已知的昂貴優(yōu)良裸片,失敗成本很高。在組件之間,有一些突起形成垂直的電氣連接,控制凸塊高度和共面性對于確保堆疊組件之間的可靠性至關重要。”

事實上,已知良好模具(KGD)至關重要。KGD是符合給定規(guī)格的未包裝零件或裸片,如果沒有KGD,封裝可能遭受低產(chǎn)或失敗。

KGD對封裝廠也很重要。“我們收到裸片,對其進行封裝,并交付功能產(chǎn)品,合作方會要求我們提供非常高的產(chǎn)量。”東方電氣工程技術營銷總監(jiān)曹麗紅在最近的一次活動中表示,“因此,我們希望KGD能夠經(jīng)過充分測試并功能良好。”

裸片對晶圓的混合鍵合類似于晶圓對晶圓的工藝。最大的區(qū)別在于芯片是用高速倒裝芯片鍵合器中檢測或在其他芯片上切割和堆疊的。

Xperi的裸片對晶圓混合鍵合流程圖,圖片源自:Xperi

整個過程從晶圓廠開始,使用各種設備在晶圓上加工芯片,這部分被稱之為前段生產(chǎn)新(FEOL)。在混合鍵合中,兩個或更多的晶圓在流動過程中被加工。之后,晶圓被運送到生產(chǎn)線后端(BEOL)的特殊部分,使用不同的設備對晶圓進行單一鑲嵌工藝。

單一鑲嵌工藝是一項成熟的技術,通常是將氧化物材料沉淀在晶圓上,然后用微小的通孔對氧化物材料進行蝕刻并繪制圖案,最后通過沉積工藝填充銅,繼而在晶圓表面上形成銅互連或焊盤,銅焊盤以微米為單位,相對較大。這一過程與當今先進的晶圓廠芯片生產(chǎn)類似,但對于高級芯片而言,最大的區(qū)別在于銅互連是納米級別的。

上述流程就是Xperi的新裸片對晶圓的銅混合鍵合工藝的最初模式,其他公司使用類似或有細微不同的流程。

Xperi晶圓對晶圓工藝的第一步是使用化學機械拋光(CMP)拋光晶圓表面,即通過化學方法和機械方法拋光表面。在這一過程中,銅焊板略微凹陷在晶圓表面,得到淺而均勻的凹槽,有較好的良率。

不過,化學機械拋光(CMP)實現(xiàn)過程困難,拋光過度會使銅焊盤的凹槽太大,最終可能導致某些焊盤無法接和,拋光不足則會留下銅殘留物造成短路。針對這一問題,Xperi開發(fā)出200nm和300nm CMP功能。Xperi工程部副總裁Laura Mirkarimi表示:“在過去十年中,CMP技術在設備設計、材料選擇和監(jiān)控方面都進行了創(chuàng)新,能夠達到精準控制,讓過程可重復且具有穩(wěn)定性。”

在經(jīng)過CMP之后,需要使用原子力顯微鏡(AFM)和其他工具對晶圓表面進行測量,這一部分非常關鍵。

KLA的Hiebert說:“對于混合鍵合,測量鑲嵌焊盤形成后的晶圓表面必須采用亞納米精度,以確保銅焊盤苛刻的凹凸要求。銅混合鍵合的主要工藝挑戰(zhàn)包括晶圓表面缺陷控制、晶圓表面輪廓納米級控制以及控制頂部和底部芯片上的銅焊盤的對準。隨著混合鍵距變小,例如晶圓對晶圓間距小于2μm或裸片對晶圓間距小于10μm,這些表面缺陷、表面輪廓和鍵合焊盤對準挑戰(zhàn)變得更加重要。”

不過這可能還不夠,在某些時候,還會考慮到探測。FormFactor高級副總裁Amy Leong表示:“傳統(tǒng)上認為直接在銅焊盤或銅凸塊上進行探測是不可能的,如何在探針尖端和凸塊之間保持穩(wěn)定的電接觸是需要關注的重點。”

為此,F(xiàn)ormFactor開發(fā)了一種基于MEMS的探針設計,稱為Skate。結(jié)合低接觸力,尖端會輕柔地穿過氧化層,從而與凸塊形成電接觸。

完成計量步驟后,還需要對晶圓進行清潔和退火處理,然后再使用刀片或隱形激光切割系統(tǒng)在晶圓上切割芯片,這將產(chǎn)生用于封裝的單個裸片。裸片切割極具挑戰(zhàn)性,若切割不當則會產(chǎn)生顆粒、污染物和邊緣缺陷。

KLA的Hiebert說:“對于裸片之間的混合鍵合,晶圓切割和裸片處理增加了額外的顆粒生產(chǎn)源,必須對其進行管理。由于晶圓的污染程度低得多,因此正在研究對晶圓對晶圓進行離子切割的混合鍵合方案。”

切割之后是粘合,這一步驟需要使用倒裝芯片鍵合機直接從切割框架中拾取芯片,然后將芯片放置在主晶圓或其他芯片上,這兩個結(jié)構在常溫下立即結(jié)合。在銅混合鍵合中,芯片或晶圓先使用電介質(zhì)鍵合,再進行金屬互連。

粘合過程對粘合劑的對準精度提出挑戰(zhàn),在某些情況下,對準精度需要達到幾微米,業(yè)界一般需要達到亞微米級別。

“盡管裸片的對準是一項挑戰(zhàn),但倒裝芯片鍵合機已經(jīng)向前邁了一大步,”EV Group的Uhrmann說:“晶圓間鍵合正朝著覆蓋層小于100nm的方向發(fā)展,因此符合先進節(jié)點的要求。對于裸片對晶圓,通常精度和生產(chǎn)量之間存在依賴關系,其中較高的精度可以通過較低的總體生產(chǎn)量來平衡。由于工具已經(jīng)針對諸如焊接和熱壓連接之類的后端工藝進行了優(yōu)化,因此1μm的規(guī)格在很長一段時間能都是足夠的。混合式芯片對晶圓鍵合改變了設備設計,這是由精度和設備清潔度引起的,下一代工具的規(guī)格將遠遠低于500nm。”

業(yè)界正在為這一目標而努力,在ECTC上,BE半導體公司(Besi)展示了一種新的混合芯片-晶圓鍵合機原型的第一項成果,最終規(guī)格目標為200nm、ISO 3潔凈室環(huán)境以及2000 UPH的300 mm晶圓基板。該機器包括零件晶圓臺、基板晶圓臺以及鏡面拾取和放置系統(tǒng)。該公司表示,機器會根據(jù)生產(chǎn)流程的需要自動更換基板和晶圓組件,且為實現(xiàn)高精度,公司發(fā)布了用于快速穩(wěn)固高精度對準的光學硬件。

不過,裸片對準的探索仍未停止,往后可能會出現(xiàn)新的對準問題或缺陷,與所有封裝一樣,混合粘合的2.5D和3D封裝可能需要經(jīng)歷更多的測試和檢查步驟。

小結(jié)

混合鍵合是一項可行的技術,可能催生新一類產(chǎn)品。不過客戶需要權衡其選擇并深挖其中的細節(jié),并不是一件容易的事情。

責任編輯:YYX

電子發(fā)燒友App

電子發(fā)燒友App

評論