本文以汽車電子的可編程邏輯基礎(chǔ)知識(shí)、FPGA 架構(gòu)、FPGA 實(shí)現(xiàn)技術(shù)、處理器內(nèi)核、SoPC 優(yōu)勢(shì)和處理器靈活性為例進(jìn)行了簡要討論。

大型可編程邏輯器件,如現(xiàn)場(chǎng)可編程門陣列 (FPGA) 和復(fù)雜可編程邏輯器件 (CPLD),自從幾十年前作為膠合邏輯的替代品和 ASIC 原型器件首次推出以來,其功能迅速發(fā)展。嵌入式加速器和微處理器使它們成為許多曾經(jīng)被認(rèn)為是 DSP 和 ASSP 專屬領(lǐng)域的應(yīng)用的有力候選者。一旦設(shè)計(jì)人員了解了 FPGA 和 CPLD 架構(gòu)的基礎(chǔ)知識(shí),他們就可以提高許多設(shè)計(jì)的性能、效率和設(shè)計(jì)周期。

可編程邏輯在其在 FPGA 和 CPLD 中達(dá)到最先進(jìn)的形式之前有很長的發(fā)展歷史。這兩種技術(shù)在架構(gòu)上的差異是由名稱本身來表示的。FPGA 的結(jié)構(gòu)非常類似于門陣列 ASIC,事實(shí)上,最初用于 ASIC 原型設(shè)計(jì)。CPLD 是一個(gè)可編程邏輯元件網(wǎng)絡(luò),這些元件連接起來可以創(chuàng)建一個(gè)更大的系統(tǒng)。

可編程邏輯基礎(chǔ)

通過回顧可編程陣列邏輯 (PAL) 的特性,可以快速了解 FPGA 和 CPLD 的基本配置思想,該特性始于一個(gè)用于對(duì)輸入進(jìn)行與運(yùn)算的廣泛的可編程與平面。OR 平面是固定的,這限制了可以進(jìn)行 OR 運(yùn)算的項(xiàng)數(shù)。添加了基本邏輯設(shè)備,如多路復(fù)用器、異或和鎖存器,還包括時(shí)鐘元件,如觸發(fā)器。

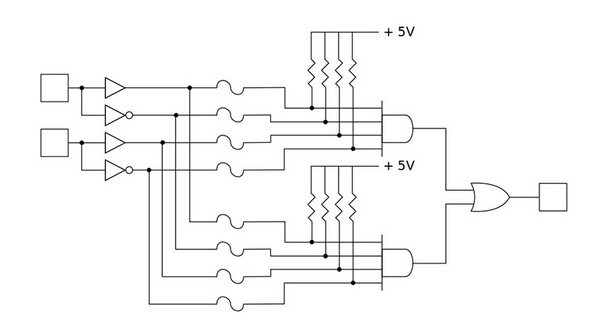

電路元件的這種組合使設(shè)計(jì)者能夠?qū)崿F(xiàn)大量邏輯功能,包括狀態(tài)機(jī)所需的時(shí)鐘時(shí)序邏輯。PAL 是速度非常快的設(shè)備,它取代了上一代設(shè)計(jì)中的大部分標(biāo)準(zhǔn)邏輯。圖 1 顯示了一個(gè)基本的 PAL,其中可編程元件(顯示為熔絲)將真輸入和互補(bǔ)輸入都連接到與門。AND 門,也稱為乘積項(xiàng),它們被 OR 運(yùn)算在一起以形成乘積和邏輯陣列。

簡化 PAL

CPLD 和 FPGA 在 PAL 和 ASIC 門陣列之間創(chuàng)建了一個(gè)愉快且可擴(kuò)展的媒介。CPLD 與 PAL 一樣快,但更復(fù)雜。FPGA 接近門陣列的復(fù)雜性并且是可編程的。

CPLD 架構(gòu)

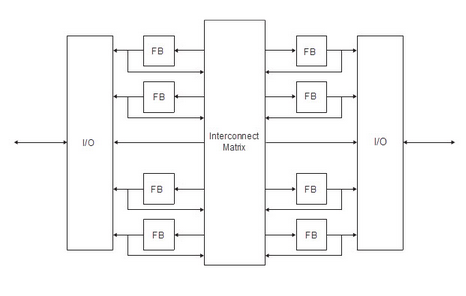

盡管每個(gè) CPLD 供應(yīng)商都有其獨(dú)特的實(shí)現(xiàn)方式,但所有 CPLD 都具有由功能塊 (FB)、輸入/輸出塊 (I/O) 和互連矩陣組成的共同特征。CPLD 使用特定于制造商技術(shù)的元素進(jìn)行編程。存儲(chǔ)器件可以是 EPROM 單元、EEPROM 單元或閃存 EPROM 單元。圖 2 顯示了典型 CPLD 的架構(gòu)。

簡化的 CPLD 架構(gòu)

FPGA架構(gòu)

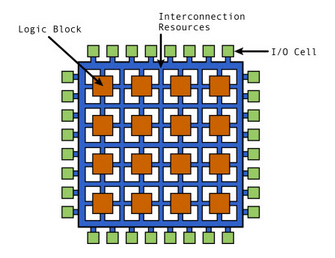

FPGA 架構(gòu)與 ASIC 相似,但與 CPLD 完全不同。通用 FPGA 架構(gòu)由一組可配置邏輯塊 (CLB)、I/O 焊盤和可編程互連組成,如圖 3 所示。添加時(shí)鐘電路以將時(shí)鐘信號(hào)驅(qū)動(dòng)到每個(gè)邏輯塊。算術(shù)邏輯單元、存儲(chǔ)器和解碼器也是典型的元件。

基本FPGA架構(gòu)

FPGA 邏輯包含在 CLB 中,其中包含用于創(chuàng)建組合邏輯功能的 RAM,也稱為查找表 (LUT)。它還包含用于時(shí)鐘存儲(chǔ)元件的觸發(fā)器,以及用于在塊內(nèi)和外部資源之間路由邏輯的多路復(fù)用器。多路復(fù)用器還用于極性選擇和復(fù)位和清除輸入選擇。

FPGA 實(shí)現(xiàn)技術(shù)

FPGA 傳統(tǒng)上是根據(jù)用于存儲(chǔ) FPGA 邏輯配置的存儲(chǔ)器技術(shù)來描述的。目前使用的有四種,每種都有其優(yōu)點(diǎn)和缺點(diǎn):基于 SRAM 的 FPGA、帶有內(nèi)部閃存的 SRAM、基于閃存的和反熔絲(也稱為 OTP,因?yàn)樗鼈兪且淮涡钥删幊痰模?/p>

基于 SRAM 的 FPGA 將邏輯單元配置存儲(chǔ)在組織為鎖存器陣列的靜態(tài)存儲(chǔ)器中。由于 SRAM 是易失性的,因此每次系統(tǒng)啟動(dòng)時(shí)都必須對(duì)此類 FPGA 進(jìn)行編程。有兩種基本的編程模式:

主模式,即 FPGA 從外部源(例如外部閃存芯片)讀取配置數(shù)據(jù)。

Slave 模式,F(xiàn)PGA 由外部主設(shè)備(例如處理器)進(jìn)行配置。通常,這是通過專用配置接口或使用邊界掃描 (JTAG) 接口完成的。

帶有內(nèi)部閃存的基于 SRAM 的 FPGA 包含內(nèi)部閃存塊,無需外部非易失性存儲(chǔ)器。

真正基于閃存的 FPGA 使用閃存作為配置存儲(chǔ)的主要資源,因此不需要外部非易失性存儲(chǔ)器。與基于 SRAM 的 FPGA 相比,該技術(shù)的功耗更低,并且更能容忍輻射的影響。

基于反熔絲 (OTP) 的 FPGA 與前面提到的技術(shù)不同,因?yàn)樗鼈冎荒芫幊桃淮巍#ǚ慈劢z裝置最初不傳導(dǎo)電流,但可以燒毀到傳導(dǎo)狀態(tài)。)

處理器核心

盡管可編程器件最初是作為膠合邏輯替代品開發(fā)的,但隨著門密度的增加,F(xiàn)PGA 和 CPLD 供應(yīng)商開始添加具有專用功能的電路,以補(bǔ)充未分配的門和邏輯功能。結(jié)果被稱為可編程芯片上的系統(tǒng) (SoPC),其中由處理器等復(fù)雜設(shè)備組成的整個(gè)系統(tǒng)被集成到單個(gè)可編程邏輯設(shè)備中。

今天,大多數(shù) FPGA 和 CPLD 供應(yīng)商提供的產(chǎn)品系列提供 MCU 和其他 IP 核的功能。使用內(nèi)核使系統(tǒng)設(shè)計(jì)人員可以訪問熟悉的開發(fā)工具集、操作系統(tǒng)和可選擇的性能以適應(yīng)應(yīng)用程序。

芯片優(yōu)勢(shì)

考慮使用包含 MCU 功能的 SoPC 有幾個(gè)令人信服的理由。首先是認(rèn)識(shí)到使用專用 MCU 的隱性成本。例如,如果部件沒有正確的功能組合,則必須開發(fā)外部邏輯和軟件來填補(bǔ)功能漏洞。雖然 MCU 供應(yīng)商提供具有特殊功能的設(shè)備以適應(yīng)特定應(yīng)用,但這些芯片并未考慮可能需要(例如,在很短的時(shí)間內(nèi)需要新接口或外設(shè))的動(dòng)態(tài)市場(chǎng)條件。

示例:汽車電子的處理器靈活性

汽車對(duì)集成 MCU 有著無限的需求。每個(gè)主要系統(tǒng)——發(fā)動(dòng)機(jī)控制、制動(dòng)、底盤和娛樂系統(tǒng),僅舉三個(gè)——至少有一個(gè)。傳統(tǒng)上,需求是通過特定于應(yīng)用程序的 MCU 來滿足的,但隨著應(yīng)用程序(和 MCU 變體)數(shù)量的增加,這種策略受到質(zhì)疑。汽車制造商正在尋找更靈活、更易于定制的解決方案,在某些情況下,F(xiàn)PGA 就是答案。

編輯:hfy

-

微控制器

+關(guān)注

關(guān)注

48文章

7926瀏覽量

153906 -

FPGA

+關(guān)注

關(guān)注

1644文章

21993瀏覽量

615570 -

cpld

+關(guān)注

關(guān)注

32文章

1257瀏覽量

171188 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

524瀏覽量

44639

發(fā)布評(píng)論請(qǐng)先 登錄

可編程邏輯控制器PLC物聯(lián)網(wǎng)平臺(tái)有哪些功能

CY8C40xx系列32 位 PSOC? Arm? Cortex? 微控制器Cypress

TMS320C6000 DSP軟件可編程鎖相環(huán)控制器指南

PLC可編程控制器的簡介

可編程電阻焊控制器:智能化工業(yè)焊接新解決方案探究

FPGA 與微控制器優(yōu)缺點(diǎn)比較

2024年星閃進(jìn)入規(guī)模商用快車道

可編程邏輯控制器——安全威脅和解決方案

可編程控制器在自動(dòng)化控制領(lǐng)域有哪些應(yīng)用?

基于微控制器的設(shè)計(jì)走上快車道的可編程邏輯

基于微控制器的設(shè)計(jì)走上快車道的可編程邏輯

評(píng)論