一種增加音頻轉(zhuǎn)換器系統(tǒng)動(dòng)態(tài)范圍的常用技術(shù)是使用相同的信號(hào)和輸出總和并行操作兩個(gè)轉(zhuǎn)換器通道。相關(guān)信號(hào)的總和使信號(hào)電平增加 6 dB,而不相關(guān)噪聲源的總和僅使噪聲電平增加 3 dB。

CS5381 的實(shí)施要求

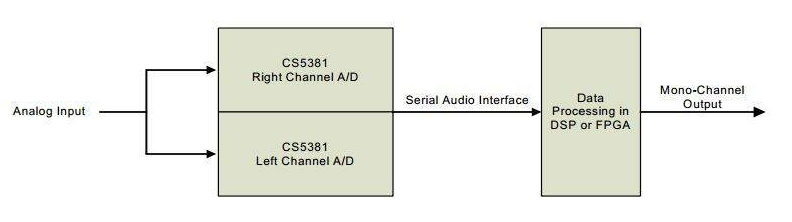

圖 1 所示的框圖顯示了 CS5381 A/D 的實(shí)現(xiàn)。請(qǐng)注意,相同的模擬信號(hào)應(yīng)用于 CS5381 內(nèi)的每個(gè) A/D 轉(zhuǎn)換器。然后在數(shù)字信號(hào)處理器 (DSP) 或現(xiàn)場(chǎng)可編程門(mén)陣列 (FGPA) 中執(zhí)行所需的數(shù)學(xué)運(yùn)算。

需要注意的是,加法(或減法)必須使用同步采樣和時(shí)間對(duì)齊的數(shù)據(jù)對(duì)來(lái)執(zhí)行。在串行音頻接口內(nèi),左后右聲道數(shù)據(jù)對(duì)是同步采樣數(shù)據(jù)。然而,右聲道數(shù)據(jù)對(duì)與左聲道數(shù)據(jù)對(duì)相對(duì)于彼此在時(shí)間上偏移一個(gè)采樣周期,并且這些對(duì)的相加或相減將產(chǎn)生錯(cuò)誤的結(jié)果。

單模框圖

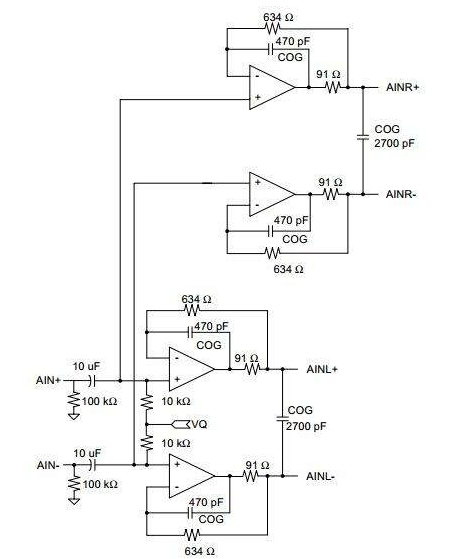

CS5381 在單聲道模式下的推薦模擬輸入緩沖器 CS5381的實(shí)現(xiàn)需要單獨(dú)的輸入緩沖器級(jí)用于差分模擬輸入。已證明驅(qū)動(dòng)兩個(gè)差分輸入的單個(gè)緩沖器會(huì)導(dǎo)致不可接受的失真水平。推薦的緩沖器拓?fù)渑c CS5381 評(píng)估板 CDB5381 上顯示的幾乎相同。圖 2 中的示意圖是方程 eo = A/2 + B/2 的建議緩沖區(qū)實(shí)現(xiàn)。

CS5381 推薦的同相配置緩沖器實(shí)現(xiàn)

演示技術(shù)

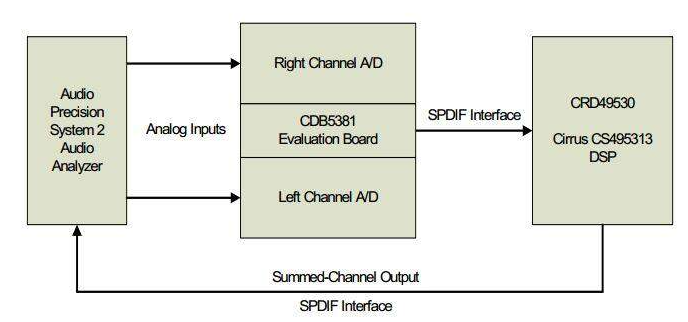

使用標(biāo)準(zhǔn) Cirrus Logic 評(píng)估板和 Audio Precision System 2 組裝測(cè)試系統(tǒng)來(lái)演示該技術(shù)是一件相對(duì)簡(jiǎn)單的事情。圖 3 中的框圖顯示了一個(gè)測(cè)試設(shè)置,其中包括 CDB5381 和 CRD43530,評(píng)估CS5381 A/D 和 CS495313 音頻 DSP 板。Audio Precision System 2 是模擬信號(hào)的來(lái)源,也是用于生成性能數(shù)據(jù)和繪圖的分析工具。評(píng)估板和 Audio Precision System 2 之間的數(shù)字互連是標(biāo)準(zhǔn)的 S/PDIF (IEC-60958) 接口。評(píng)估是在 48 kHz 采樣率下進(jìn)行的,但性能改進(jìn)在所有采樣率下都有效。

測(cè)試系統(tǒng)框圖

編輯:hfy

-

FGPA

+關(guān)注

關(guān)注

1文章

25瀏覽量

16230 -

數(shù)字信號(hào)處理器

+關(guān)注

關(guān)注

5文章

481瀏覽量

27763 -

音頻轉(zhuǎn)換器

+關(guān)注

關(guān)注

0文章

24瀏覽量

45407

發(fā)布評(píng)論請(qǐng)先 登錄

EEPROM芯片內(nèi)部的1路14bit ADC, ADC精度受使用通道數(shù)和采樣率是怎么樣的?

噪聲與ADC的范圍和位數(shù)是什么關(guān)系呢?怎樣選用和匹配?

多通道DAC的每個(gè)輸出通道能通過(guò)增加電容來(lái)達(dá)到輸出連續(xù)嗎?

AN-1279: 如何過(guò)采樣5 MSPS、18/16位精密SAR轉(zhuǎn)換器以便增加動(dòng)態(tài)范圍

ADC344X的外部同步輸入SYSREF范圍是-0.3~(AVDD + 0.3 = 2.1)V,是否可以通過(guò)FPGA輸出1.8V信號(hào)來(lái)直接驅(qū)動(dòng)?

如何通過(guò)TLA2528獲取8個(gè)通道的adc值?

PCM1808的通道溢出、動(dòng)態(tài)范圍窄是什么原因?qū)е碌模吭趺唇鉀Q?

adc0809輸入電壓范圍 adc0809和adc0808區(qū)別

什么是無(wú)雜散動(dòng)態(tài)范圍 (SFDR)?為什么 SFDR 很重要?

通過(guò)通道求和提高音頻ADC的動(dòng)態(tài)范圍和SNR

使用TLV320ADC5140/6140和PCM5140-Q1/PCM6140-Q1中的動(dòng)態(tài)范圍增強(qiáng)器

ADS2806高動(dòng)態(tài)范圍、12位流水線式模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADS850高動(dòng)態(tài)范圍、14位模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADC3910Dx和ADC3910Sx小型單通道和雙通道ADC數(shù)據(jù)表

如何通過(guò)通道總和增加 ADC 動(dòng)態(tài)范圍

如何通過(guò)通道總和增加 ADC 動(dòng)態(tài)范圍

評(píng)論