DDR的歷史,就是一個SI技術(shù)變革的過程,說白了就是拓撲與端接之爭。DDR2使用的是T拓撲,發(fā)展到DDR3,引入了全新的菊花鏈—fly-by結(jié)構(gòu)。使用fly-by并不完全因為現(xiàn)在的線路板越來越高密,布局空間越來越受限,主要原因還是DDR3信號傳輸速率變得更快了,T型拓撲已經(jīng)不能滿足高速傳輸?shù)囊蟆?/p>

高速先生前期的文章中提到了fly-by,并且早期的文章對fly-by結(jié)構(gòu)也做過一些介紹。看過文章的網(wǎng)友肯定還記得文中的一些觀點,例如:不是所有的DDR都可以使用fly-by;為提高負載的信號質(zhì)量,fly-by結(jié)構(gòu)可以進行容性負載補償…

這期文章的主題是圍繞拓撲結(jié)構(gòu)與端接展開的,我也來說說我對fly-by結(jié)構(gòu)的一些理解。

Stub長度決定信號質(zhì)量

我們經(jīng)常見到的使用fly-by結(jié)構(gòu)將內(nèi)存顆粒串聯(lián)起來的實例如圖1和圖2

圖1

圖2

圖1中,stub長度約為200mil,圖2 stub約為20mil。這兩種做法哪種信號質(zhì)量更好些呢?高速先生為此專門做仿真驗證了一下。

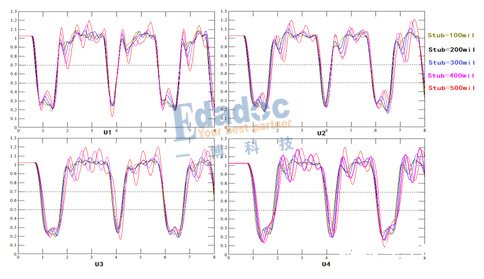

圖3各段線阻抗都取50 ohm。只改變stub長度,四個接收端波形如下圖4所示:

圖4

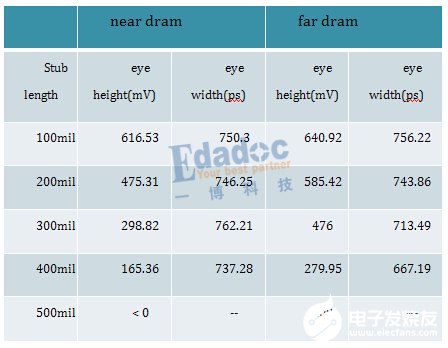

從波形可以看出,隨著stub長度的增加,波形的過沖現(xiàn)象越來越嚴重。為更好的評估stub變長對信號帶來的影響,我們將近端和遠端接收端的眼圖對比如下:

圖5

由上圖5可知,隨著Stub變長,眼高逐漸變小,這再次驗證了:stub越長信號質(zhì)量越差。

阻抗補償有利于改善信號質(zhì)量

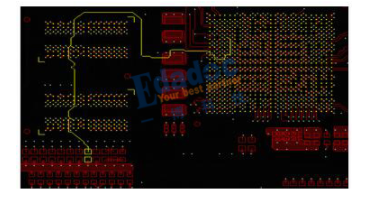

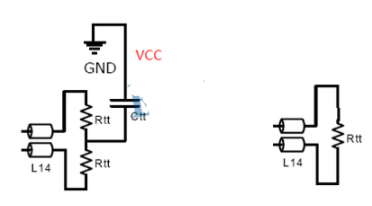

設(shè)計過DIMM條的小伙伴們都會注意這樣一個細節(jié),就是主網(wǎng)絡(luò)走線要比到各個分支走線粗,如下圖

圖6

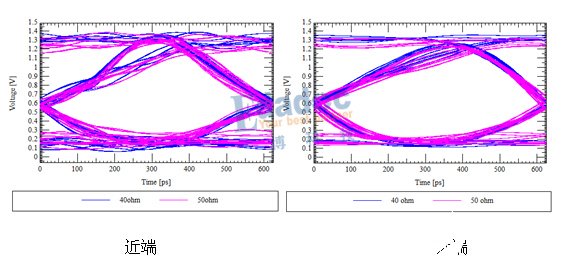

這么做真的可以改善信號質(zhì)量?空口無憑,我們還是用仿真數(shù)據(jù)來說話。搭建如下拓撲結(jié)構(gòu),只是改變主線段阻抗(最初阻抗都是50ohm),其他變量不變。

主線段阻抗分別取40ohm與50ohm,近端和最遠端負載眼圖對比如下圖7,圖7中藍色眼圖代表的是主干線阻抗為40ohm情況,紫色眼圖代表的是主干線阻抗是50ohm的情況。

圖7

由上圖可知,藍色眼圖比紫色眼圖張的更開,也就意味著主線段阻抗偏低信號質(zhì)量會更好。降低主線段阻抗或者提高后面分支的阻抗的確可以改善信號質(zhì)量,這個方法業(yè)內(nèi)把它叫做容性負載補償。特別是那種負載很多的結(jié)構(gòu),一條鏈路上串了8片或者10片DDR顆粒的,做一下容性負載補償對提升信號質(zhì)量有很大的幫助。

編輯:hfy

-

阻抗

+關(guān)注

關(guān)注

17文章

970瀏覽量

47179 -

DDR

+關(guān)注

關(guān)注

11文章

732瀏覽量

66593 -

拓撲結(jié)構(gòu)

+關(guān)注

關(guān)注

6文章

327瀏覽量

39986 -

端接

+關(guān)注

關(guān)注

0文章

32瀏覽量

8459

發(fā)布評論請先 登錄

(工程實踐)DDR3 fly-by拓撲設(shè)計

FLY-BY拓撲,阻抗是怎么不連續(xù)的?

T型及Fly_by拓撲之應(yīng)用總結(jié)

【分享】Altium 4層核心板(菊花鏈拓撲)案例

案例分享之DDR拓撲結(jié)構(gòu)的選擇

DDR3采用fly-by拓撲為什么有的采用RTT上拉端接,而有的采用RC下拉端接?

我的板子之前是按照fly-by拓撲(菊花鏈)布線,之后板子縮小打算用T行拓撲布線,有用過的大神知道可以直接更改嗎?

請教一下DM8148的DDR控制器支持讀寫平衡嗎,沒找到描述,用fly-by拓撲,還是T型?

請問fly-by適用于多個芯片的情況效果一樣嗎?

不加端接電阻的快樂,你們絕對想象不到!

拓撲結(jié)構(gòu),拓撲結(jié)構(gòu)有哪些類型?

如何選擇DDR的拓撲結(jié)構(gòu)?怎樣去改善信號質(zhì)量呢?

FLY-BY拓撲結(jié)構(gòu):阻抗不連續(xù)到了什么程度呢

圍繞拓撲結(jié)構(gòu)與端接展開,淺談對fly-by結(jié)構(gòu)

圍繞拓撲結(jié)構(gòu)與端接展開,淺談對fly-by結(jié)構(gòu)

評論