相比T拓?fù)洌琭ly-by在傳輸較高速率信號時更占優(yōu)勢一些,當(dāng)然fly-by也并不就是完美的,它自身也存在很多缺陷,例如使用fly-by,負(fù)載之間有延時差,導(dǎo)致信號不能同時到達(dá)接收端。為解決這個問題,DDR3引入了read and write leveling,但是fly-by由于分支結(jié)構(gòu)的存在,通道本身就存在一些缺點(diǎn)。例如:通道阻抗不連續(xù);容性突變對時序的影響等等。下面就來詳細(xì)的分析一下。

分支處阻抗的不連續(xù)程度受stub長度影響

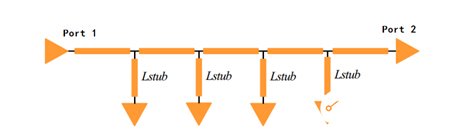

信號通道中只要有分叉就會存在阻抗的不連續(xù),fly-by結(jié)構(gòu)處處是分叉,阻抗不連續(xù)問題就很突出,到底這種阻抗不連續(xù)到了什么程度呢?下面就通過仿真實(shí)例來看看。在仿真軟件中搭建如下拓?fù)浣Y(jié)構(gòu),掃描通道S參數(shù),再利用S參數(shù)反推出各個節(jié)點(diǎn)的阻抗。

圖1

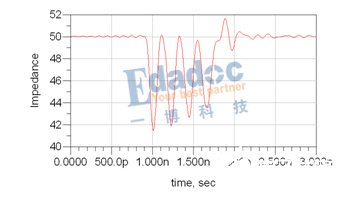

起初,我們將Stub長度都設(shè)定為100mil,掃描通道,得到通道的阻抗曲線如下

圖2

由上圖2可知,通道中有四次阻抗跌落,這些跌落分別對應(yīng)該傳輸線的四個分支。Stub的長度與阻抗跌落的程度是否呈正相關(guān)呢?為簡化分析過程,我們只允許通道中有一個Stub,掃描Stub長度,看看阻抗的變化趨勢

圖3

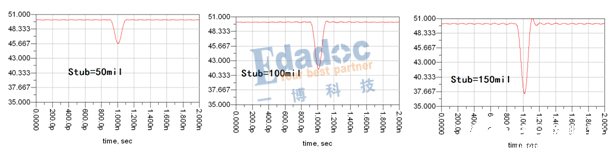

仿真的結(jié)果如下圖4所示。

圖4

上圖的結(jié)構(gòu)是不是很容易讓我們聯(lián)想到過孔的Stub,沒錯,傳輸線上的Stub和過孔的Stub效應(yīng)差不多,只不過我們在仿真過孔的時候,一般會選擇三維建模,而且,過孔還考慮了焊盤的效應(yīng)。

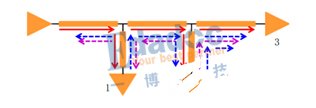

由圖4的三個波形曲線可知,Stub越長,阻抗掉的越低。為什么會這樣?傳輸線瞬態(tài)阻抗計算公式為Z=√(L/C)。就是信號感知的電感與電容的比值再開根號。因為分叉處的傳輸線與主線之間是并聯(lián)關(guān)系,Stub就像并聯(lián)在傳輸線上的小電容,Stub越長,電容量越大,阻抗也就越低。當(dāng)然,fly-by結(jié)構(gòu)的分支較多,每個分叉處都存在阻抗不連續(xù),信號會在Stub之間來回反射,如圖5所示,所以分析起來比較復(fù)雜。

圖5

像這種復(fù)雜的反射,只能借助仿真軟件去評估它對信號的影響程度。為了解決這個問題,工程上一般會選擇在主通道末端接上上拉電阻。但是,末端端接只能解決末端反射問題,對于分支上的反射是不能完全消除的。

Stub電容效應(yīng)對傳輸延時的影響

我們知道,連接在通道中途的短樁線和主通道是并聯(lián)關(guān)系,而這些短樁線本身是有電容的,這就意味著這些小樁線相當(dāng)于一個個的小電容并聯(lián)在傳輸線中。由電容的頻率響應(yīng)曲線可知,電容對信號中的高頻分量的阻抗是很低的,也就是說信號中的高頻分量會因為通道中并聯(lián)的小電容被過濾掉。高頻分量的損失會導(dǎo)致信號的上升時間的變緩。到底是不是這樣呢?

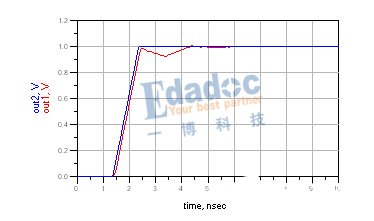

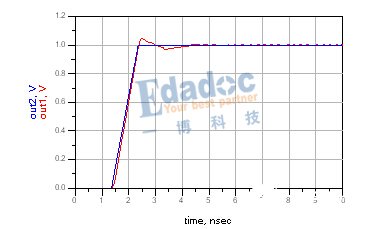

搭建如下拓?fù)洌聢D兩個通道的長度是完全一致的。驅(qū)動端阻抗與傳輸線阻抗相匹配,在驅(qū)動端加載一個上升沿為1ns的激勵。

圖7

和我們推測的一樣,連線中途的Stub會導(dǎo)致信號上升沿出現(xiàn)延遲的現(xiàn)象。因為: TD_0=Len√LC,信號在傳輸?shù)倪^程中,每遇到一個Stub就會導(dǎo)致一個小小的延遲,多次累加后就會出現(xiàn)一個較大的延遲。這對高速信號來說,是不可忽略的影響。

工程中會通過線寬補(bǔ)償來減小這種容性突變,效果究竟怎么樣呢,還是通過仿真來看一下。如上拓?fù)浣Y(jié)構(gòu),調(diào)高Stub以及樁線之間走線的阻抗,看看上升沿的變化。

圖8

由圖8可知,Stub以及Stub之間的走線阻抗拉高之后,上升沿延遲現(xiàn)象得到改善。容性突變導(dǎo)致的負(fù)反射也得到一定的補(bǔ)償。細(xì)心讀者可能會發(fā)現(xiàn),補(bǔ)償之后,反射導(dǎo)致的過沖問題又顯現(xiàn)出來,這可真是“按下葫蘆浮起瓢”。怎么辦?過沖問題只有交給端接電阻去解決了。

說了這么多,看來要想把fly-by結(jié)構(gòu)對信號的影響說清楚還真是沒那么容易。對于這種拓?fù)浣Y(jié)構(gòu),常規(guī)的串?dāng)_控制自是不必多說的,另外,還需要牢牢記住的就是:Stub能短就盡量做短些吧;在負(fù)載很多的情況下,做一下阻抗補(bǔ)償還是很有必要的。

編輯:hfy

-

DDR3

+關(guān)注

關(guān)注

2文章

283瀏覽量

43002 -

阻抗

+關(guān)注

關(guān)注

17文章

970瀏覽量

47124 -

拓?fù)浣Y(jié)構(gòu)

+關(guān)注

關(guān)注

6文章

327瀏覽量

39960

發(fā)布評論請先 登錄

(工程實(shí)踐)DDR3 fly-by拓?fù)?/b>設(shè)計

T型及Fly_by拓?fù)?/b>之應(yīng)用總結(jié)

【分享】Altium 4層核心板(菊花鏈拓?fù)?/b>)案例

案例分享之DDR拓?fù)?/b>結(jié)構(gòu)的選擇

DDR3采用fly-by拓?fù)?/b>為什么有的采用RTT上拉端接,而有的采用RC下拉端接?

我的板子之前是按照fly-by拓?fù)?/b>(菊花鏈)布線,之后板子縮小打算用T行拓?fù)?/b>布線,有用過的大神知道可以直接更改嗎?

請教一下DM8148的DDR控制器支持讀寫平衡嗎,沒找到描述,用fly-by拓?fù)?/b>,還是T型?

請問fly-by適用于多個芯片的情況效果一樣嗎?

如何解決PCB阻抗不連續(xù)問題

圍繞拓?fù)?/b>結(jié)構(gòu)與端接展開,淺談對fly-by結(jié)構(gòu)

如何選擇DDR的拓?fù)?/b>結(jié)構(gòu)?怎樣去改善信號質(zhì)量呢?

FLY-BY拓?fù)浣Y(jié)構(gòu):阻抗不連續(xù)到了什么程度呢

FLY-BY拓?fù)浣Y(jié)構(gòu):阻抗不連續(xù)到了什么程度呢

評論