DC-DC轉(zhuǎn)換器所產(chǎn)生的EMI,一直給無線和物聯(lián)網(wǎng)設(shè)備的設(shè)計(jì)人員造成困擾。寬帶諧波成分通常會(huì)達(dá)到1.5GHz,從而涵蓋大多數(shù)無線協(xié)議、蜂窩LTE和GPS/GNSS頻段。

在如何減少無線和物聯(lián)網(wǎng)設(shè)備自我產(chǎn)生的EMI方面,我已經(jīng)寫了幾篇文章并主持了幾場(chǎng)網(wǎng)絡(luò)研討會(huì),而解決這類EMI的關(guān)鍵方法之一,是實(shí)現(xiàn)適當(dāng)?shù)?a target="_blank">PCB設(shè)計(jì)。最近我就這個(gè)主題主持了一場(chǎng)很長(zhǎng)的網(wǎng)絡(luò)研討會(huì)。如果您錯(cuò)過了這個(gè)演講,歡迎您觀看其網(wǎng)絡(luò)錄像回放。這場(chǎng)研討會(huì)中探討了幾個(gè)有關(guān)PCB設(shè)計(jì)和降低DC-DC轉(zhuǎn)換器EMI的問題,我的回答如下。

問:什么時(shí)候可以以電源平面作為電路走線的參考?

圖1:常見的四層層疊示例,其EMI非常差。

這是個(gè)常見問題,它是由于使用了典型的四層和六層電路板設(shè)計(jì)所引起,其中電源平面和地回路平面通常完全分開(圖1)。高頻(>100kHz)信號(hào)實(shí)際上是電磁波,其返回電流通常以數(shù)字地回路作為參考,如果您了解這點(diǎn),那么您就能更好地理解為什么參考電源平面是個(gè)壞主意。這類返回電流需要找到一種方法“以某種方式”返回?cái)?shù)字回路,因此其所經(jīng)過的路徑可能會(huì)產(chǎn)生EMI。在我看來,當(dāng)且僅當(dāng)電源平面和返回平面之間實(shí)現(xiàn)緊密耦合并且通過去耦電容很好地實(shí)現(xiàn)旁路時(shí),才可以將非關(guān)鍵信號(hào)(低頻、控制信號(hào)等)以電源作為參考。對(duì)于典型的四層板和六層板層疊,則通常不是這種情況。在大多數(shù)情況下,以電源平面作為參考運(yùn)行高頻數(shù)字信號(hào),對(duì)EMI來說存在高風(fēng)險(xiǎn)。我建議您在設(shè)計(jì)電路板時(shí)參考我的四部分系列文章“Design PCBs for EMI”以實(shí)現(xiàn)低EMI。

問:“鋪地”是否有助于隔離噪聲信號(hào)?

隔離噪聲信號(hào)的最佳方法是實(shí)現(xiàn)適當(dāng)?shù)腜CB層疊。也就是說,所有高頻(>100kHz)數(shù)字信號(hào)的走線都應(yīng)與實(shí)心返回平面相鄰。這就可以抑制電磁波。返回平面的斷裂會(huì)導(dǎo)致EMI增加15至20dB(請(qǐng)參閱參考資料中我的視頻演示)。根據(jù)Eric Bogatin博士的說法,取決于電路板設(shè)計(jì),鋪地通常實(shí)際上并沒有幫助,而且還可能有害,因?yàn)樵谀承┣闆r下,鋪地可能會(huì)在返回平面上表現(xiàn)為“斷裂”。有興趣者可訪問他的網(wǎng)站,獲取更多有關(guān)PCB設(shè)計(jì)和鋪地的信息。

問:從電路板的頂部到底部運(yùn)行時(shí)鐘走線時(shí),在附近為返回電流增加通孔有多重要?

這要視情況而定,并且其答案通常也可以用來回答許多EMC問題!如果電源平面和返回平面之間的距離很近(最大2~3mil),并且電路板上有足夠的去耦電容,那么為返回電流路徑添加鄰近過孔就沒有那么重要了。但是,對(duì)于諸如時(shí)鐘之類的關(guān)鍵走線,我會(huì)添加一個(gè)或多個(gè)過孔以確保對(duì)電磁波嚴(yán)格控制。這里我再次向您推薦我上述“通過PCB設(shè)計(jì)降低EMI”的系列文章。

問:上升時(shí)間和下降時(shí)間對(duì)EMI有什么影響?脈沖寬度的上升和下降所占百分比應(yīng)是多少?

Eric Bogatin博士在他的Signal and Power Integrity Simplified, 3rd edition一書中對(duì)這個(gè)主題做出了出色的討論(請(qǐng)參見下面的推薦書列表)。簡(jiǎn)而言之,可以使用公式BW=0.35/RT,其中,BW(帶寬)以GHz為單位,RT(10~90%上升時(shí)間)以ns為單位。因此,對(duì)于1ns的上升時(shí)間,帶寬約為0.35×1GHz,即350MHz。脈沖寬度會(huì)影響諧波的幅度。隨著其減小,總振幅也將減小。隨著脈沖寬度的減小,到某個(gè)點(diǎn)后,上升時(shí)間和下降時(shí)間會(huì)開始變成一個(gè)圓角的脈沖(在固定RT/FT的情況下),因此存在某個(gè)點(diǎn),好的矩形脈沖形狀到此就開始瓦解。我不確定RT與脈沖寬度的百分比是否有通用規(guī)則。

問:電子僅以1cm/s的速度傳播?

這個(gè)問題與我對(duì)數(shù)字信號(hào)如何在PCB中傳播的解釋有關(guān)。我們中的大多數(shù)人都被教導(dǎo)(或至少暗示)了信號(hào)實(shí)際上是電子在銅線或走線中的流動(dòng),而且電子是以接近光速的速度而運(yùn)動(dòng)。盡管對(duì)于DC電路而言確實(shí)如此,但電子不會(huì)以接近光速的速度行進(jìn),因?yàn)樗鼈冊(cè)阢~原子中的結(jié)合非常緊密。在高頻(>100kHz)下,數(shù)字信號(hào)實(shí)際上是電磁波,它通過銅走線和返回平面之間的介電層傳播。在DC和100kHz之間存在一個(gè)過渡區(qū)域,在此,信號(hào)從純DC電流轉(zhuǎn)變?yōu)殡姶挪ā?/p>

圖2:地回路平面上的微帶截面圖,借此即可從物理上了解,數(shù)字信號(hào)在走線和返回平面之間的介電空間內(nèi)是以電磁波形式傳播。

這個(gè)電磁傳播模型由兩個(gè)元素組成:傳播波本身——其在電介質(zhì)(假設(shè)為FR4電介質(zhì))中傳播的速度約為光速的一半;傳導(dǎo)電流(即電子在銅原子中的流動(dòng))和位移電流(“通過”電介質(zhì))的組合(圖2)。這個(gè)傳導(dǎo)電流可以使用電流表來測(cè)量,但是電子僅以約1cm/s的速度運(yùn)動(dòng)。我發(fā)現(xiàn)在大多數(shù)領(lǐng)域和電波教科書中通常都沒有對(duì)這種數(shù)字信號(hào)傳播的物理模型進(jìn)行教授。但是,我推薦兩個(gè)參考文獻(xiàn):Eric Bogatin博士撰寫的Signal and Power Integrity Simplified, 3rd edition(第245至252頁),以及Ron Schmitt撰寫的Electromagnetics Explained – A Handbook for Wireless/RF, EMC, and High-Speed Electronics(第33~34、84~86和96~98頁)。另請(qǐng)參閱我的“通過PCB設(shè)計(jì)降低EMI”的系列文章。

問:具有集成電感的電源模塊是否對(duì)降低EMI更好?

是的,因?yàn)檩斎胼敵龌芈返拿娣e實(shí)現(xiàn)了最小化。一個(gè)例子是凌力爾特的“μModule”片上系統(tǒng)(SoC)。請(qǐng)參見圖3以及ADIμModule升降壓穩(wěn)壓器頁面。

圖3:這個(gè)來自凌力爾特公司的DC-DC轉(zhuǎn)換器的例子,顯示其將集成電感(在本例中為變壓器)Cin和Cout全部集成到了SoC中。這種設(shè)計(jì)最大程度地減少了噪聲電流回路,從而可以降低EMI。(圖片來源:凌力爾特)

問:開關(guān)節(jié)點(diǎn)平面下方直到底部是否需要開孔以減少電場(chǎng)耦合?

這是個(gè)很好的問題!顯然,我們希望最大程度降低開關(guān)節(jié)點(diǎn)(SW)到電感的走線的面積,以減少到該點(diǎn)的耦合,在上例中,該點(diǎn)可能開關(guān)高達(dá)42V的方波而產(chǎn)生強(qiáng)烈的電場(chǎng)(圖4)。

圖4:這是個(gè)典型的DC-DC降壓轉(zhuǎn)換器,其上顯示了開關(guān)節(jié)點(diǎn)(SW)和輸出電感。爭(zhēng)論的焦點(diǎn)是是否要在SW節(jié)點(diǎn)或電感或者兩者的附近將返回平面切掉。(圖片來源:凌力爾特)

幾年前,我覺得把開關(guān)節(jié)點(diǎn)(SW)區(qū)域中的返回平面切掉對(duì)于減少電容耦合很重要,直到我真正開始從物理角度研究數(shù)字(在上述情況中為功率開關(guān))的工作方式為止。雖然我現(xiàn)在堅(jiān)信返回平面在DC-DC轉(zhuǎn)換器的所有部分下面都應(yīng)保持為實(shí)心平面,但您的論點(diǎn)也不能完全忽視,這可能取決于實(shí)際情況。

EMC和PCB設(shè)計(jì)領(lǐng)域的著名專家Todd Hubing博士、Rick Hartley和Daniel Beeker都認(rèn)為,返回平面應(yīng)為實(shí)心。另一方面,我所認(rèn)識(shí)的信號(hào)完整性(SI)和配電網(wǎng)絡(luò)(PDN)專家,例如Steve Sandler,正在沿著您的思路進(jìn)行思考。目前,我已經(jīng)和Steve Sandler和Todd Hubing開始了一項(xiàng)研究,其中就包括對(duì)這個(gè)問題進(jìn)行調(diào)查。Steve已同意制作幾塊電路板來測(cè)試信號(hào)完整性和電源完整性,而我則會(huì)測(cè)量輻射發(fā)射和傳導(dǎo)發(fā)射。這個(gè)研究應(yīng)該會(huì)引起關(guān)注,而有可能最終形成技術(shù)論文。目前,我對(duì)實(shí)心返回平面的看法不會(huì)改變,除非得到其他證明。

問:使用吸波材料后,我們看到EMI衰減了。但是否需要將它放到電路內(nèi)部的某個(gè)其他地方(未知)而不是放在外面呢?

實(shí)際上,來自IC或電路走線的輻射發(fā)射,會(huì)受到有損鐵氧體材料吸收而轉(zhuǎn)化為熱量。

問:在DC-DC轉(zhuǎn)換器輸入和輸出上串聯(lián)鐵氧體磁珠,是否是個(gè)好主意?

結(jié)合我的RF設(shè)計(jì)背景,這是RF電路非常普遍的做法——我仍然相信該技術(shù)可能會(huì)獲得成功使用。近年來,隨著我研究電源完整性,我開始改變主意。為了獲得良好的PDN性能,我們不希望PDN中有任何串聯(lián)阻抗。已故的Steve Weir在其PowerCon演講中,以及Eric Bogatin博士和Larry Smith在其著作Principles of Power Integrity for PDN Design Simplified的最新教材中,都清楚地說明了這一點(diǎn)。如果確實(shí)想要在輸入或輸出濾波器中這樣做,那么就需要確保在鐵氧體磁珠和數(shù)字開關(guān)轉(zhuǎn)換器IC之間添加一個(gè)額外的大容量電容(4.7至27μF陶瓷)。我仍然不建議添加它。

編輯:hfy

-

emi

+關(guān)注

關(guān)注

53文章

3725瀏覽量

130384 -

物聯(lián)網(wǎng)

+關(guān)注

關(guān)注

2927文章

45949瀏覽量

388598 -

DC-DC轉(zhuǎn)換器

+關(guān)注

關(guān)注

10文章

653瀏覽量

56347

發(fā)布評(píng)論請(qǐng)先 登錄

PL5920 21V,2A,600KHz同步降壓DC/DC轉(zhuǎn)換器

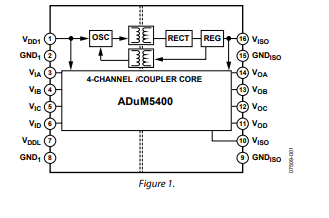

ADUM5400集成DC/DC轉(zhuǎn)換器的四通道隔離器技術(shù)手冊(cè)

DH30W10系列DC-DC轉(zhuǎn)換器CINCON

什么是DC-DC轉(zhuǎn)換器?

聞泰科技推出新款降壓DC-DC轉(zhuǎn)換器

CINCON電源DC-DC轉(zhuǎn)換器替換VICOR

熱敏電阻與DC-DC轉(zhuǎn)換器在能源存儲(chǔ)系統(tǒng)的應(yīng)用

AN29-關(guān)于DC-DC轉(zhuǎn)換器的一些想法

雙向DC-DC轉(zhuǎn)換器用戶指南

升壓型DC-DC轉(zhuǎn)換器關(guān)斷時(shí)的工作

面向新太空應(yīng)用的DC-DC轉(zhuǎn)換器解決方案

使用帶有DVFS的DC/DC轉(zhuǎn)換器的高Vin、高效率電源解決方案

降壓型與升壓型DC-DC轉(zhuǎn)換器的輸出紋波有什么不同

快速輸入轉(zhuǎn)換速率應(yīng)用中DC-DC轉(zhuǎn)換器的設(shè)計(jì)注意事項(xiàng)

關(guān)于PCB設(shè)計(jì)和降低DC-DC轉(zhuǎn)換器EMI的解決方案(一)

關(guān)于PCB設(shè)計(jì)和降低DC-DC轉(zhuǎn)換器EMI的解決方案(一)

評(píng)論