設計背景:

IIC 簡單來說,就是一種串行通信協(xié)議,IIC 的通信協(xié)議和通信接口在很多工程中有廣泛的應用,如數(shù)據采集領域的串行 AD,圖像處理領域的攝像頭配置,工業(yè)控制領域的 X 射線管配置等等。除此之外,由于 IIC 協(xié)議占用的 IO 資源特別少,連接方便,所以工程中也常選用 IIC 接口做為不同芯片間的通信協(xié)議。

設計原理:

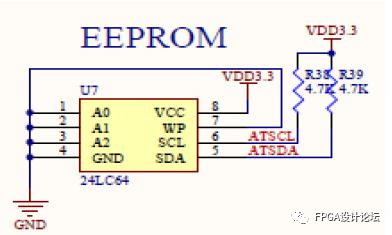

IIC 電路原理圖如下:

24LC64 各引腳定義:

1、A0,A1,A2 為 24LC64 的片選信號,由于 IIC 總線可以掛載多個 IIC 接口器件,所以每個器件都應該有自己的“身份標識”,通過對 A0,A1,A2 輸入不同的高低電平,就可以設置該 EEPROM 的片選信號。

2、WP 為讀寫使能信號,當 WP 懸空或者接地,EEPROM 可讀可寫,當 WP 接電源,EEPROM 只能讀不能寫。

3、SCL 為 IIC 接口的時鐘線。

4、SDA 為 IIC 接口的數(shù)據線。

IIC 接口的讀寫時序:

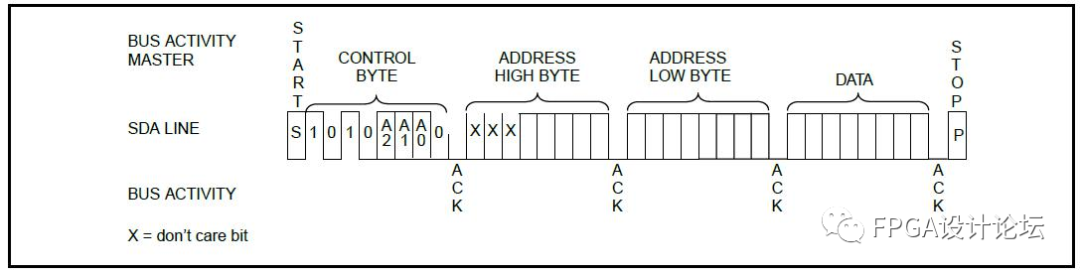

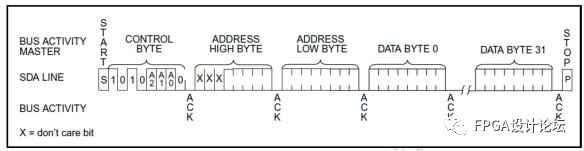

IIC 接口讀寫時序分為隨機讀寫(單字節(jié)讀寫)和頁面讀寫(多字節(jié)讀寫),先分析隨機讀寫(Byte Write/Read)時序。Byte Write 時序如下:

時序解讀:如果我們要向 EEPROM 寫入一個字節(jié),那么必須經過以下步驟:

1. 發(fā)送啟動信號

2. 發(fā)送控制字

3. 接收并檢測 EEPROM 發(fā)來的應答信號 ACK

4. 發(fā)送高字節(jié)地址位

5. 接收并檢測 EEPROM 發(fā)來的應答信號 ACK

6. 發(fā)送低字節(jié)地址位

7. 接收并檢測 EEPROM 發(fā)來的應答信號 ACK

8. 發(fā)送 8bit 有效數(shù)據

9. 接收并檢測 EEPROM 發(fā)來的應答信號 ACK

10.發(fā)送停止信號

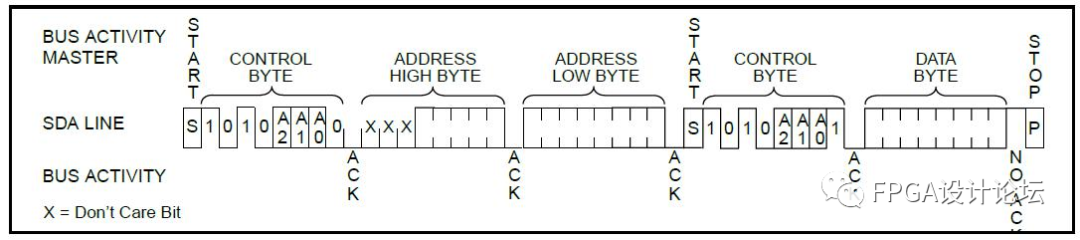

Byte Read 時序如下:

時序解讀:如果我們要從 EEPROM 讀出一個字節(jié),那么必須經過以下步驟:

1. 發(fā)送啟動信號

2. 發(fā)送控制字 1010_A2A1A0_0

3. 接收并檢測 EEPROM 發(fā)來的應答信號 ACK

4. 發(fā)送高字節(jié)地址位

5. 接收并檢測 EEPROM 發(fā)來的應答信號 ACK

6. 發(fā)送低字節(jié)地址位

7. 接收并檢測 EEPROM 發(fā)來的應答信號 ACK

8. 發(fā)送啟動信號

9. 發(fā)送控制字 1010_A2A1A0_1

10. 接收并檢測 EEPROM 發(fā)來的應答信號 ACK

11. 讀取一個字節(jié)數(shù)據

12. 發(fā)送 NO ACK 信號

13. 發(fā)送停止信號

接下來則需要分析各步驟具體意義:

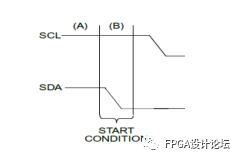

1.啟動信號

在 SCL 保持高電平期間,如果 SDA 出現(xiàn)由高到低的跳變沿,代表啟動信號

2. 控制字

我們的控制字為 1010_0000,其中 1010 為 EEPROM 的型號標識,為一組固定的序列,緊接著 A2,A1,A0 就是我們的片選信號,最后一位為讀寫控制位,低電平代表寫,高電平代表讀,我們這里首先需要對 EEPROM 寫入地址位,所以我們最后一位為 0。

3. 高/低位地址

由于 24LC64 有 64Kbit 的存儲空間,所以我們需要 13 位的地址位寬才能尋址所有的存儲空間,由于 IIC 協(xié)議規(guī)定只能以字節(jié)形式寫入,所以必須將 13 位的地址擴展為 16 位的地址,分為高八位和低八位,多出來的前三位填充任意數(shù)據即可,對我們的尋址地址沒有影響。

3. 停止信號

4. 應答信號 ACK

應答信號是由數(shù)據接收方發(fā)出的,當 SCL 為高電平期間,如果監(jiān)測到 SDA 為低電平,說明有應答信號。

5. 非應答信號 NO ACK

非應答信號也是由數(shù)據接收方發(fā)出的,當 SCL 為高電平期間,如果 SDA 為高電平,說明有非應答信號。

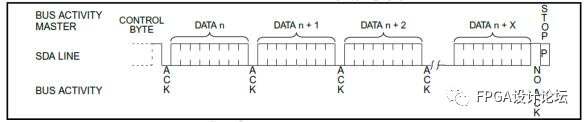

說明:由于 IIC 總線協(xié)議啟動和停止信號都是在 SCL 高電平期間發(fā)生跳變,這就決定了我們其他數(shù)據的改變只能發(fā)生在 SCL 低電平期間,在 SCL 為高電平期間,數(shù)據必須保持穩(wěn)定。即在 SCL 低電平改變數(shù)據,在 SCL 高電平采集數(shù)據。相比于單字節(jié)讀寫,頁面讀寫只是增加了幾個狀態(tài),具體時序如下,這里和后面的設計代碼不做詳細論述。

Page Write 時序如下:

Page Read 時序如下:

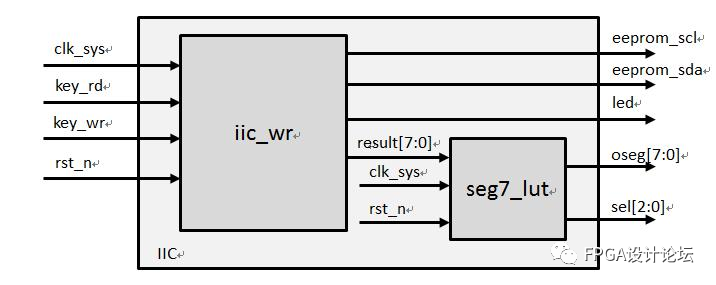

設計架構圖:

本設計用兩個按鍵控制 EEPROM 讀寫,當寫按鍵按下時,向EEPROM 某一固定地址寫入一個字節(jié)數(shù)據,當讀按鍵按下時,將該地址數(shù)據讀出,并顯示到數(shù)碼管,LED 燈是一個標志信號,LED 亮說明數(shù)據寫入完畢。設計架構如下:

設計代碼:

iic_wr 模塊代碼:負責進行 IIC 數(shù)據的讀寫

seg7_lut 模塊代碼,負責數(shù)碼管顯示

IIC 頂層模塊代碼:

tb 頂層測試模塊代碼:

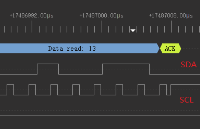

仿真圖:

隨機讀寫,仿真寫時序:

隨機讀寫,仿真讀時序:

在仿真時,需要將檢測應答的狀態(tài)跳過,直接向下一狀態(tài)跳轉,觀察讀寫時序,當讀寫按鍵按下時,都會產生對應的動作。

責任編輯:lq

-

FPGA

+關注

關注

1630文章

21803瀏覽量

606435 -

IIC

+關注

關注

11文章

302瀏覽量

38544 -

工業(yè)控制

+關注

關注

38文章

1470瀏覽量

86057

原文標題:FPGA入門課程《基于 FPGA 的 IIC設計》

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

請問DS90UB903Q的IIC工作頻率必須為100KHz嗎?

如何通過FPGA配置CDCI6214?

愛芯元智亮相IIC Shenzhen 2024

愛芯元智邀您相約IIC Shenzhen 2024峰會

MCU通過IIC口控制TLV320AIC3204,請問MCU的IIC接口和TLV320AIC3204的IIC接口對接時需要電平轉換嗎?

IIC信號線需要增加上拉電阻,是因為IIC的IO是什么

FPGA通過IIC給TLV320AIC3204寫入寄存器,讀出來的數(shù)據一直是零,為什么?

NSA2302iic通訊地址

示波器如何捕獲和分析IIC波形?

STM8L051F3手冊里是否有IIC作為slave的IIC address?

lis3dh使用IIC通訊,CS引腳懸空也能正常IIC通信嗎?

FPGA實現(xiàn)IIC協(xié)議的設計

GD32 MCU碰到IIC總線卡死怎么辦?

《基于FPGA的IIC設計》

《基于FPGA的IIC設計》

評論