問題1:對于DFX(Dynamic FunctioneXchange)設計,如果出現如下Error信息,該如何解決?

ERROR:[DRC HDPR-6]Logic illegally placed:Cell 'scl_OBUF_inst' is placed at site 'IOB_X0Y47' which belongs toreconfigurable Pblock 'pb_app'. This cell is not part of the reconfigurablelogic assigned to this Pblock, and should not be placed at this site [Solution] 可以按照下面的方法,兩步即可解決。

1.對于每個RM,如果其輸入/輸出引腳最終要被分配到某個FPGA管腳上,在代碼中手工實例化IOBUF,然后選擇OOC綜合方式

2.在頂層設計中,使相應的輸入/輸出引腳不要再插入IOBUF,在xdc中添加下面的約束。 set_propertyIO_BUFFER_TYPE NONE [get_ports

問題2:如何在RM(ReconfigurableModule)中使用ILA或VIO?

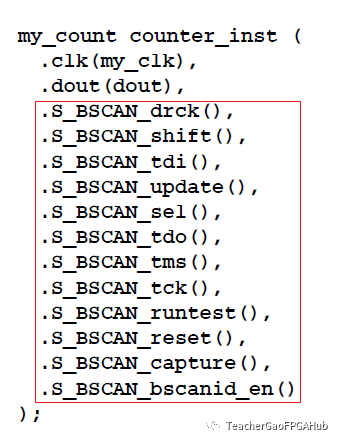

[Solution]目前在RM中使用ILA或VIO只能通過HDL代碼實例化的方式,暫不支持網表插入ILA的方式。采用HDL代碼實例化的方式還有一個問題就是如何使得RM中的ILA和Debug Hub相連。此時要通過如下方式解決。 首先在靜態區,要按如下方式預留12個端口。 Verilog版本:

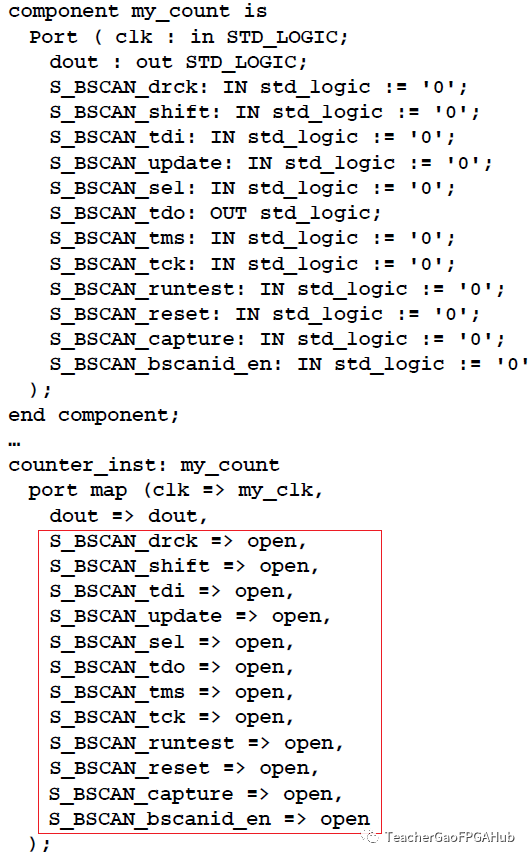

VHDL版本:

這里需要注意,使用VHDL時,在端口映射時要使用open,以保證端口初始值為0,若為1,則無法與Debug Hub相連。在RM的頂層RTL代碼中也預留這12個端口。最終這12個端口都會與Debug Hub相連。在綜合階段,Debug Hub可以被自動創建(此時為黑盒子),靜態區和RM都會有自己的Debug Hub。

問題3:哪個版本的ISE或Vivado可以支持Partial Reconfiguration?

[Solution]目前,PartialReconfiguration已經更名為Dynamic Function eXchange,簡稱為DFX。對于ISE,從12.x開始支持PR,對于Vivado,從2013.x開始支持PR。

問題4:PR支持哪些配置方式?

[Solution]PR可支持JTAG、SelectMAP、BPI、SPI和ICAP五種配置方式。 Tcl之$$a 80%的概率...... DSP58來了 AI Engine到底是什么?

責任編輯:xj

原文標題:DFX設計中可能遇到的幾個問題及解決方法

文章出處:【微信公眾號:Lauren的FPGA】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1630文章

21805瀏覽量

606555 -

DFx

+關注

關注

0文章

35瀏覽量

10592

原文標題:DFX設計中可能遇到的幾個問題及解決方法

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

關于DS90UB925Q的幾個問題求解

使用ADS1258有幾個問題求解

用ad1246采集數據,參考電壓2.5V有幾個問題請教

使用ADS5403遇到的幾個問題求解

關于TDA3116D2的幾個問題求解答

有關TAS5630B的模擬地和地的幾個問題求解

求助,關于D類功放的幾個問題求解

BCM中的開關檢測:集成MSDI解決方案與半分立解決方案

使用LM48901數字芯片遇到的幾個問題求解

求助,關于TRAVEO? II MCU安全調試的幾個問題求解

在USB中的MaxPktSize的幾個問題求解

如何在AMD Vivado? Design Tool中用工程模式使用DFX流程?

DFX設計中的幾個問題及其解決方案

DFX設計中的幾個問題及其解決方案

評論