學(xué)習(xí)電子工程的過程中離不開大量的實驗和動手練習(xí),就如同開車一樣,學(xué)習(xí)理論數(shù)載,如果從來沒有打幾把方向盤,踩幾腳油門然后再被教練緊急剎車幾次,仍然不會開車。正所謂,看別人做一百次,不如自己練一次。

1

門電路原理

在數(shù)字電路中,門電路是最基本的構(gòu)成單位,可以說,任何復(fù)雜的數(shù)字電路系統(tǒng)都可以通過我們耳熟能詳?shù)呐c門,非門,或門,與非門,異或門等等組合實現(xiàn)。

對于各種門電路的邏輯特征,想必大家都掌握得爐火純青,腦海里可以毫無壓力地隨時浮現(xiàn)著各種0和1的組合。

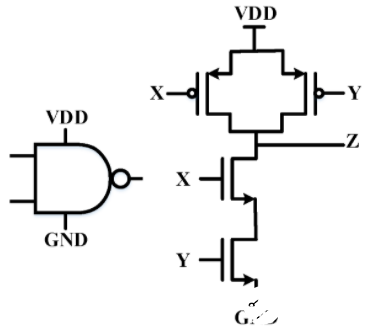

然而,搭建一個門電路實驗卻并不容易!我們以下面的與非門電路為例。

圖1 與非門電路

表1 與非門真值表

傳說中,如果想做一個與非門的數(shù)字電路實驗,可以通過以下兩種方法:

熱愛模電的朋友們可以通過MOS管+面包板+電源+跳線以及若干小時的反復(fù)調(diào)試。

土豪朋友們對此不屑一顧,直接拍幾千塊買一臺數(shù)字電路實驗儀。

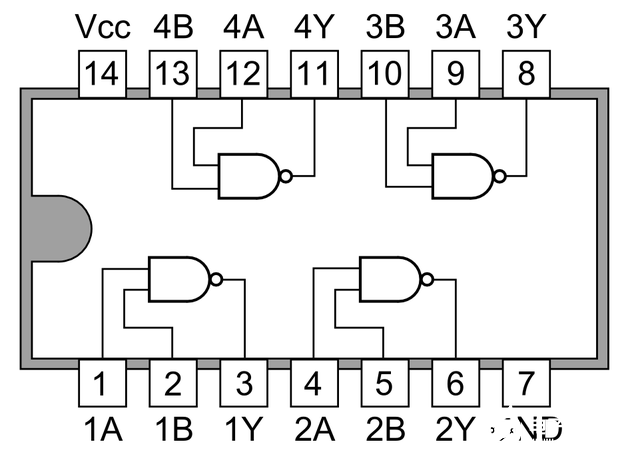

當(dāng)然,既沒有那么熱愛模電,也沒有那么多軟妹紙的朋友門仍然有更合適的辦法,那就是通過邏輯芯片。比如大家熟悉的7400系列的邏輯芯片,只需要接上電源,再配上開關(guān),LED等器件,就可以通過實驗方式對與非門的邏輯和電氣特性進行直觀地學(xué)習(xí),比如采用7400 Quad2的與非門邏輯芯片。

圖2 與非門邏輯芯片

因為我們要觀察實驗現(xiàn)象,因此需要配上開關(guān)和LED燈,使得實驗可以可視化。當(dāng)然,作為習(xí)慣了課上學(xué)習(xí)1+1=2,考試見到

的后浪,肯定不能滿足于這個簡單的實驗。現(xiàn)在,在上一個練習(xí)的基礎(chǔ)上,我們來嘗試構(gòu)建以下門電路組合。

圖3 組合門電路

嵌入式專欄

2

門電路實現(xiàn)

以下是某位同學(xué)獨特的實現(xiàn)方式:

圖4

雖然我們還通過軟件仿真的方式構(gòu)建上述電路并觀察波形,然而和電路上進行實打?qū)嵉牟僮飨啾冉K究是有質(zhì)的差別。畢竟靠著模擬飛車駕齡20年資歷上路還是要被警察叔叔帶走的。

不難看出,畫門電路容易,對門電路進行實驗很難,對各式各樣奇葩組合的門電路進行實驗更是難上加難。然而這一切在FPGA面前都只是談笑風(fēng)生。

FPGA,英文全稱Field Programmable Gate Array,是一種可以通過某百科或搜索引擎查找到并且看了之后不明覺厲的東西。在此,我們主要介紹一下FPGA的部分特點,以及如何使其與數(shù)字電路實驗進行結(jié)合。

首先問大家一個問題:我們在計算3x7=21或者5x8=40的時候,有誰是通過最原始的乘法原理推導(dǎo)并計算出來的,如果有,請在底部留言并獲得所有人的膜拜。相信大部分人都可以在半秒內(nèi)給出準(zhǔn)確答案,為什么?因為我們都背過九九乘法表,只要是在這個范圍內(nèi)的任意乘法我們的大腦都可以瞬間對應(yīng)出計算結(jié)果。相信大家對當(dāng)年的112=121,122=144,132=169…等等還歷歷在目。

之所以我們可以在一定范圍內(nèi)進行準(zhǔn)確和快速的計算,是因為我們的大腦里儲存了一個擁有大量數(shù)據(jù)的查找表,在一定范圍內(nèi)的輸入數(shù)據(jù)我們都可以迅速在表中找到對應(yīng)答案。其實,F(xiàn)PGA的運算處理方式就類似于我們的大腦。它擁有一個可以儲存大量數(shù)據(jù)的查找表,只要我們通過程序定義出輸入與輸出之間的邏輯關(guān)系,F(xiàn)PGA就可以按照該邏輯關(guān)系自行對其內(nèi)部結(jié)構(gòu)進行重新定義,直白地說,就是我們可以隨時給FPGA進行洗腦,而后者可以永遠(yuǎn)不計回報,心甘情愿地被洗腦。

接下來我們就快速展示一下如何通過FPGA展示圖3所示的門電路。既然要對FPGA進行洗腦,肯定需要語言。在這里我們采用簡單通俗的Verilog語言,通過描述門電路的方式,以16行代碼輕松在FPGA上搭建上述門電路。

module custblock ( input wire A, //定義輸入A input wire B, //定義輸入B input wire C, //定義輸入C input wire D, //定義輸入D output wire Y1, //定義輸出Y1 output wire Y2 //定義輸出Y2 ); wire s1,s2,s3; //定義中間變量 nand (s1,A,B); //(輸出,輸入,輸入) or (s2,C,D); // 調(diào)用基本門電路 xnor (Y1,s1,C); and (s3,C,s2); xor (Y2,C,s3); endmodule

將上述代碼導(dǎo)入FPGA之后,就等于在FPGA上構(gòu)建出了一個模塊,輸入端分別是A,B,C,D,輸出端分別是Y2,Y1,且內(nèi)部結(jié)構(gòu)和圖3中所示的功能完全一樣。

圖5

不過,對于實驗來說,僅僅在FPGA上搭建出該門電路模塊還是不夠的,我們還需要允許實驗者對該電路進行調(diào)試并觀察現(xiàn)象,因此還需要有相應(yīng)的可操作/觀察元件與FPGA配合使用。接下來就是我們備受歡迎的小腳丫FPGA登場的時候了。

圖6 小腳丫FPGA核心板

從示意圖中可以看出,小腳丫FPGA帶有多個板載外設(shè),如開關(guān),LED和數(shù)碼管等,可以對絕大部分?jǐn)?shù)字電路進行生動的實驗操作。小腳丫配有USB下載器,可以通過一根USB線實現(xiàn)供電和程序下載。板上的36個多功能I/O接口可以進行項目擴展,且封裝采用DIP40尺寸,因此可以與面包板完美結(jié)合。

以下是通過我們小腳丫FPGA對該電路進行的實驗。我們采用板載的4個撥碼開關(guān)和2個LED(低電平亮)分別作為模塊的4路輸入和2路輸出,并且通過調(diào)節(jié)輸入來觀察輸出結(jié)果。上下兩圖分別所對應(yīng)的輸入分別為:0001和0101,我們也觀察到了在兩種情況下的LED狀態(tài)。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1646文章

22053瀏覽量

618766 -

電路

+關(guān)注

關(guān)注

173文章

6027瀏覽量

175106 -

核心板

+關(guān)注

關(guān)注

5文章

1164瀏覽量

30903

發(fā)布評論請先 登錄

實用電子電路設(shè)計(全6本)——數(shù)字邏輯電路的ASIC設(shè)計

基于FPGA實現(xiàn)FIR數(shù)字濾波器

基于FPGA數(shù)字門電路的實現(xiàn)

基于FPGA數(shù)字門電路的實現(xiàn)

評論