在數字信號處理系統中,有限脈沖響應(finite impulse response,FIR)數字濾波器是一個非常重要的基本單元。近年來,由于FPGA具有高速度、高集成度和高可靠性的特點而得到快速發展。隨著現代數字通信系統對于高精度、高處理速度的需求,越來越多的研究轉向采用FPGA來實現FIR濾波器。而對于FIR濾波器要充分考慮其資源與運行速度的合理優化,各種不同的FIR濾波結構各具優缺點,在了解各種結構優缺點后才能更好地選擇合適結構來實現FIR濾波。

1 FIR數字濾波器

FIR數字濾波器由有限個采樣值組成,設計中在滿足幅值特性時,還能保證精確、嚴格的相位特性,因此在信號處理等領域得到廣泛的應用。

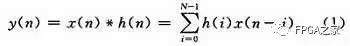

對于FIR濾波器,其輸出y(n)表示為如下形式:

式中:N為濾波器的階數(或抽頭數);x(i)表示第i時刻的輸入樣本;h(i)為FIR濾波器的第i級抽頭系數。

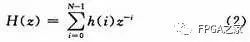

由于FIR濾波器的沖擊響應為一個有限序列,其系統函數可表示為:

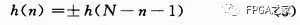

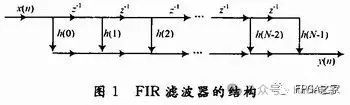

FIR濾波器的基本結構如圖1所示。FIR濾波器只在原點處存在極點,所以這使得FIR濾波器具有全局穩定性。同時FIR濾波器滿足線性相位條件,其沖擊響應序列為實數且滿足奇對稱或偶對稱條件,即:

2 實現方法

運用FPGA來實現FIR數字濾波器的結構多種多樣,但是主要有以下幾類:串行結構、并行結構、轉置型結構、基于FFT算法結構、分布式結構。其他類型的FIR濾波器結構都可以由以上幾種結構衍生而來。

2.1 串行結構

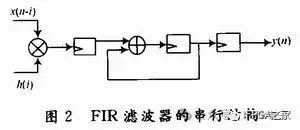

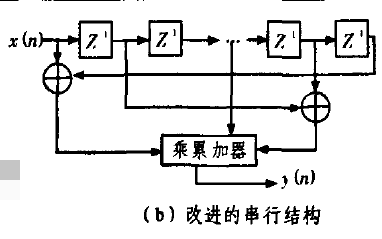

由表達式(1)可知,FIR濾波器實質是做一個乘累加運算,其濾波器的階數決定了一次乘累加的次數,其串行結構如圖2所示。

串行結構的FIR濾波器結構簡單,硬件資源占用少,只需要復用1個乘法器和1個加法器,所以成本較低。但是,這種結構的FIR濾波器要經過多個時鐘周期才有輸出,同時,內部時鐘周期還受到乘法器運算速度的影響,所以該結構的FIR濾波器處理速度慢,只適用于濾波階數較低且處理速度要求低的系統。

2.2 并行結構

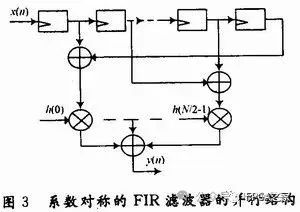

將串行結構的FIR濾波器展開就可以得到并行結構的FIR濾波器,并行FIR濾波器結構又稱作直接型FIR濾波器結構,這種結構是直接根據圖1的濾波器結構,用多個乘法器和加法器并行實現。通常考慮到其濾波器系數的對稱性,先對輸入值進行加法運算,再進行乘法運算,最后累加輸出,以此來減少乘法器的個數,其結構如圖3所示。

并行結構的FIR濾波器在1個周期內可以完成1次濾波,運行速度快,雖然利用濾波系數對稱性,但仍要占用大量的乘法器和加法器,特別對于濾波階數高的濾波器,其資源占用較多,如對于256階的濾波器,其需要128個乘法器來實現。為提高濾波器速度,常引入流水線結構,即在每次加法或者乘法運算后加入1個寄存器存儲數據,使得濾波器可以運行在更高的頻率上。

2.3 轉置型結構

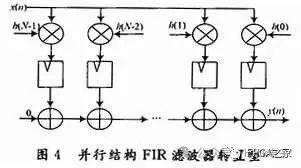

根據轉置定理,如果將網絡中所有的支路方向倒轉,并將輸入x(n)和輸出y(n)相互交換,則其系統函數H(z)不變。通過轉置定理,將并行結構的FIR濾波器變換就可以得到轉置型FIR濾波器,其結構如圖4所示。

基于并行結構的轉置型FIR濾波器實現了數據的并行輸入,在1個周期內就能完成1次濾波,并且各級結構相同,在每個階段都可以讀出數據,可以對濾波階數進行擴展或者縮減,實現任意階數的濾波器。但是由于基于的是并行結構,便有著并行結構的一些缺點,主要是對于高階的濾波器,其資源占用量是巨大的,設計成本高。雖然這樣,轉置型FIR濾波器仍是應用廣泛的一種濾波器。

2.4 基于FFT的結構

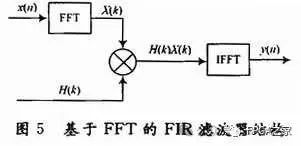

應用快速傅里葉變換(fast fourier transform,FFT)實現FIR濾波器是一種快速實現濾波算法的重要途徑。由式(1)可知,FIR濾波器的輸出y(n)是輸入x(n)與系統沖擊響應序列h(n)的卷積,應用FFT可以快速實現卷積變換。如圖5所示,先將輸入信號x(n)通過FFT變換為它的頻譜采樣值X(k),然后再與FIR濾波器的頻響采樣值H(k)相乘,H(k)可事先存放在存儲器中,最后再將乘積X(k)H(k)通過快速傅里葉反變換(IF-FT)還原為時域序列,即得到輸出y(n)。

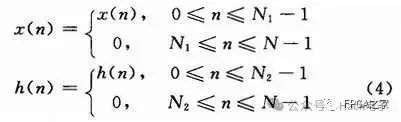

為實現FFT,根據兩有限長序列的線性卷積可用其循環卷積代替而不發生混疊,必須選擇循環卷積長度N≥N1+N2-1,即將x(n)和h(n)補零至長度為N的序列,即:

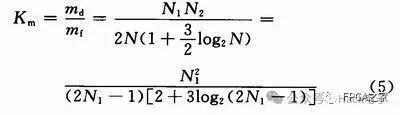

在基于FFT的FIR濾波器結構中,求X(k),H(k)以及反傅里葉變換y(n)需要的乘法次數均為N/2log2N,而計算X(k)H(k)需要N次乘法,所以基于FFT的總乘法次數為mf=3/2Nlog2N+N。由于h(n)滿足式(3)條件,所以直接卷積所需的乘法次數為md=1/2N1N2。假設N1=N2,則比較這兩種乘法計算量有:

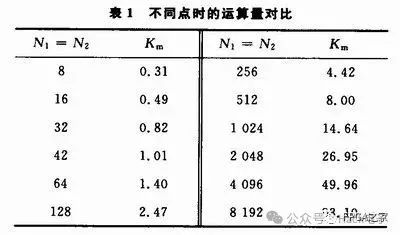

從表1可知,當N1<42時,FFT法的運算量小于直接卷積的運算量,當N1=42時,FFT法的運算量與直接卷積的運算量相當,當N1>42時,FFT法的運算量大于直接卷積的運算量,并且隨著N1增加,FFT法的運算速度越來越快,特別是N1=8 192時,FFT法的運算速度與直接卷積相比快上將近100倍。

2.5 分布式結構

2.5.1 分布式算法原理

分布式算法(distributed arithmetic,DA)于1973年就由Croisier提出,但是直到FPGA出現,才廣泛的被應用于FPGA中計算乘累積和。

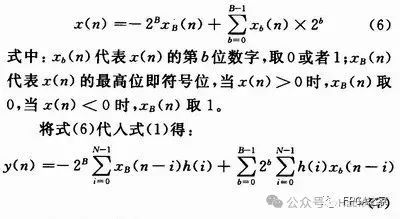

對于有符號數x(n)可以用下式的補碼形式表示:

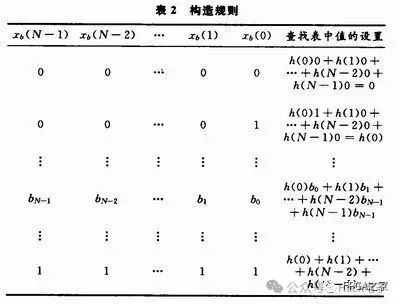

對于式(7)中的h(i)xb(n-i)代表著輸入數據x(n-i)的第i位與抽頭系數h(i)的乘積,對于FIR濾波器,其系數h(i)是常數,所以可以事先構造一個查找表。該查找表存儲所有h(i)xb(n-i)的乘積值,通過輸入(xb(N-1),xb(N-2),…,xb(0))對該表尋址,然后將查得的值乘上2b后移位累加便得到濾波器輸出y(n)。該查找表構造規則如表2所示。

2.5.2 基于分布式算法的FIR濾波器結構

基于分布式算法的FIR濾波器主要有3種結構類型。

(1)第一種結構為串行分布式結構。串行分布式FIR濾波器的原理為,首先用所有N個輸入量的最低位對DA查找表進行尋址查值,得到一個部分積,將部分積右移一位即相當于除以2后放到寄存器中暫存。同時,N個輸入量的次低位開始對DA查找表進行尋址查值,得到另一個部分積,把該部分積與上一個儲存在寄存器中的值進行相加,相加后的值再右移一位放到寄存器中。以此重復循環累加,直到所有位數都尋址完成,注意最高位尋址后的部分積是相減,最后所得到的值就是所需要的結果。

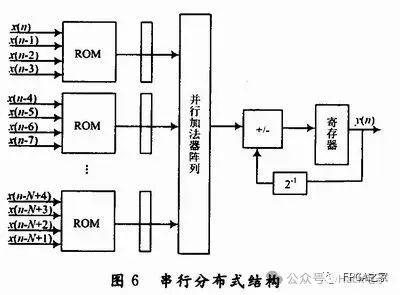

當N過大,即FIR濾波器的濾波階數很高時,采用一個查找表來實現將使得存儲查找表的ROM變得十分龐大。為此可采用部分表結構,即將查找表劃分為多個部分,N個輸入量的同一位對應不同的部分表尋址。圖6所示即為基于4輸入部分表結構的串行DA結構。

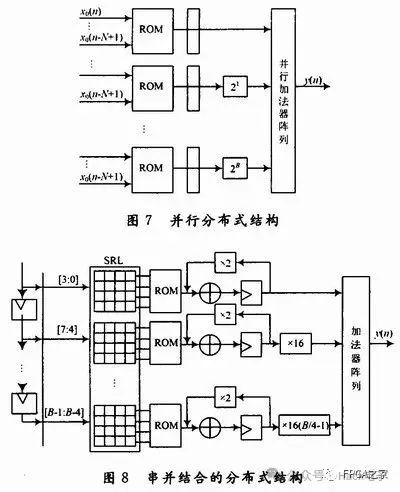

(2)第二種結構為并行分布式結構。并行分布式結構就是將N個輸入量的不同位進行同時查表,而相同位送入同一個ROM尋址,不同位有不同的ROM。其結構如圖7所示。

第三種結構為串并結合分布式結構。它是一種折中方案,既要求速度不太高又要求資源占用少。對于串行分布式算法,是一次一位(one bit-at-a-time,1BAAT)查找表,而并行分布式算法是一次B位(B bits-at-a-time)。所以串并結合分布式算法采用一次多位,如2BAAT,3BA-AT。圖8所示為4BAAT查找表結構圖。

圖8中位數B是4的倍數,SRL為移位寄存器。SRL中第1行從右邊數第1列為數據的0位,第2列為數據的1位,第3列為數據的2位,第4列為數據的3位。類似地,第2行右數第1列為數據的4位,第2列為數據的5位,第3列為數據的6位,第4列為數據的7位。以后各行按相似的數位順序排列。在第一個時鐘周期,數據的0,4,…,B-4位同時進入查找表ROM中,查出所要的數據,第二個時鐘周期,1,5,…,B-3位同時進入ROM中,查出所要的數據,所查得的數據傳遞給下一級累加器進行累加,這樣依次對剩下的各數據位進行同樣的操作。由于每個塊之間相差4位,即16倍,為了對應位相加,所以乘16。FIR濾波器的分布式算法結構比單獨用乘法器實現的速度快,特別是濾波階數越高,其優勢更加明顯。分布式結構中,串行結構是1次查詢1位,所以對B位的數據在不算上移位寄存等的時間,完成1次濾波需要B個時鐘周期;而并行結構只需要1個時鐘周期便完成濾波,所以并行結構是速度最優的結構,但是并行結構需要B個DA查找表,需要大量的ROM來儲存,加大了硬件資源的消耗,特別是階數越高,硬件規模將十分膨大;串并結構綜合兩種結構優勢,實現在速度和規模上的協調。實際應用中。需根據系統的要求來選擇合適的結構。

3 結語

本文定性地分析了各種FIR濾波器的FPGA實現方法。對于低階的FIR濾波器可采用串行結構、并行結構以及轉置型結構來實現,而并行結構和轉置型結構的FIR濾波器以犧牲資源損耗來實現了速度上優勢;對于高階的FIR濾波器,基于乘法器結構的串行結構、并行結構及轉置型結構在速度上難以達到高速處理的要求,而分布式算法將乘法轉換為查表和累加的結構,使得分布式結構的FIR濾波器在速度上得到了提高,

但三種不同形式的分布式結構要在綜合考慮資源以及速度的基礎上進行合理選擇;同樣采用FFT實現的FIR濾波器以減少運算量來獲得了速度上的提高,特別是濾波階數越高其速度提升越明顯。

現代工程技術領域對濾波系統的帶寬、高速、信號的實時性處理等方面要求越來越高,在運用FPGA來實現FIR濾波中,基于乘法器結構的FIR濾波器無法滿足以上要求,而分布式結構的FIR濾波器巧妙地運用ROM查找表來實現固定系數的乘累加運算,避免了乘法運算,并且在隨后的每級加法運算中引入流水線結構,提高了速度。因此采用分布式算法實現FIR濾波器是目前研究的熱點,同時無論哪種分布式算法都要使用ROM來做查找表,但是隨著濾波階數的增加,ROM的數量將會增加,在進一步提高速度的情況下如何減少ROM的數量是今后亟待解決的問題。

1/********************************************************************************* 2*Company: 3*Engineer:空氣微涼 4* 5*CreateDate:000022/03/2013 6*DesignName: 7*ModuleName: 8*ProjectName: 9*TargetDevices: 10*Toolversions: 11*Description: 12*http://www.cnblogs.com/kongqiweiliang/ 13*Dependencies: 14*直接型 15*Revision: 16*Revision:0.01-FileCreated 17*AdditionalComments: 18********************************************************************************/ 19`timescale1ns/1ps 20`defineUD#1 21/*******************************************************************************/ 22moduleFIR 23( 24//systeminterface 25inputiCLK,// 26//Interfacepackage 27input[`DSIZE1-1:0]iDAT,// 28outputreg[`DSIZE2-1:0]oDAT// 29); 30//------------------------------------------------------------------------------- 31`defineDSIZE18 32`defineDSIZE216 33 34reg[`DSIZE1-1:0]TAP0,TAP1,TAP2,TAP3,TAP4,TAP5,TAP6,TAP7,TAP8,TAP9,TAP10; 35reg[`DSIZE1-1:0]T0,T1,T2,T3,T4,T5; 36reg[`DSIZE2-1:0]SUM; 37 38/*0.0036,-0.0127,0.0417,-0.0878,0.1318,0.8500,0.1318,-0.0878,0.0417,-0.0127,0.0036, 390.4608,-1.6256,5.3376,-11.2384,16.8704,108.800,16.8704,-11.238,5.3376,-1.6256,0.4608*/ 40always@(posedgeiCLK)begin 41TAP0<=?iDAT; 42??TAP1??<=?TAP0; 43??TAP2??<=?TAP1; 44??TAP3??<=?TAP2; 45??TAP4??<=?TAP3; 46??TAP5??<=?TAP4; 47??TAP6??<=?TAP5; 48??TAP7??<=?TAP6; 49??TAP8??<=?TAP7; 50??TAP9??<=?TAP8; 51??TAP10?<=?TAP9; 52?? 53??T0????<=?TAP0?+?TAP10;??//h(0) 54??T1????<=?TAP1?+?TAP9;???//h(1) 55??T2????<=?TAP2?+?TAP8;???//h(2) 56??T3????<=?TAP3?+?TAP7;???//h(3) 57??T4????<=?TAP4?+?TAP6;???//h(4) 58??T5????<=?TAP5?;?????//h(5) 59??//T0??128-4*4-4+0.5+0.25+0.0625=108.8125??=?128?*?0.8500?????h(0) 60??//T1??16+0.5+0.25+0.125=16.875?????=?128?*?0.1318?????h(1) 61??//T2??8+4-1+0.25=11.25???????=?128?*?-0.0878????h(2) 62??//T3??4+1+0.25+0.0625+0.03125=5.34375???=?128?*?0.0417?????h(3) 63??//T4??1+0.5+0.125=1.625???????=?128?*?-0.0127??????h(4) 64??//T5??0.5-0.03125=0.46875???????=?128?*?0.0036?????h(5) 65??SUM???<=?(T0<<7)-(T0<<4)-(T0<<2)+{{1{T0[`DSIZE1-1]}},T0[`DSIZE1-1:1]}+{{2{T0[`DSIZE1-2]}},T0[`DSIZE1-1:2]}+{{4{T0[`DSIZE1-1]}},T0[`DSIZE1-1:4]}?+ 66???????(T1<<4)+{{1{T1[`DSIZE1-1]}},T1[`DSIZE1-1:1]}?+??{{2{T1[`DSIZE1-1]}},T1[`DSIZE1-1:2]}+{{3{T1[`DSIZE1-1]}},T1[`DSIZE1-1:3]}?- 67???????(T2<<3)+(T2<<2)?-?T2?+?{{2{T2[`DSIZE1-1]}},T2[`DSIZE1-1:2]}?+ 68???????(T3<<2)+T3+{{2{T3[`DSIZE1-1]}},T3[`DSIZE1-1:2]}+{{4{T3[`DSIZE1-1]}},T3[`DSIZE1-1:4]}+{{5{T3[`DSIZE1-1]}},T3[`DSIZE1-1:5]}?- 69???????T4+{{1{T4[`DSIZE1-1]}},T4[`DSIZE1-1:1]}+{{3{T4[`DSIZE1-1]}},T4[`DSIZE1-1:3]}?+ 70???????????{{1{T5[`DSIZE1-1]}},T5[`DSIZE1-1:1]}-{{5{T5[`DSIZE1-1]}},T5[`DSIZE1-1:5]}; 71????? 72??oDAT??<=?{{7{SUM[15]}},SUM[15:7]}; 73?end????? 74????????? 75?//------------------------------------------------------------------------------- 76?endmodule?

-

FPGA

+關注

關注

1646文章

22069瀏覽量

619676 -

數字濾波器

+關注

關注

4文章

274瀏覽量

47662 -

FIR

+關注

關注

4文章

151瀏覽量

34330 -

數字信號

+關注

關注

2文章

998瀏覽量

48416

原文標題:有限脈沖響應-FIR

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

使用FPGA構建的數字濾波器設計方案

基于DSP的FIR 數字濾波器設計

基于FPGA的FIR數字濾波器該怎么設計?

基于LabVIEW的FIR數字濾波器設計

基于FPGA的FIR數字濾波器的優化設計

FPGA是如何設計并實現了32階FIR數字濾波器的硬件電路?

基于FPGA實現FIR數字濾波器

基于FPGA實現FIR數字濾波器

評論