在上周舉辦的IEDM 2020上,IMEC展示了一種新穎的動態(tài)隨機存取存儲器(DRAM)單元架構(gòu),該架構(gòu)實現(xiàn)了兩種銦鎵鋅氧化物薄膜晶體管(IGZO-TFT),并且沒有存儲電容器。

對于不同的單元尺寸,這種2T0C(2晶體管0電容器)配置的DRAM單元顯示的保留時間超過400s–顯著降低了存儲器的刷新率和功耗。

在BEOL中處理IGZO-TFT的能力減少了CELL的占地面積,并為堆疊單個CELL提供了可能性。這些突破性成果為低功耗和高密度單片3D-DRAM存儲器鋪平了道路。

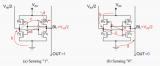

(a)2T0C DRAM單元的示意圖,其中存儲元件是讀取晶體管的氧化物電容Cox;(b)2T0C DRAM陣列在單個平面上的示意性俯視圖示例。

A-A‘截面方向表示,可以通過(c)堆疊2T0C單元的幾層來增加陣列密度。將傳統(tǒng)的1T1C(一個晶體管一個電容器)的DRAM擴展到超過32Gb的裸片密度面臨著兩個主要挑戰(zhàn)。

首先,基于Si的陣列晶體管縮放的困難使得在減小單元尺寸的同時保持所需的關(guān)斷電流和world line resistance 具有挑戰(zhàn)性。

其次,3D集成和可擴展性(通向高密度DRAM的終極途徑)受到對存儲電容器需求的限制。Imec提出了一種新穎的DRAM體系結(jié)構(gòu),可以應(yīng)對這兩個挑戰(zhàn),從而提供了一條通往低功耗高密度3D-DRAM存儲器的擴展路徑。

新架構(gòu)實現(xiàn)了兩個IGZO-TFT,它們以極低的關(guān)斷電流而聞名,并且沒有存儲電容器。在這種2T0C配置中,讀取晶體管的寄生電容用作存儲元件。

由于3x10 -19 A / ?m的極低(抽出)關(guān)斷電流,所得DRAM單元的保留時間》 400s。這些突破的結(jié)果是在300mm晶圓上加工的優(yōu)化規(guī)模IGZO晶體管(柵極長度為45nm)上獲得的。

優(yōu)化旨在抑制氧和氫缺陷對電流和閾值電壓的影響-這是開發(fā)IGZO-TFT的主要挑戰(zhàn)之一。

imec計劃總監(jiān)Gouri Sankar Kar表示,除了保留時間長之外,基于IGZO-TFT的DRAM單元還具有超越當(dāng)前DRAM技術(shù)的第二個主要優(yōu)勢。

與Si不同,IGZO-TFT晶體管可以在相對較低的溫度下制造,因此,與BEOL處理兼容,這使我們能夠?qū)RAM存儲器單元的外圍移動到存儲器陣列下方,從而顯著減少了存儲器裸片的占位面積;

此外,BEOL處理還開辟了通往堆疊單個DRAM單元的途徑,從而使3D DRAM體系結(jié)構(gòu)成為可能。

IMEC的突破性解決方案將有助于拆除所謂的內(nèi)存墻,使DRAM內(nèi)存在要求苛刻的應(yīng)用(例如云計算和人工智能)中繼續(xù)發(fā)揮關(guān)鍵作用。

責(zé)編AJX

-

電容

+關(guān)注

關(guān)注

100文章

6240瀏覽量

153520 -

DRAM

+關(guān)注

關(guān)注

40文章

2343瀏覽量

185282 -

存儲器

+關(guān)注

關(guān)注

38文章

7640瀏覽量

166638

發(fā)布評論請先 登錄

電容知識大全

電容知識大全(精彩講義)

DRAM基本單元最為通俗易懂的圖文解說

Imec牽頭啟動汽車芯粒計劃

帶電容式觸摸板的無線遙控器,使用MSP430F51x2

【「算力芯片 | 高性能 CPU/GPU/NPU 微架構(gòu)分析」閱讀體驗】--全書概覽

DRAM存儲器的特性有哪些

如何開發(fā)不帶Flash API 的Bootloader實現(xiàn)在線升級

DRAM存儲器的基本單元

什么是存儲器的刷新

SSD基本架構(gòu)

imec實現(xiàn)硅基量子點創(chuàng)紀(jì)錄低電荷噪聲

DRAM芯片的基本結(jié)構(gòu)

不帶防爆等級的電容使用后會出現(xiàn)什么問題

IMEC展示不帶電容的DRAM單元架構(gòu)

IMEC展示不帶電容的DRAM單元架構(gòu)

評論