Del Jones ADI公司

在JESD204C入門系列的第1部分中,通過描述它解決的一些問題,對JESD204標準的新版本進行了說明。通過描述新的術語和特性來總結B和C版本標準之間的差異,然后逐層概述這些差異。因為第1部分已經奠定了理解基礎,現在我們來進一步研究一下JESD204C標準幾個更值得注意的新特性。

64b/66b和64b/80b鏈路層

對于64b/66b鏈路層,66位數據塊由兩個同步頭位,后接八個八位位組的樣本數據組成,其中部分是基于IEEE 802.3第49條定義的數據塊格式。與IEEE標準不同的是,它沒有編碼——有效載荷數據只是轉換器樣本數據,由傳輸層打包到數據幀中。由于沒有編碼來確保發生一定數量的數據轉換來提供dc平衡,因此必須對樣本數據進行加擾。這些加擾的八位位組的幀數據被直接放入鏈路層,兩個同步頭位附加在其中。

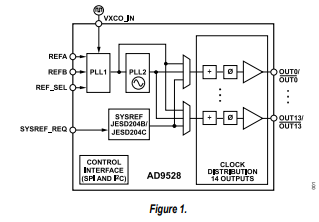

64b/66b數據塊的格式如圖1所示。該示例展示了這樣的情況:一個數據通道由幀組成,每個幀包含來自一個轉換器的一個樣本。塊映射規則與來自JESD204B標準的幀映射規則非常相似。按順序完成八位位組到64位數據塊的映射,其中D0表示幀的第一個八位位組。例如,如果F = 8,D0表示JESD204C幀的第一個八位位組,D7表示JESD204C幀的最后一個八位位組。該幀的第一個八位位組的MSB是Converter0的Sample0的MSB(與JESD204B一樣)。例如,如果F = 2,D0和D1代表第一個幀,D2和D3代表第二個幀,以此類推。

為了與JESD204B中使用的方法保持一致,多塊中的八位位組按MSB到LSB的順序被轉移到加擾器/解擾器中。

在E = 1的情況中,每個多塊都從幀邊界開始。如果E > 1,擴展多塊將從(必須從)幀邊界開始。有關更多信息,請參考多塊(MB)和擴展多塊(EMB)章節。

圖1.64b/66b數據塊格式示例,LMFS = 1.1.2.1,N = N’ = 16。

同步頭是一個2位未加擾值,位于每個數據塊的開始位置,其內容經過解析之后,用于解碼單個同步轉換位。這些位要么采用0-1序列,表示邏輯1,要么采用1-0序列,表示邏輯0。

64b/80b數據塊的格式如圖2所示。除了樣本數據的八個八位位組和兩個同步頭之外,還具有兩個填充位,位于每個八位位組之間。填充位的值由17位PRBS序列決定,以減少雜散,并確保適當數量的數據轉換以保持dc平衡。未加擾的填充位在樣本數據加擾之后插入到塊中。

圖2.64b/80b數據塊格式示例,LMFS = 1.1.2.1,N = N’ = 16。

提供64b/80b選項是為了與8b/10b保持相同的時鐘比,幫助簡化鎖相環(PLL)設計,同時最小化雜散。對于希望通過使用前向糾錯或利用同步字提供的其他功能的應用,相比8b/10b,更應該選擇64b/80b,稍后將就這一問題進行詳細討論。

多塊(MB)和擴展多塊(EMB)

JESD204C多塊中包含32個塊。每個多塊中的32個同步轉換位構成一個32位同步字。稍后,我們將就此進行詳細討論。擴展多塊是一個E多塊容器,必須包含整數數量的幀。當多幀不包含整數數量的幀時,要求E > 1。多塊和擴展多塊的格式如圖3所示。

多塊可以是2112 (32×66)位,或者是2560 (32×80)位,具體由所用的64位編碼方案決定。對于大多數場景,擴展多塊只是一個多塊。JESD204C中引入了E參數,確定了擴展多塊中的多塊數量。E的默認值為1。如上所述,當幀F中的八位位組的數量不是2的倍數時,該配置要求E > 1。E的公式為:E = LCM(F, 256)/256。發送12位樣本且N’=12時,一般選擇這些配置,以最大化鏈路中的帶寬效率。這一要求確保EMB邊界與幀邊界一致。

圖4和圖5所示為E > 1的JESD204C配置示例。所示的JESD204C配置適用于以下情況:LMFS = 2.8.6.1,N’ = 12,E = 3。圖4顯示了傳輸層的映射情況。在這個配置中,每個通道有4個12位樣本,相當于6個八位位組。由于多塊的每個塊都需要8個八位位組,因此該塊中填充了來自后續幀的2個八位位組(1.33個樣本)。

圖3.JESD204C多塊和擴展多塊的格式。

|

LMFS = 2.8.6.1 N = 12 N’ = 12 |

LMFS = 2.8.6.1 N = 12 N’ = 12 |

|

2 Lanes (L = 2) |

2個通道 (L = 2) |

|

8 Converters (M = 8) |

8個轉換器 (M = 8) |

|

1 Sample per Converter per Frame (S = 1) |

每轉換器每幀一個樣本(S = 1) |

|

12-Bit Nibble Group (N’ = 12) |

12位 半字節組 (N’ = 12) |

|

6 Octets per Lane (F = 6) |

每通道6個 八位位組(F = 6) |

|

ADC7 D11…D0 |

ADC7 D11…D0 |

| Nib. Grp 3 | 半字節組3 |

| Cnv7Smpl0 | Cnv7Smpl0 |

| Lane1, Octet 5 | 通道1,八位位組5 |

|

1 Frame of Data Has 6 Octets, so 2 More Octets Needed from Subsequent Frame to Fill the Block |

1個數據幀有6個八位位組, 所以需要從后續幀獲取2個八位位組,以填充塊 |

| Scramble | 加擾 |

| Serialize/SH Insert | 序列化/SH插入 |

| Transport Layer | 傳輸層 |

| 64b/66b Link Layer | 64b/66b鏈路層 |

圖4.傳輸層映射,LMFS = 2.8.6.1,N’ = 12,E = 3。

圖5顯示了如何使用來自傳輸層的數據幀來形成塊和多塊。如圖所示,可以看到幀邊界與每三個塊的塊邊界對齊。由于多塊由32個塊組成,所以要在第三個多塊之后才能和多塊對齊。因此,E = 3。

LEMC是擴展多塊計數器,大致相當于8b/10b鏈路層中的LMFC。SYSREF對系統中的所有LEMC進行對齊,并使用LEMC邊界來確定同步和通道對齊。

|

Scramble Serialize/SH Insert |

加擾 序列化/SH插入 |

|

Block 0 SH Octet0 |

塊0 SH 八位位組0 |

| Lane1, Block0 Contain Sample 0 from Converters 7:4, Sample 1 from Converter 4, and Bits 11:8 of Converter 5 Sample 1. These 64 Bits Are Scrambled to Form a Scrambled Block of Data. | 通道1、塊0包含來自轉換器7:4的樣本0、來自轉換器4的樣本1,以及來自轉換器5樣本1的位11:8。這些64位都已加擾,以形成加擾數據塊。 |

| Lane0, Block0 Contain Sample 0 from Converters 3:0, Sample 1 from Converter 0, and Bits 11:8 of Converter 1 Sample 1. These 64 Bits Are Scrambled to Form a Scrambled Block of Data. | 通道0、塊0包含來自轉換器3:0的樣本0、來自轉換器0的樣本1,以及來自轉換器1樣本1的位11:8。這些64位都已加擾,以形成加擾數據塊。 |

| Frame 0 | 幀0 |

| Block 2 | 塊2 |

| Frame Boundaries Align with Block Boundaries on Every Third Block. | 幀邊界與每三個塊的塊邊界對齊。 |

| Frame 3 | 幀3 |

| MB | MB |

| EMB = 3 | EMB = 3 |

| Frame Boundaries Near a Multiblock Boundary Occur at 33 and 63 – Blocks, not Aligned. | 多塊邊界附近的幀邊界出現在塊33和63邊界處,沒有對齊。 |

| SERDOUT1± | SERDOUT1± |

| Multiblock and Frame Alignment Occurs at the End of 96th Block (Block 95) and 128th Frame (Frame 127). So, E = 3. | 多塊和幀對齊出現在第96個塊(塊95)和第128個幀(幀127)的末端位置。因此,E = 3。 |

| SERDOUT0± | SERDOUT0± |

| Frame 127 | 幀127 |

圖5.串行輸出多塊/幀對齊,LMFS = 2.8.6.1,N’ = 12,E = 3。

同步字

32位同步字由多塊中32個塊的每個同步頭位組成,其中第一個傳輸的是位0。同步字用于提供通道同步,并使能確定性延遲。此外,它還可以選擇性地提供CRC錯誤校驗、前向糾錯,或者提供一個命令通道,供發射器與接收器通信。

32位同步字有三種不同的格式選項。在每種情況下,都需要多塊序列的結束,因為它用于獲得多塊同步和通道對齊。

64b/66b鏈路操作

當使用64b/66b鏈路層時,鏈路的建立過程從同步頭對齊開始,然后是擴展多塊同步,最后是擴展多塊對齊。

同步頭對齊

同步頭中的同步轉換位確保在每個塊邊界(66位)都有一個數據轉換。JESD204C接收器中的狀態機檢測到一個數據轉換,在66位后再查找另一個轉換。如果狀態機檢測到64個連續以66位間隔進行的位轉換,則會實現同步頭鎖定(SH_lock)。如果沒有檢測到64個連續轉換,則重新啟動狀態機。

圖6.JESD204C擴展多塊(通道)對齊。

擴展多塊同步

一旦實現同步頭對齊,接收器就會在轉換位中查找擴展多塊結束(EoEMB)序列(100001)。同步字的結構確保此序列只能在適當的時間發生。一旦確定EoEMB,狀態機將檢查每32個同步字,以確保存在多塊結束導頻信號(00001)。如果E = 1,EoEMB位也會存在導頻信號。如果E > 1,那么每個E × 32轉換位,導頻信號都將包含EoEMB位。一旦檢測到四個連續的有效序列,就可以實現擴展多塊結束鎖定(EMB_LOCK)。繼續監測每個E × 32轉換位,如果沒有檢測到有效的序列并重置對齊過程,則EMB_LOCK丟失。

擴展多塊(通道)對齊

使用64b/66b鏈路層時的通道對齊與使用8b/10b鏈路層時的通道對齊非常相似,每個通道上的JESD204C接收器都使用一個彈性緩沖區來存儲傳入的數據。這被稱為擴展多塊對齊,緩沖區開始在EoEMB邊界(而不是在使用8b/10b鏈路層時ILAS期間的/K/至/R/邊界)存儲數據。圖6說明了如何實現通道對齊。每個通道的接收緩沖區在接收到EoEMB的最后一位之后開始緩沖數據(最后一個接收通道除外)。接收到最后一個接收通道的EoEMB之后,會觸發釋放所有通道的接收緩沖區,所以現在所有通道都是對齊的。

錯誤監測和前向糾錯

JESD204C同步字選項讓用戶能夠監測或糾正JESD204數據傳輸中可能發生的錯誤。糾錯會導致額外的系統延遲。對于大多數應用,使用CRC-12同步字進行錯誤監測是可行的,因為它提供了大于1 × 10-15的誤碼率(BER)。

JESD204C發射器中的CRC-12編碼器接收每個多塊的加擾數據位,并計算12個奇偶校驗位。這些奇偶校驗位在隨后的多塊中傳輸到接收器。接收器同樣將從接收到的每個數據多塊中計算12個奇偶校驗位,并與同步字中接收到的位進行對比。如果所有奇偶校驗位都不匹配,則接收到的數據中至少存在一個錯誤,可以觸發錯誤標志。

對于對額外延遲不敏感但對錯誤敏感的應用(例如測試和測量設備),使用FEC可以得到優于10 × 10-24的誤碼率。JESD204C發射器中FEC電路計算多塊中已加擾數據位的FEC奇偶校驗位,并在下一個多塊的同步頭位流上對這些奇偶校驗位編碼。接收器計算接收位的校驗子,本地生成的奇偶校驗位和接收到的奇偶校驗位之間的差異就在于此。如果校驗子為0,則假定接收到的數據位正確。如果校驗子非0,則可以用它來確定最可能的錯誤。

FEC奇偶校驗位的計算方法與CRC相似。FEC編碼器接收多塊的2048位加擾數據位,并添加26位奇偶校驗位,以構建一個縮短的二進制循環碼。該碼的發生器多項式為:

對于每個多塊,這個多項式可以糾正最多9位突發錯誤。

總結

為了滿足未來幾年數據密集型應用更快處理數據的需求,JESD204C將多千兆位接口定義為數據轉換器和邏輯器件之間必需的通信通道。高達32 GSPS的通道速率和64b/66b編碼使超高帶寬應用能以最小的開銷來提高系統效率。這些和其他標準改進對于5G通信、雷達和電子戰應用都大有裨益。再加上糾錯功能,先進的儀器儀表和其他應用都能夠無錯運行多年。

有關JESD204及其在ADI公司產品中的實現的更多信息,請訪問ADIJESD204串行接口頁面。有關ADI高速轉換器的更多信息,請訪問我們的RF轉換器頁面和28 nm RF 數據轉換器頁面。有關ADI收發器產品的更多信息,請訪問我們的RadioVerse頁面。

作者簡介

Del Jones是位于美國北卡羅來納州格林斯博羅的高速轉換器團隊的應用工程師。他自2000年以來一直為ADI工作,負責支持ADC、DAC和串行接口。加入ADI之前,他曾在電信行業擔任電路板和FPGA設計工程師。Del畢業于德克薩斯大學達拉斯分校,獲電氣工程學士學位。

審核編輯 黃昊宇

-

數據轉換器

+關注

關注

1文章

373瀏覽量

28586

發布評論請先 登錄

LTC6953具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz時鐘分配器技術手冊

AD9528提供14路LVDS/HSTL輸出的JESD204B/JESD204C時鐘發生器技術手冊

使用jesd204b IP核時,無法完成綜合,找不到jesd204_0.v

松下MPS媒體制作平臺 第十一篇:深入探索自動跟蹤插件(第二部分)

松下MPS媒體制作平臺第七篇:視頻混合器插件(第二部分)

JESD204B使用說明

TSW14J58 JESD204C數據采集和圖形發生器卡

TSW14J59EVM JESD204C數據采集和圖形發生器卡

Air780EP硬件設計原理解析(第二部分)

0.4mm層疊封裝(PoP)封裝的PCB組裝指南,第二部分

從JESD204B升級到JESD204C時的系統設計注意事項

TI AFE8092 AFE8030 JESD204C配置及調試手冊 Part B

TI AFE8092/AFE8030 JESD204C配置及調試手冊 Part C

ADC12QJ1600-SP具有JESD204C接口的四通道1.6GSPS 12位模數轉換器(ADC)數據

JESD204C入門第二部分:新特性及其內容

JESD204C入門第二部分:新特性及其內容

評論