各位大佬,我想請教一個問題:

為了驗(yàn)證H750主時鐘頻率和功耗的關(guān)系:

用STM32CUBEMX配置STM32H750VBT6的主時鐘為:100MHz,程序可以正常運(yùn)行,然后將主時鐘改

發(fā)表于 03-12 06:38

ADS7864數(shù)據(jù)手冊上說當(dāng)采用8M外部時鐘的時候,采樣頻率為500kHz,但是有人說可以通過HOLDX頻率來控制采樣頻率,一個HOLDX下降沿采樣一次,HOLDX

發(fā)表于 01-14 06:47

電子發(fā)燒友網(wǎng)站提供《AN-616:AD9430評估板對XTAL振蕩器時鐘的修改.pdf》資料免費(fèi)下載

發(fā)表于 01-13 14:31

?0次下載

接第四十五期的SCG介紹,下文對SCG時鐘工作頻率范圍、寄存器設(shè)置等進(jìn)行詳細(xì)闡述。

![的頭像]() 發(fā)表于

發(fā)表于 12-09 14:55

?854次閱讀

請問如果要修改ADS1299的采樣頻率,應(yīng)該同個哪個寄存器進(jìn)行修改呢?麻煩答復(fù)一下,謝謝

這里好像是輸出速率,不是采樣頻率,那么采樣頻率應(yīng)

發(fā)表于 11-26 07:33

spi周期的波形

主要問題應(yīng)該不是spi不行,因?yàn)橛幸话攵丝谑钦]敵龅模?b class='flag-5'>時鐘頻率不算高,說明書能到50MHz。修改時鐘到12.5MHz就所有端口都正常。

發(fā)表于 11-19 06:01

電子發(fā)燒友網(wǎng)站提供《使用中繼器的I2C總線的最大時鐘頻率.pdf》資料免費(fèi)下載

發(fā)表于 10-08 09:48

?0次下載

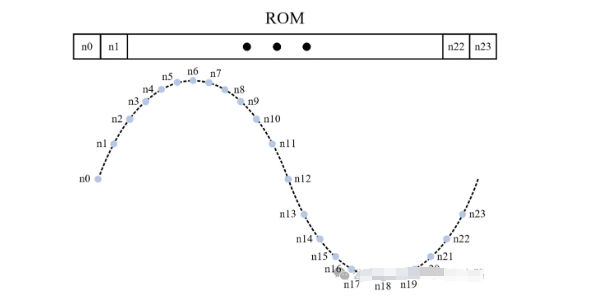

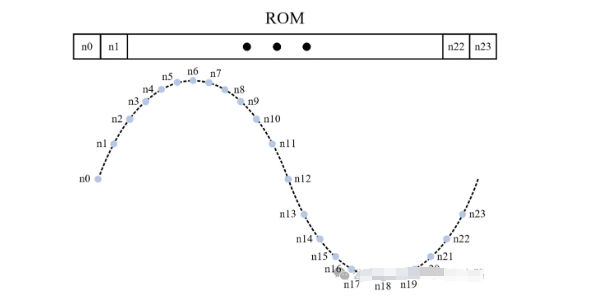

DDS(Direct Digital Synthesizer,直接數(shù)字頻率合成器)技術(shù)是一種頻率合成方法,其輸出頻率與時鐘之間存在密切的關(guān)系。 一、DDS基本原理 DDS技術(shù)通過編程

![的頭像]() 發(fā)表于

發(fā)表于 10-06 15:27

?2307次閱讀

內(nèi)存時鐘是內(nèi)存模塊中一個至關(guān)重要的參數(shù),它直接關(guān)聯(lián)到內(nèi)存模塊能夠工作的最高頻率。以下是對內(nèi)存時鐘的詳細(xì)解析,包括其定義、作用、與內(nèi)存頻率的關(guān)系、對計(jì)算機(jī)性能的影響以及選擇時的考慮因素,

![的頭像]() 發(fā)表于

發(fā)表于 09-04 11:45

?2201次閱讀

DDR4(第四代雙倍數(shù)據(jù)率同步動態(tài)隨機(jī)存取存儲器)的時鐘頻率和速率之間存在著緊密的關(guān)系,這種關(guān)系對于理解DDR4內(nèi)存的性能特性至關(guān)重要。以下將詳細(xì)探討DDR4時鐘頻率和速率之間的關(guān)系,

![的頭像]() 發(fā)表于

發(fā)表于 09-04 11:44

?5572次閱讀

電子發(fā)燒友網(wǎng)站提供《CDCDLP223高性能時鐘頻率合成器數(shù)據(jù)表.pdf》資料免費(fèi)下載

發(fā)表于 08-22 10:35

?0次下載

電子發(fā)燒友網(wǎng)站提供《CDC7005高性能時鐘頻率合成器和抖動消除器數(shù)據(jù)表.pdf》資料免費(fèi)下載

發(fā)表于 08-21 11:14

?0次下載

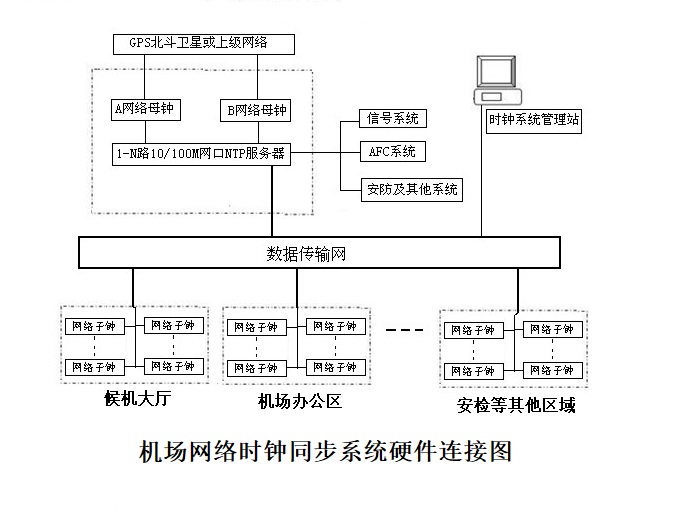

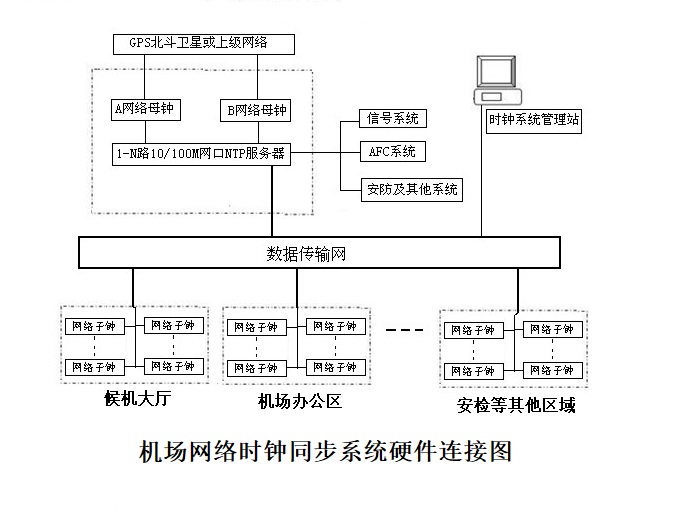

時間頻率設(shè)備(時鐘同步)賦能機(jī)場系統(tǒng)-安徽京準(zhǔn)

![的頭像]() 發(fā)表于

發(fā)表于 08-06 14:29

?616次閱讀

ESP8266EX文件表明最大PWM頻率為1Khz。我需要 20Khz 到 100Khz。PWM時鐘預(yù)分頻器可以修改嗎?

我對Delta_Sigma硬件有同樣的問題。

發(fā)表于 07-19 10:53

上次我們聊到了晶振的占空比,即信號在高電平持續(xù)時間與整個周期時間的比例。今天,我們來聊聊晶振頻率信號中的脈沖、時鐘周期和機(jī)械周期之間的關(guān)系。

![的頭像]() 發(fā)表于

發(fā)表于 07-17 14:38

?2468次閱讀

如何修改時鐘頻率

如何修改時鐘頻率

評論