DDS(Direct Digital Synthesizer,直接數字頻率合成器)技術是一種頻率合成方法,其輸出頻率與時鐘之間存在密切的關系。

一、DDS基本原理

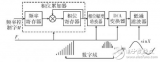

DDS技術通過編程頻率控制字來分頻系統時鐘,以產生所需的頻率。DDS系統的核心部件包括相位累加器、波形存儲器(ROM查詢表)、數模轉換器(DAC)和低通濾波器。其工作原理可以概括為:在每個時鐘周期,相位累加器根據頻率控制字累加相位值,累加的結果作為地址去查詢波形存儲器中的波形數據,然后將波形數據通過DAC轉換為模擬信號,最后通過低通濾波器得到平滑的波形輸出。

二、DDS輸出頻率與時鐘的關系

DDS輸出頻率與時鐘的關系可以通過以下公式來表達:

**F_{out} = frac{K times f_{clk}}{2^N} ] 其中: - (F_{out}) 是DDS的輸出頻率。 - (K) 是頻率控制字,它是一個整數或小數,用于控制DDS的輸出頻率。 - (f_{clk}) 是參考時鐘頻率,即DDS系統使用的時鐘源頻率。 - (N) 是相位累加器的位數,它決定了DDS的頻率分辨率和相位累加器的精度。

直接數字式頻率合成器 (Direct Digital

Synthesizer, DDS )是一種新型的頻率合成技術,具有相對帶寬大、頻率轉換時間短、穩定性好、分辨率高、可靈活產生多種信號等優點,被廣泛應用于現代電子系統及設備的頻率源設計中。

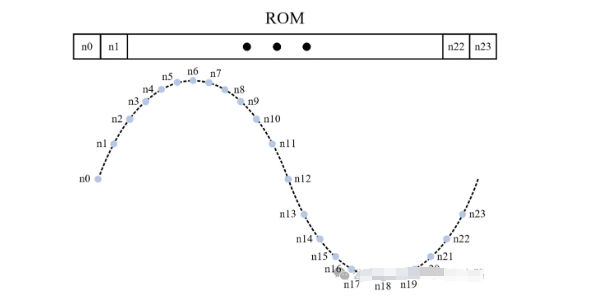

假設存儲空間里有一組數據:n0~n23,這組數據是對一個周期正弦波形采樣的結果。現在計算機想輸出其中一些數據點,有幾種輸出方法呢?

輸出數據索引從n0開始依次累加M

1、M = 1:即n0、n1、n2、…、n22、n23、n0、n1、…

2、M = 3:即n0、n3、n6、…、n18、n21、n0、n3、…

假設系統時鐘頻率為Fclk,那么,在一秒鐘的時間內索引會一直累加至M×Fclk,但是,存儲空間內只有一個周期的數據,只有24個數據點,因此,每當索引值累加至23時便會溢出,繼續從0開始累加,意味著一個周期輸出完成,開始輸出下一周期。

三、影響DDS輸出頻率與時鐘關系的因素

- 參考時鐘頻率((f_ {clk})) : - 參考時鐘頻率是DDS系統的基礎,它決定了DDS能夠產生的最高頻率。理論上,DDS可以產生的最高頻率是參考時鐘頻率的一半(即奈奎斯特頻率),但由于實際電路中的限制(如DAC的帶寬、低通濾波器的截止頻率等),實際可實現的最高頻率通常會低于這個值。 - 參考時鐘頻率的穩定性也直接影響到DDS輸出頻率的穩定性。因此,在選擇參考時鐘源時,需要選擇具有高穩定性的晶振或其他時鐘源。

- 頻率控制字((K)) : - 頻率控制字是控制DDS輸出頻率的關鍵參數。通過改變頻率控制字,可以實現對DDS輸出頻率的精確調整。 - 頻率控制字的取值范圍受限于相位累加器的位數。當相位累加器的位數確定后,頻率控制字的取值范圍也就確定了。

- 相位累加器位數((N)) : - 相位累加器的位數決定了DDS的頻率分辨率。位數越多,DDS的頻率分辨率越高,即能夠產生的最小頻率間隔越小。但同時,也會增加系統的復雜性和功耗。 - 相位累加器的位數還決定了DDS能夠產生的最高頻率。在參考時鐘頻率確定的情況下,相位累加器的位數越多,DDS能夠產生的最高頻率也越高(盡管實際可實現的最高頻率受到其他因素的限制)。

四、DDS輸出頻率與時鐘關系的實際應用

在實際應用中,需要根據具體需求來選擇合適的參考時鐘頻率、頻率控制字和相位累加器位數。例如,在需要產生高精度、高分辨率的頻率信號時,可以選擇較高的參考時鐘頻率和較多的相位累加器位數;而在對頻率分辨率要求不高但需要快速頻率切換的應用場景中,則可以選擇較低的參考時鐘頻率和較少的相位累加器位數以簡化系統設計和降低成本。 此外,還需要注意DDS輸出頻率與時鐘之間的相位關系。

由于DDS是基于數字信號處理技術實現的頻率合成器,因此其輸出信號的相位是可控的。通過調整相位控制字或相位累加器的初值等參數,可以實現對DDS輸出信號相位的精確控制。這一特性使得DDS在需要精確控制信號相位的應用場景中(如雷達、通信等領域)具有廣泛的應用前景。

-

頻率合成器

+關注

關注

5文章

295瀏覽量

32774 -

時鐘

+關注

關注

11文章

1892瀏覽量

133028 -

DDS

+關注

關注

22文章

672瀏覽量

154239 -

輸出頻率

+關注

關注

0文章

10瀏覽量

8374

發布評論請先 登錄

關于DDS輸出信號頻率的分辨問題

請問在DDS系統中通過DDS內部倍頻得到芯片參考時鐘內部倍頻是否對輸出信號有影響?

AD5933和AD5934的時鐘頻率差異的相關問題?

如何確定DDS輸出信號頻譜中的雜散源

AD9850 DDS 頻率合成器的原理及應用

DDS陣列頻率源技術研究

DDS有關名詞解釋

直接數字頻率合成器(DDS)簡介及其輸出頻譜中主相位截斷雜散的頻率和幅度

基于DDS的短波射頻頻率源設計方案解析

dds輸出頻率與時鐘的關系

dds輸出頻率與時鐘的關系

評論