在Aries PCIe? Smart Retimer取得成功的基礎之上,Astera Labs以CXL? 2.0解決方案進一步突破數據中心連接的帶寬、容量和性能瓶頸。宣布與Intel加強合作,為數據中心承載運算及延遲敏感的工作負載提供保障

中國,北京 - 2021年3月11日- 智能系統連接解決方案的先驅Astera Labs今日宣布拓展其關注領域,目的是解決以數據為中心(data-centric)的應用系統的性能瓶頸。全新的Aries Compute Express Link?(CXL? 2.0)Smart Retimer(PT5161LX、PT5081LX)產品系列是面向低時延的CXL.io連接方案,是其布局新領域的首款解決方案,目前正積極與戰略性客戶進行樣品驗證。

Astera Labs首席執行官Jitendra Mohan表示:“隨著我們拓展至CXL生態系統,Astera Labs實現了再次躍進,通過提供專用解決方案來實現復雜的異構運算與可重組的分解式系統拓撲。基于在PCI Express?(PCIe?) 4.0和5.0互連領域的領先地位,Astera Labs的Aries CXL Smart Retimer產品提供了實現全新的工作負載優化平臺的無縫通道。”

急速增加的數據以及人工智能和機器學習等特定工作負載的主流化,都要求專用加速器與通用CPU在相同的主板或機架內協同工作,同時共享內存空間。CXL 2.0互連對實現此類緩存一致性的系統拓撲至關重要。

Astera Labs創始投資人Avigdor Willenz表示:“如同我們先前投資的Annapurna Labs與Habana Labs一樣,Astera Labs正以專用解決方案的先驅姿態邁步前行。我相信Astera Labs最新的CXL與PCIe連接解決方案,對于在云端實現人工智能的全部潛力至關重要。”

CXL聯盟總裁Barry McAuliffe表示:“做為CXL聯盟的早期成員,Astera Labs積極貢獻其在連接方面的專業知識,推動CXL標準的發展。很高興看到其首款CXL芯片產品上市,支持快速成長的CXL生態系統。”

與Intel成功且持續擴大的合作,使得數據中心承載運算及延遲敏感的工作負載成為可能

Astera Labs同時宣布在Aries Smart Retimer產品系列提供全新的低延遲模式(Low Latency Mode),可與Intel Xeon Scalable處理器進行PCIe連接。此項進展是與Intel公司密切合作的成果,可進一步將PCIe鏈路時延降低至10ns以下,并提升以數據為中心的工作負載性能。Astera Labs是首家與Intel Xeon Scalable處理器(代號Sapphire Rapids)在PCIe 5.0接口上實現強壯互連的廠商。

此外,Astera Labs發布其Equinox產品,它是適用于PCIe/CXL應用的新型即插即用Smart Retimer Add-in-Card。與Intel公司合作開發的Equinox卡和相關專用固件可簡化采用Intel最新Xeon Scalable處理器開發PCIe 5.0系統。這展現了Astera Labs的一種轉變,即通過其提供易用的即插即用板卡,迅速實現復雜的系統拓撲。

Intel公司企業副總裁兼數據中心工程與架構部門總經理Zane Ball表示:“PCIe Gen5和CXL是目前乃至未來在異構運算工作負載和數據中心架構的基礎技術。我們正與Astera Labs等生態系統領導者合作,為即將發布的Intel Xeon Scalable平臺(代號Sapphire Rapids)及其他平臺大幅降低PCIe和CXL的互連延遲。”

供貨情況:

·適用于PCIe 5.0(PT5161LR、PT5081LR)和CXL(PT5161LX、PT5081LX)的Aries Smart Retimer可與戰略性客戶進行樣品驗證。

·適用于PCIe 4.0并支持低延遲模式的Aries Smart Retimer現已量產。

·適用于PCIe 5.0(EQUINOX)的Aries Smart Retimer Add-in-Card已開放訂購。

-

處理器

+關注

關注

68文章

19825瀏覽量

233746 -

intel

+關注

關注

19文章

3493瀏覽量

188061 -

數據中心

+關注

關注

16文章

5166瀏覽量

73245 -

PCIe

+關注

關注

16文章

1328瀏覽量

84751 -

人工智能

+關注

關注

1804文章

48788瀏覽量

246951

發布評論請先 登錄

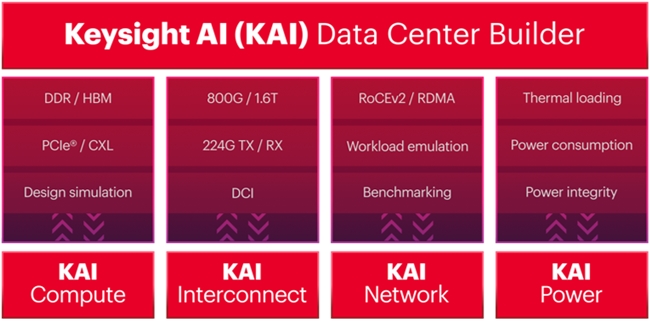

是德科技推出用于大規模AI數據中心的系列解決方案

康普發布面向數據中心的Propel XFrame解決方案

適用于數據中心和AI時代的800G網絡

優化800G數據中心:高速線纜、有源光纜和光纖跳線解決方案

源網荷儲一體化解決方案:如何為大型數據中心節省用電成本?

高速線纜在數據中心的應用和解決方案

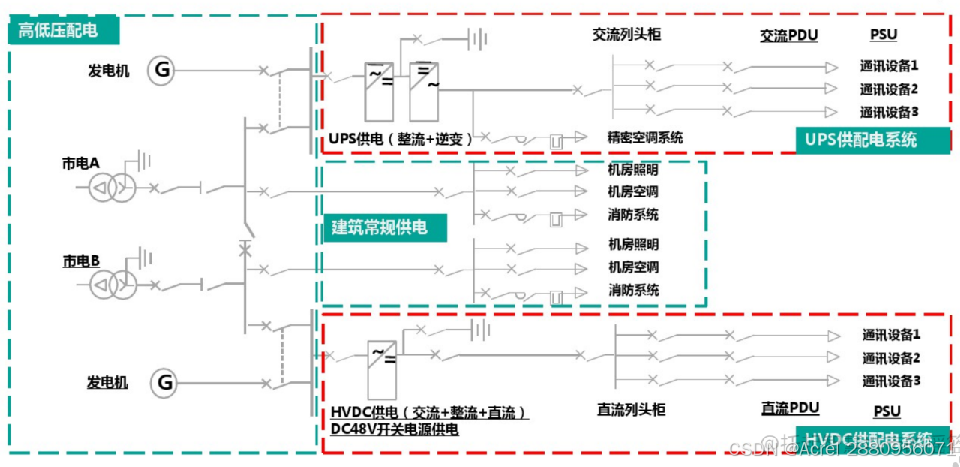

數據中心列頭柜精密配電監控解決方案

安科瑞AMB數據中心智能小母線監控解決方案

Molex莫仕發布革新熱管理解決方案,賦能高性能數據中心應對未來挑戰

Molex連接器助力構建未來數據中心 充分發揮人工智能AI的力量

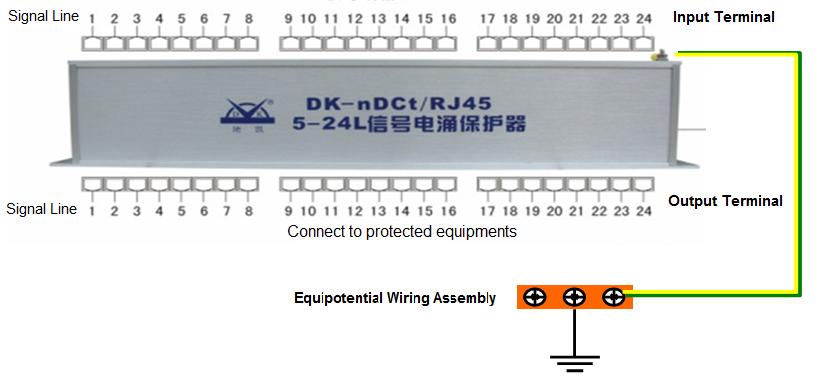

數據中心機房防雷和接地系統的解決方案

Astera Labs拓展新領域 以專用解決方案解決數據中心連接瓶頸

Astera Labs拓展新領域 以專用解決方案解決數據中心連接瓶頸

評論