導(dǎo)言:這篇為PCIe要提及的時鐘類型作個小鋪墊,可以大致作一個了解,想深入了解可以參考更加細(xì)致的文獻(xiàn)。

三種基本的I/O架構(gòu)

1? 通用時鐘(Common Clock)

2? 前向時鐘(Forward Clock)

3? 嵌入時鐘(Embedded Clock)

?這些I/O架構(gòu)用于需要不同級別I/O帶寬的各種應(yīng)用

?處理器可能具有這些I/O類型中的一種或全部

?通常,相同的電路可用于仿真不同的I/O方案以重復(fù)使用設(shè)計

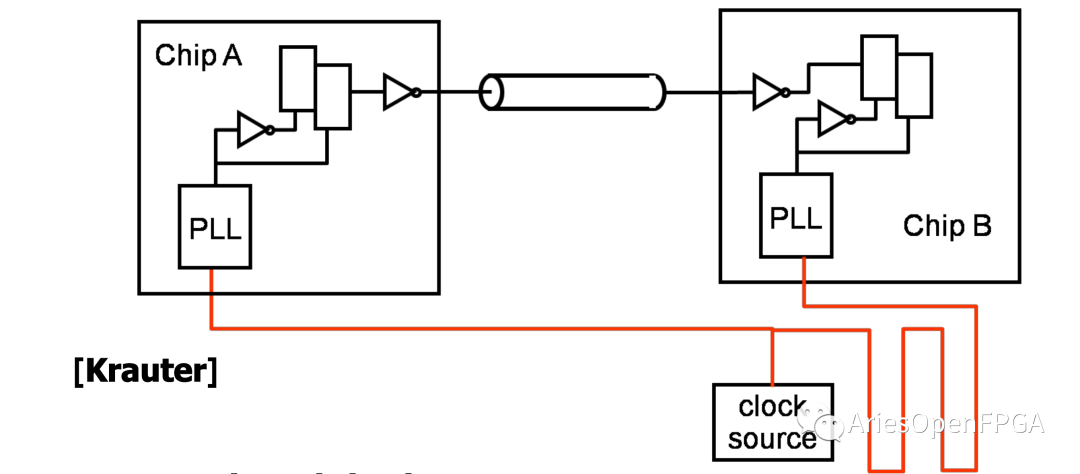

通用時鐘的I/O架構(gòu)

?在原始計算機(jī)系統(tǒng)中常見

?同步系統(tǒng)(Synchronous system)

?通用總線時鐘控制芯片到芯片的傳輸

?需要等長的走線路徑,以最大程度地減少時鐘偏斜

?數(shù)據(jù)速率通常限制在0?100Mb(數(shù)據(jù)可能比較老)

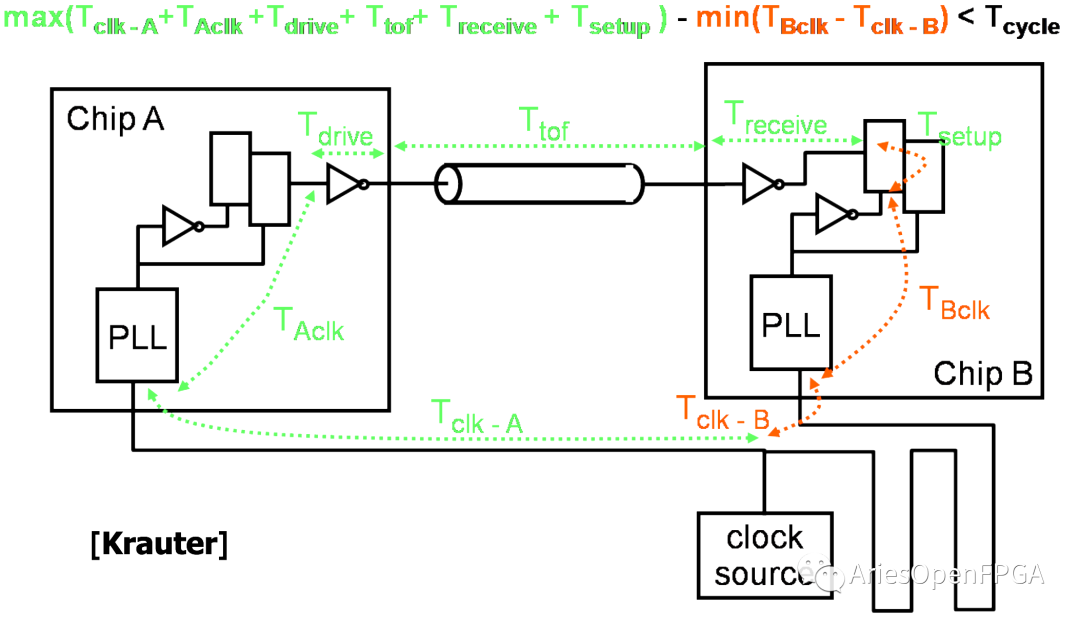

通用時鐘I/O循環(huán)時間

通用時鐘I/O限制

?難以控制時鐘偏斜和傳播延遲

?需要嚴(yán)格控制絕對延遲以滿足給定的周期時間

?對芯片上電路和電路板布線路徑中的延遲變化很敏感

?由于片上延遲和片外延遲之間的相關(guān)性低,難以補(bǔ)償延遲變化

?雖然通常用于片上通信,但應(yīng)用的速度受限

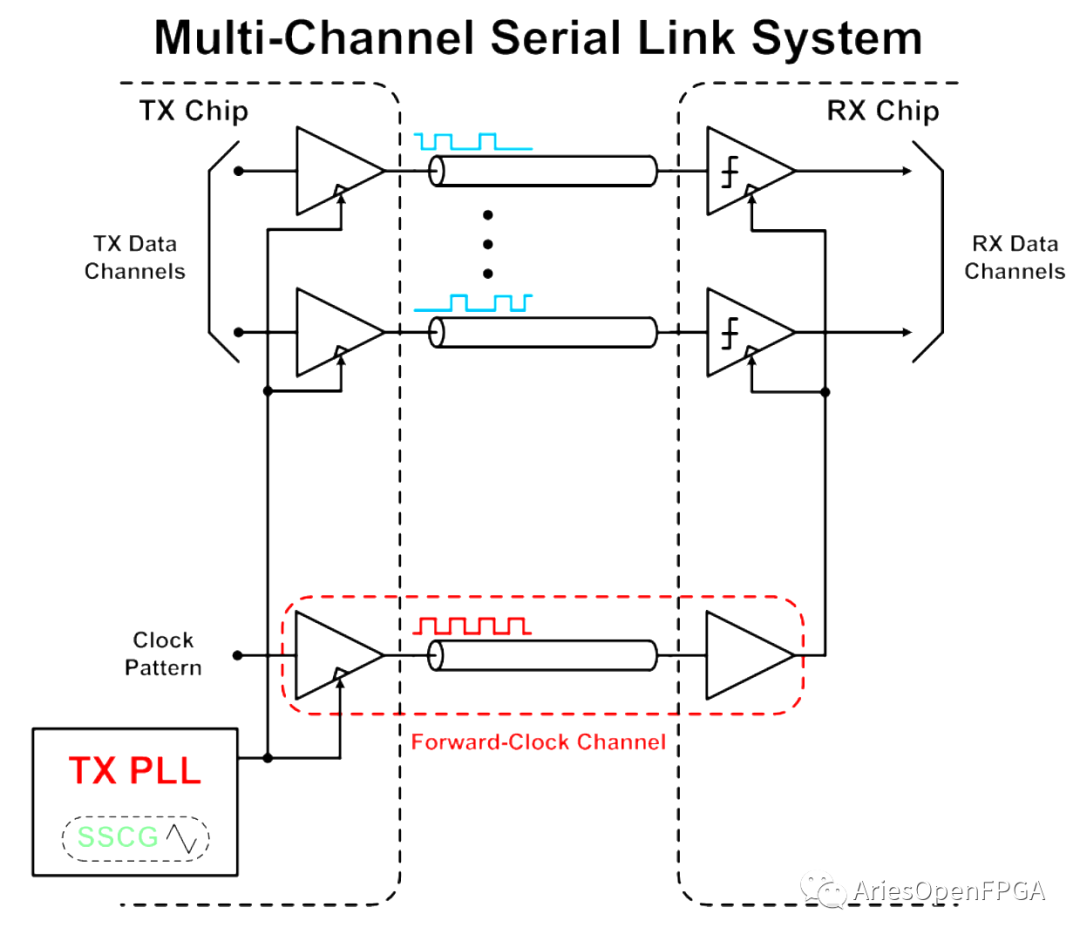

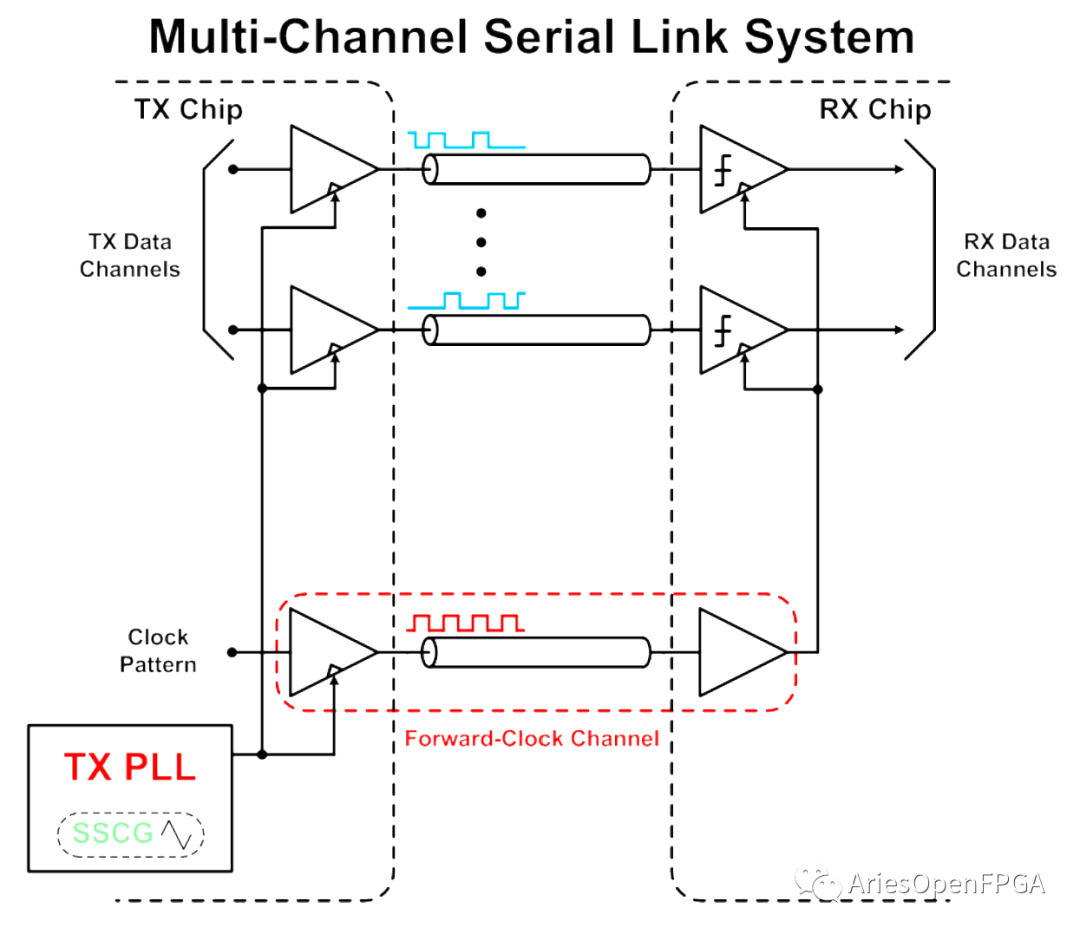

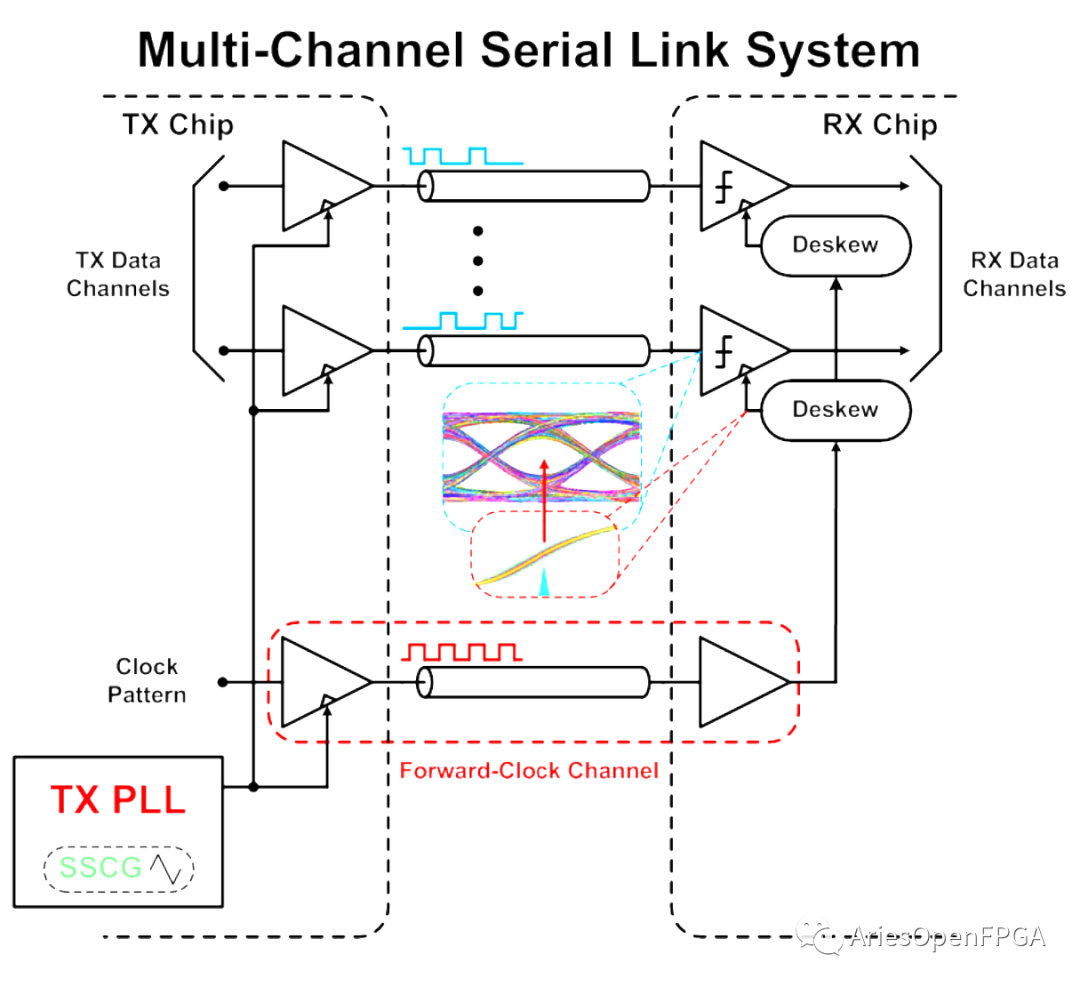

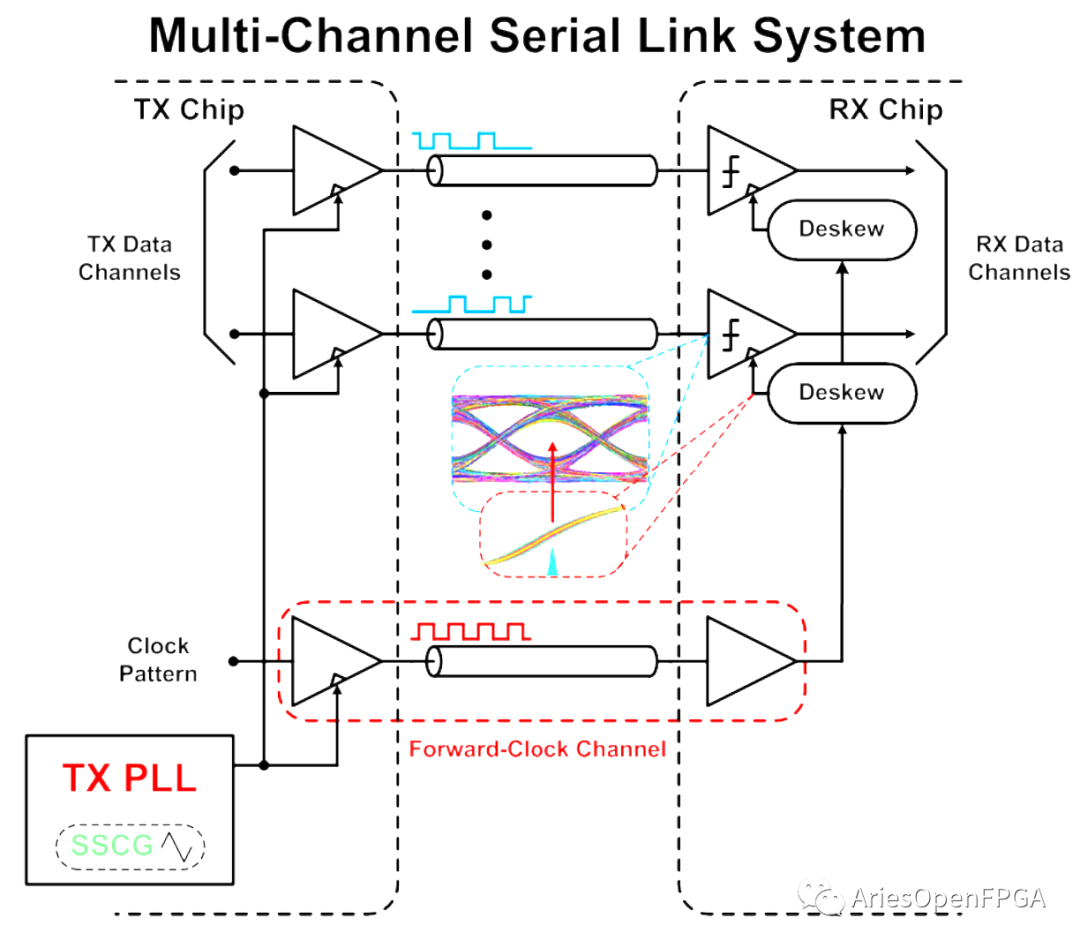

前向時鐘I/O架構(gòu)

?通常作為高速傳輸中,TX芯片到RX芯片的前向參考時鐘

?同步系統(tǒng)(Mesochronous system)

?用于處理器內(nèi)存接口和多處理器通信

?Hypertransport(HT總線)

?需要一個額外的時鐘通道

?“相干”時鐘可實現(xiàn)從低頻到高頻的抖動跟蹤

?需要好的時鐘接收放大器,因為前向時鐘會被通道衰減

前向時鐘I/O限制

?時鐘偏斜會限制前向時鐘I/O性能

?驅(qū)動能力和負(fù)荷失配

?互連長度不匹配

?低通通道導(dǎo)致抖動放大

?前向時鐘的占空比變化

前向時鐘I/O偏斜校正

?每通道偏移校正可顯著提高數(shù)據(jù)速率

?采樣時鐘調(diào)整為輸入數(shù)據(jù)眼的中心時鐘

?實施

?延遲鎖定環(huán)路和相位內(nèi)插器

?注入鎖定振蕩器

?相位采集可以是

?基于BER的附加輸入相位采樣器

?基于相位檢測器,并帶有額外的輸入相位采樣器,定期打開電源

前向時鐘I/O電路

?TX PLL

?TX時鐘分配

?復(fù)制TX時鐘驅(qū)動器

?通道

?前向時鐘放大器

?RX時鐘分配

?去偏斜電路

?DLL/PI

?注入鎖定振蕩器

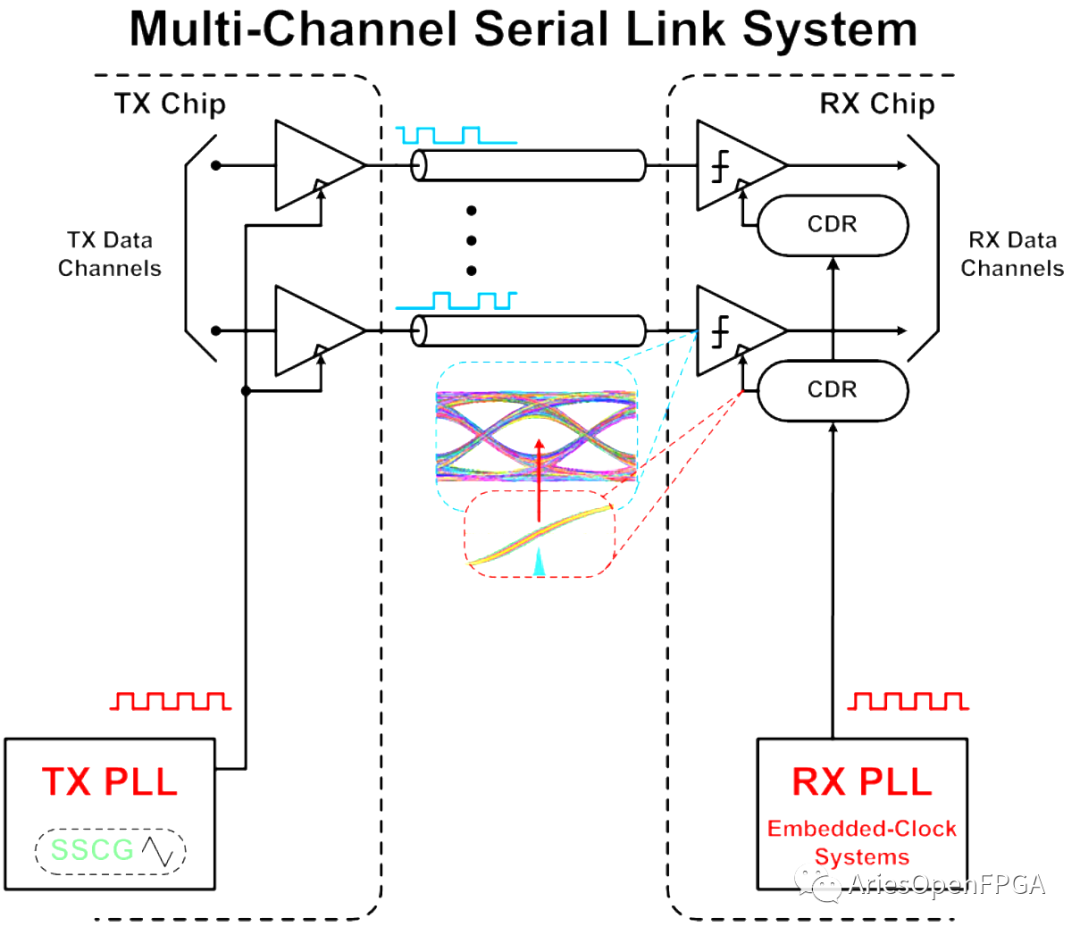

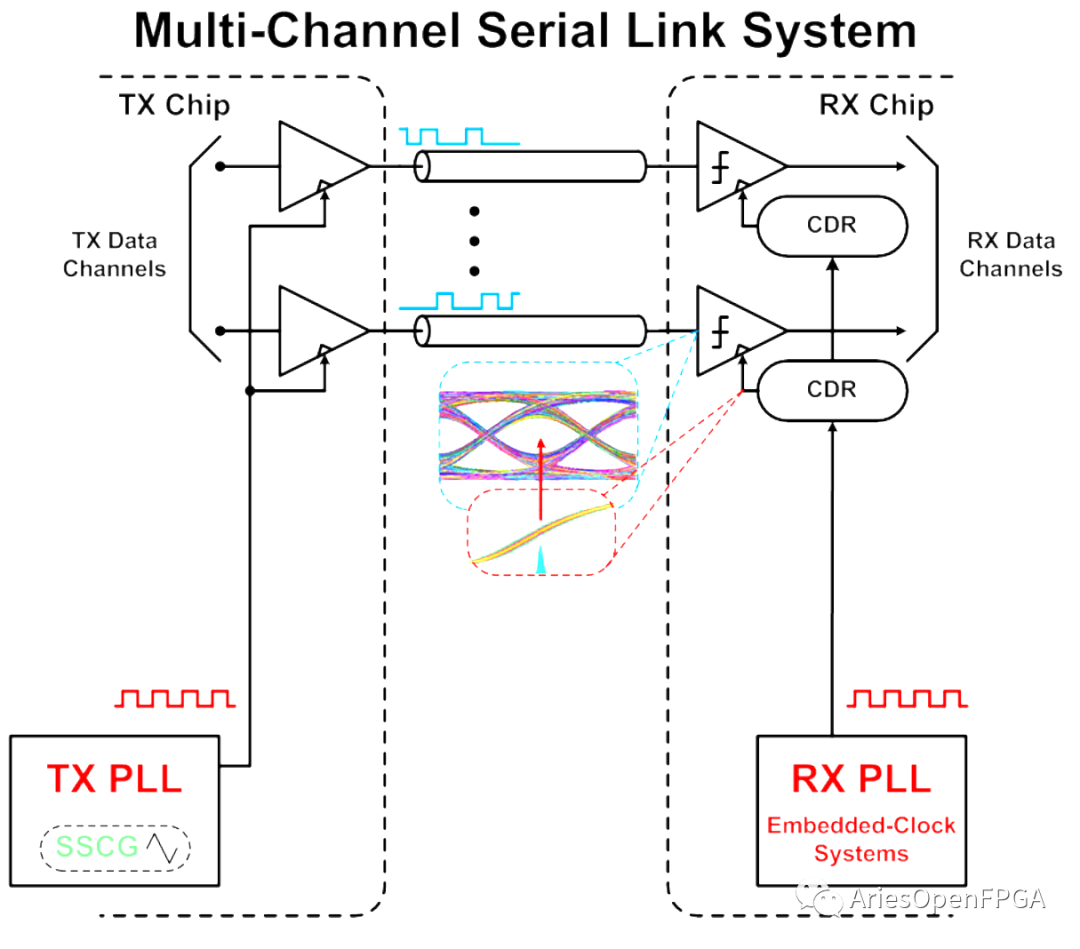

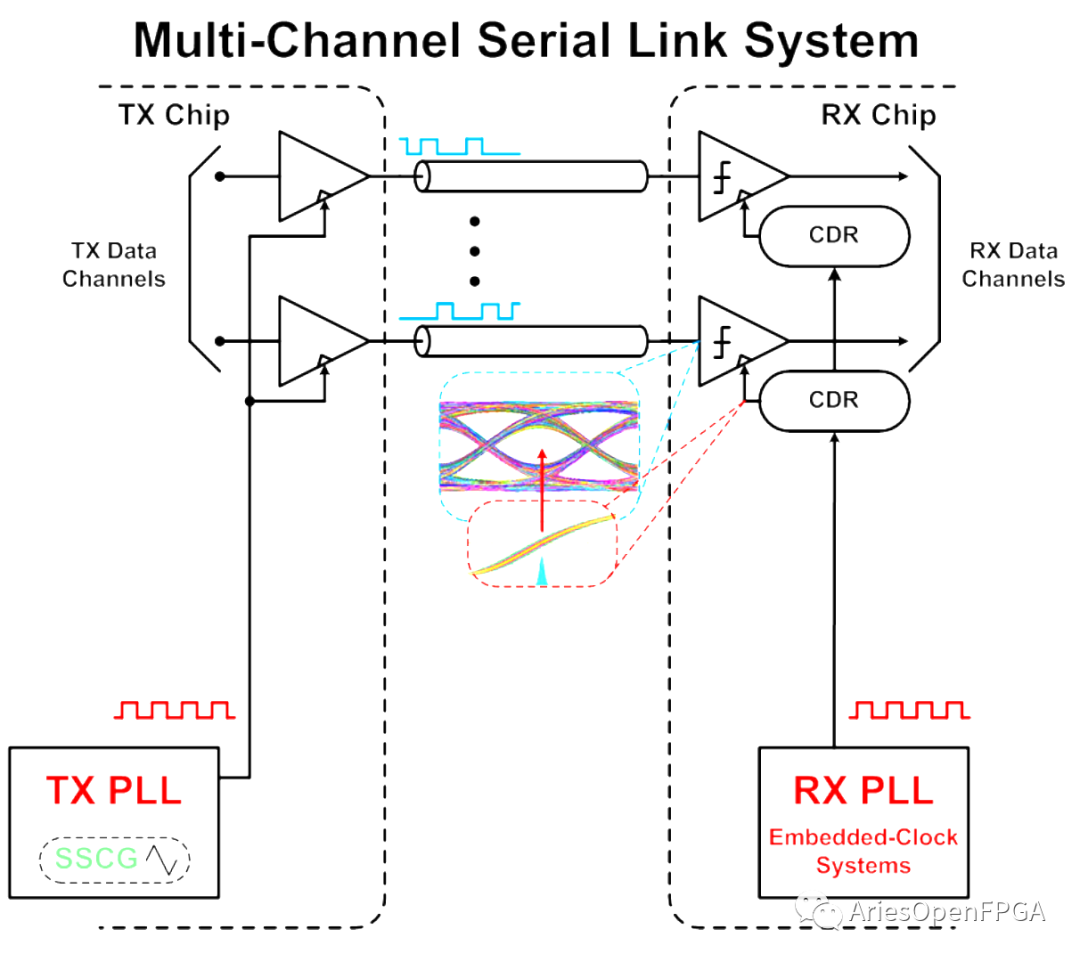

嵌入式時鐘I/O架構(gòu)

?可用于同步或準(zhǔn)同步系統(tǒng)(mesochronousor plesiochronous systems)

?從輸入數(shù)據(jù)流中提取時鐘頻率和最佳相位

?持續(xù)運(yùn)行的相位檢測

?CDR實施(應(yīng)用)(CDR:clock and data recovery)

?基于每個通道的PLL

?雙環(huán)帶全局PLL或

?本地DLL/PI

?本地相位旋轉(zhuǎn)器PLL

嵌入式時鐘I/O限制

?抖動跟蹤受CDR帶寬限制(clock and data recovery)

?技術(shù)擴(kuò)展允許具有更高帶寬的CDR,從而可以實現(xiàn)更高的頻率抖動跟蹤

?一般而言,實現(xiàn)前向時鐘需要更多的硬件(注:原文是,Generally more hardwarethan forward clockimplementations,我聯(lián)系上下文自己翻譯的,這里貼出來作為參考)

?額外的輸入相位采樣器

嵌入式時鐘I/O電路

?TX PLL

?TX時鐘分配

?CRD

?基于每個通道的PLL

?雙環(huán)帶全局PLL和

?本地DLL / PI

?本地相位旋轉(zhuǎn)器PLL

?全局PLL需要將RX時鐘分配給各個通道

原文標(biāo)題:?I/O時鐘架構(gòu)

文章出處:【微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

時鐘

+關(guān)注

關(guān)注

11文章

1893瀏覽量

133068 -

PCIe

+關(guān)注

關(guān)注

16文章

1334瀏覽量

84961

原文標(biāo)題:?I/O時鐘架構(gòu)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

介紹三種常見的MySQL高可用方案

nvme IP開發(fā)之PCIe下

CMOS,Bipolar,F(xiàn)ET這三種工藝的優(yōu)缺點是什么?

I/O接口與I/O端口的區(qū)別

示波器的三種觸發(fā)模式

什么是PID調(diào)節(jié)器的三種模式

I2S有左對齊,右對齊跟標(biāo)準(zhǔn)的I2S三種格式,那么這三種格式各有什么優(yōu)點呢?

mosfet的三種工作狀態(tài)及工作條件是什么

單片機(jī)的三種總線結(jié)構(gòu)

區(qū)域架構(gòu)和 MCU I/O 擴(kuò)展

PCIe 5.0 SerDes 測試

MCUXpresso IDE下在線聯(lián)合調(diào)試雙核MCU工程的三種方法

PCIe中三種基本的I/O架構(gòu)

PCIe中三種基本的I/O架構(gòu)

評論