有人希望能談談在做FPGA設計的時候,如何理解和使用過約束。我就以個人的經驗談談:

什么是過約束;

為什么會使用過約束;

過約束的優點和缺點是什么;

如何使用過約束使自己的設計更為健壯。

什么是過約束(overconstraint)

所謂過約束,就是給目標時鐘一個超過其設定運行頻率的約束。比如實際運行的時鐘頻率是100MHz,我們在給這個時鐘添加約束的時候,要求它能運行在120MHz。

為什么會使用過約束

通常在兩種情況下,我們可能會使用過約束。

第一種情況,FPGA的時序報告不準確,為了確保邏輯的實際運行頻率能滿足要求,做過約束來保留設計余量。

FPGA的時序報告是基于FPGA的時序模型計算出來的,時序模型來源于實驗室的測試和對生產過程的嚴格控制,是要充分考慮PVT(Process,Voltage,Temperature)的影響計算出來的。對比較成熟的FPGA廠家來說,研發,生產,測試都有標準流程控制,這一部分的數據還是比較可靠的。如果是新的廠家,大家可能要做好時序模型不準確的心理準備。在工藝不變的情況下,信號的傳輸,翻轉速率隨電壓,溫度的變化而變化。一般來說,溫度越低,電壓越高,信號的傳輸,翻轉越快,反之越慢。而FPGA的設計軟件在做STA的時候,往往是根據最差的工作條件下的(Worst Case)給出的。所以我們會看到這樣的現象,時序報告顯示的時序是不滿足設計要求的,但邏輯運行到FPGA上功能又是正常的。這是因為FPGA的實際運行條件要比Worst Case好,實際的時序也優于報告的結果。如果是這種情況,可以不考慮使用過約束。

第二種情況,對某些關鍵的時鐘域,時序不太容易滿足,施加一個更高的時鐘約束,以期望軟件能跑出一個滿意的結果。如果是這種情況,需要注意的是EDA軟件在做布局布線的時候,會根據邏輯功能和時鐘頻率分配布局布線資源。過約束加的不合理,會造成非關鍵路徑占用有限的布局布線資源,反而會使布局布線的結果更差。所以在做過約束的時候,要根據你的設計合理設置,不能簡單的把所有時鐘都做過約束。

過約束的優點和缺點:

過約束的優點顯而易見,會讓的設計運行的余量更大。缺點除了我們上面討論的,如果在你的設計里面有跨時鐘域的信號傳遞,而你沒有對跨時鐘域的路徑做約束,軟件在分析跨時鐘域的delay的時候,由于變成過約束后,源時鐘和目的時鐘的頻率相關性變化了,這部分的delay約束就變成了無限小,布局布線更困難了。這是我們在做過約束設計的時候要特別注意的。

過約束還有一個問題是,比如你的設計頻率是100MHz,添加的約束是120MHz。那么在做STA的時候,軟件還是按照120MHz來分析。即使你的布局布線的時序結果是119MHz,已經滿足設計要求,但在時序報告上,還會顯示時序不滿足。這給我們的時序分析帶來一些麻煩。

如何使用過約束使自己的設計更為健壯

在使用過約束的時候,一般情況下,以增加20%-30%為宜,太大的余量并沒有太大的意義。如果該時鐘有跨時鐘域的操作,一定要通過專門的約束(Multicycle或max delay)在明確定義這部分的延時要求。

在Lattice的設計軟件中,為了配合過約束的使用,增加的一個PAR_ADJ屬性:

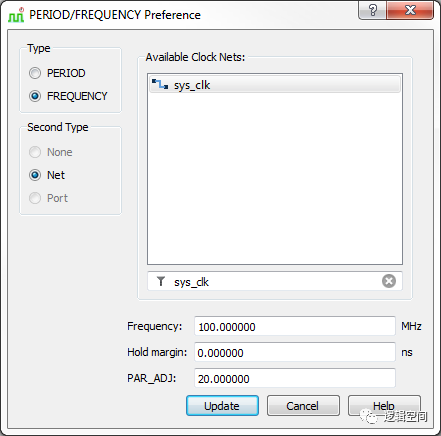

FREQUENCY NET“sys_clk” 100.000000 MHz PAR_ADJ 20.000000 ;

這樣的約束會告訴軟件,用100+20=120MHz做布局布線的時候,而用100MHz的約束來做STA,這樣就不會發生我們前面遇到的困擾了。

GUI的界面是這樣的:

原文標題:FPGA的過約束

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614906

原文標題:FPGA的過約束

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PCB Layout 約束管理,助力優化設計

FPGA時序約束之設置時鐘組

基于FPGA的電子琴設計

PGA411 OVEXC過壓保護點(Differential overvoltagethreshold)是如何理解的,保護點是多少V?

時序約束一主時鐘與生成時鐘

如何理解和使用做FPGA設計時的過約束?

如何理解和使用做FPGA設計時的過約束?

評論