摘要: 在早期獲取部分可重構EAPR(Early Access Partial Reconfiguration)方法的基礎上,研究實現局部動態自重構系統的方法和流程。設計的系統有兩個可重構區域,每個區域有兩個重構模塊,利用Virtex-4上集成的PowerPC硬核微處理器控制內部配置訪問端口ICAP(Internal Configuration Access Port)完成自重構。通過在Xilinx ML403開發板上進行驗證,實現了系統的自重構功能。系統對部分資源的分時復用提高了系統的資源利用率,高的配置速率縮短了系統的配置時間。

Implementation of partial dynamic self-reconfiguration based on EAPR

Wang Lie,Xu Xiaojie,Chen Jian

School of Computer and Electronics Information,Guangxi University,Nanning 530004,China

Abstract: The design method and flow of the partial dynamic self-reconfiguration system were studied and implemented based on the reconfiguration design of EAPR.The system included two reconfigurable regions, each with two reconfigurable modules. The PowerPC hard core microprocessor that was integrated in the Virtex-4 was used to control the ICAP to complete self-reconfigurable. Through ML403 board of Xilinx, the function of self-reconfiguration was verified. The time devision multiplexing of part of the resource improves the resouce utilization, and the high configuration speed shortens the configuration time.

Key words : FPGA;EAPR;self-reconfiguration;microprocessor

局部動態自重構系統是一種新型的可重構計算系統。實現自重構系統的可編程器件必須具有局部動態可重構能力。局部動態可重構是指系統在運行過程中可以對部分資源進行重新配置,而其余資源仍保持正常運行,分時復用可重構硬件上的資源實現不同的邏輯功能。目前,Xilinx公司Virtex系列和Spartan系列的FPGA芯片支持局部動態可重構技術[1]。自重構系統以可重構邏輯器件內嵌的微處理器實現對動態重構的控制和調配[2]。自重構系統具有從器件內部訪問配置數據的接口。Xilinx Virtex-Ⅱ以后的FPGA提供了ICAP,其主要作用就是按照特定時序將配置數據重新配置到重構區域中[3]。

Xilinx公司于2006年提出EAPR動態可重構設計方法[4]。這種方法的本質是對基于模塊的動態可重構設計方法的改進,支持高端Virtex-4以上的Virtex系列芯片,任意矩形的局部重構區域使有限的資源得到充分利用;靜態模塊的全局信號直接穿過可重構區域,靜態模塊與重構模塊使用基于Slice的總線宏進行通信,使得系統時序性能好,總線密度大。本文結合現有的基于FPGA的嵌入式系統開發流程和基于EAPR的動態可重構設計方法研究自重構系統的架構及開發流程,設計一個局部動態自重構系統,該系統有2個可重構區域,每個可重構區域有2個可重構模塊。

1 局部動態自重構系統架構

本文提出的局部動態自重構系統架構如圖1所示。PowerPC405處理器控制重構過程,兩個重構區域分別通過通用I/O設備(GPIO)和OPB_DCR_Socket模塊使能總線宏。System ACE 和ICAP配合完成系統重構,并將重構過程中的一些提示信息通過UART串口在超級終端上顯示。系統的各個主要組成部分說明如下。

(1)可編程邏輯門陣列FPGA

ML403的主芯片XC4VFX12-FF668-10C屬于Virtex-4 FX系列。Virtex-4 FX系列器件針對嵌入式處理和高速串行連接,采用90 nm工藝,密度高達20萬邏輯單元[5];將8位ICAP擴展到32位,時鐘頻率可達100 MHz,而且支持二維區域的局部動態可重構。在重構設計過程中,將FPGA劃分為可重構區域和固定區域,固定區域在系統運行過程中保持不變,通過處理器控制重構區域的重新配置實現新的邏輯功能。本文劃分為固定區域和2個可重構區域(PRR_Math和PRR_LED),每個區域有2個重構模塊,分別實現加法和乘法、LED燈向左和向右流水點亮的重構。

(2)基于Slice的總線宏

FPGA劃分的多個區域之間通過基于Slice的總線宏進行通信。總線宏是事先布好線的用來精確布線軌道的宏,其位置固定,重構時保持不變,包括基于三態緩沖器TBUF(Tri- state Buffer)的總線宏和基于Slice的總線宏。基于TBUF的總線宏結構簡單,可控制信號的傳輸方向,但不能控制信號的通斷。而在重構過程中,來自重構區域的不穩定信號可能會影響其他模塊的正常運行,所以需要在重構過程關閉總線宏,這就要求總線宏有個使能控制端口。Virtex-4以后的芯片使用基于Slice的總線宏解決了這個問題,它利用FPGA內部用作靜態路由的預留連線作為模塊之間的通信通路,在設計時,重構模塊不能使用這些資源。

(3)PowerPC硬核處理器

Virtex-4集成了一個32位的PowerPC405硬核處理器。PowerPC405經過綜合、布局布線后集成到FPGA內部的固定位置,不占用FPGA內部的任何邏輯資源和存儲單元,運行速度可達到芯片標稱值,且不影響其周邊邏輯的布局布線[3]。PowerPC采用精簡指令哈佛結構,支持5級標量流水線,具有獨立的指令和數據緩存、32個32位通用寄存器、內存管理單元和片內存儲器接口,是本文系統的核心部件之一,用于對重構過程進行控制。

(4)總線技術

PowerPC處理器支持IBM CoreConnect總線技術。本文使用的3種總線,包括處理器本地總線PLB(Process Local Bus)、片上外設總線OPB(On-chip Peripheral Bus)和設備控制寄存器DCR(Device Control Register)總線。PLB總線連接高速外設,本文中用于連接PowerPC處理器與Block RAM控制器;OPB總線用于處理器與其他低速外設之間的互連;DCR總線連接控制總線宏的寄存器。

(5)SystemACE CF

System ACE是Xilinx公司為解決多片大規模FPGA的應用而提出的一套解決方案。外部存儲器CF卡用來保存FPGA的配置文件,可直接插拔,具有非易失性。采用SystemACE CF配置方案實現動態重構具有升級速度快、配置數據安全性好等優點。重構時,首先將生成的全局初始.bit配置文件轉換成.ace文件,然后將.ace文件和部分配置文件存儲在CF卡中;開發板上電后,System ACE控制器通過JTAG端口讀取CF卡的.ace全局配置文件,對FPGA進行初始配置,PowerPC微處理器通過內部訪問配置端口 ICAP讀取重構模塊的比特流文件實現重構。

(6)ICAP

ICAP是Xilinx公司在Virtex-Ⅱ之后的FPGA中提供的一個內部配置訪問端口,HWICAP IP核將ICAP、BRAM及相關的控制器封裝在內部,掛載到OPB總線上。ICAP可以讀寫FPGA的配置數據幀。ICAP控制器負責ICAP的讀寫狀態及ICAP與BRAM之間的數據傳輸。BRAM用來保存從CF中讀取的重構模塊的比特流配置文件或者從配置存儲器中讀回的配置數據。采用ICAP方案實現自重構過程是基于“讀-修改-寫”機制的[6]。重構時,首先通過ICAP端口將需要修改的數據幀從配置存儲器讀到BRAM中;然后處理器修改這些數據幀;最后再通過ICAP將其寫回到配置存儲器中。處理器利用ICAP直接控制FPGA的重構過程,重構速度快,系統效率高。

2 系統開發流程

本文設計的自重構系統有2個可重構區域。可重構區域PRR_Math以IP核的形式實現加法和乘法的重構,重構過程通過OPB-DCR Socket模塊使能總線宏;可重構區域PRR_LED實現開發板上的4個LED燈向左和向右流水點亮的重構。這2個模塊通過ISE生成網表,完成布局布線,以GPIO作為總線宏的使能端口。靜態模塊實現對LED燈的控制,當按下暫定鍵時,LED暫停流水點亮;當按下開始鍵時,LED開始流水點亮。系統上電后,首先System ACE控制器通過JTAG端口讀取存儲在CF卡中的.ace文件對FPGA進行初始全局配置,初始的全局配置實現乘法和向右流水點亮LED。開發板通過串口UART與PC通信,并通過超級終端進行顯示和調試。重構時,在超級終端鍵入命令,處理器接受命令后,通過ICAP讀取相應的重構模塊對FPGA重新配置,通過在超級終端上測試和觀察開發板LED的變化驗證重構是否實現。本文采用基于EAPR的局部動態重構設計方法進行系統設計,開發流程如圖2所示。

(1)設計輸入和綜合

系統包括靜態模塊、可重構模塊和頂層模塊。靜態模塊是除了重構模塊以外的所有模塊,包括處理器模塊。靜態模塊實現對LED燈的控制,處理器模塊控制重構過程。2個重構區域分別有2個重構模塊,同一重構區域的可重構模塊具有相同的端口定義和實體名,要放在不同目錄下分別進行綜合。靜態模塊和所有的重構模塊在綜合時都不添加I/O端口。頂層模塊只進行各個模塊的例化,即只定義模塊的端口信號,而不進行具體的行為描述,包括處理器模塊、靜態模塊、重構模塊、總線宏、時鐘及一些信號聲明等。頂層模塊在綜合時要添加I/O端口。完成這一步驟將產生所有模塊的.ngc網表文件。

(2)軟硬件設計

在XPS中搭建系統硬件平臺,添加所需IP核,硬件平臺如圖3所示。在SDK上進行軟件編程和調試,生成executable.elf可執行文件。

(3)添加約束

利用PlanAhead添加約束,如區域約束、時序約束和引腳、時鐘、總線宏的位置約束等。添加各約束之后運行DCR檢查是否滿足設計要求。

(4)實現模塊

靜態模塊和重構模塊的實現包括轉換、映射和布局布線3個步驟。重構模塊必須在靜態模塊成功實現之后才可進行。

(5)合并

運行PR Assemble將各個模塊合并,產生各重構模塊的.bit文件、各區域的空位流文件和一個包含靜態模塊及動態模塊的全配置文件static_full.bit。生成的static_full.bit文件只含有硬件信息,需要將此文件和system_stub.bmm、executable.elf文件合并成包含軟硬件完整信息的download.bit文件。

(6)轉換文件

系統上電后,通過讀取CF卡中的.ace文件對FPGA芯片進行初始配置,將上一步生成的download.bit轉換為CF可執行的.ace文件。

(7)設計驗證

將生成的system.ace、重構配置文件和空位流文件下載到CF卡的根目錄下,連接開發板與PC進行設計驗證和調試。

3 實驗結果

在Xilinx XC4VFX12FF668-10 ML403開發板上進行驗證,開發板的配置模式設計為JTAG方式,配置資源選擇開關打向System ACE端,串口線連接開發板與PC,打開超級終端,超級終端設置波特率為115 200 b/s,8 bit數據位,無奇偶校驗,這里的設置和創建硬件平臺系統的設置要保持一致。系統上電后,讀取system.ace文件完成初始配置后,開發板上的DONE指示燈變為綠色,說明配置成功完成,這時激活的乘法模塊和右移模塊開始工作。觀察到4個LED燈向右流水點亮,當按下暫停鍵時,LED停止流水點亮;當按下開始鍵時,LED開始向右流水點亮。超級終端顯示提示信息,輸入O后系統提示要輸入兩個操作數,完成乘法運算。結果顯示如圖4所示。

根據提示命令,輸入a或A命令實現加法運算,輸入l或L命令實現向左流水點亮LED燈;輸入o或O命令,系統接收兩個操作數后執行加法運算,并將運算結果顯示在超級終端上。觀察開發板的4個LED燈變成向左流水點亮,按下暫停鍵,LED停止流水點亮;按下開始鍵,LED開始向左流水點亮。超級終端顯示如圖5所示。

當系統不需要執行重構模塊的功能時,可根據提示輸入空白配置文件的相應命令使系統處于待機模式。當需要時再輸入相應命令進行配置。這樣可減少系統的功耗。

重構時間是重構系統的一個關鍵指標。理論上,重構時間等于配置文件大小與配置速率的比值。實際上,還需要考慮總線的傳輸速率和HWICAP的配置速率。本文只從理論上分析重構時間,而重構時間和配置文件大小成正比,生成的配置文件大小如表1所示。從表中可以看出,重構模塊的配置文件比全局配置文件大幅度減小,采用局部動態配置時,只需下載重構模塊的配置模塊,重構時間也將大幅度縮短。另外,本文系統通過ICAP配置,ICAP數據位寬為32 bit,時鐘頻率為100 MHz,配置速率很高,所以在重構時間上具有一定的優勢。

本文采用EAPR方法,利用ML403開發板集成的PowerPC405微處理器設計驗證系統的自重構功能。在系統運行過程中,可以替換或停止某一不需要或出錯的功能模塊來保證系統不間斷地運行。系統采用軟硬件協同設計,使設計流程并行化,開發周期短,硬件分時復用,資源利用率高。基于EAPR的局部動態自重構技術已經成為業界的研究熱點,隨著技術不斷成熟,將逐步應用到實際產品中。

編輯:lyn

-

FPGA

+關注

關注

1643文章

21982瀏覽量

614568 -

總線技術

+關注

關注

3文章

83瀏覽量

41039 -

可編程邏輯

+關注

關注

7文章

524瀏覽量

44597 -

硬核處理器

+關注

關注

0文章

3瀏覽量

6852

發布評論請先 登錄

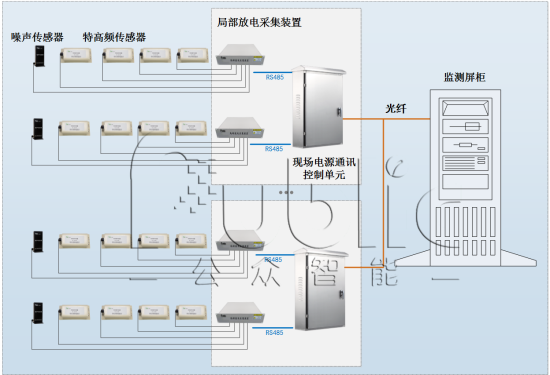

實現局部放電在線監測的不同

?數字孿生熱管理:NTC熱敏電阻陣列與熱場重構算法的動態適配

GIS局部放電在線監測系統核心功能設計

深控技術不需要點表的工業數采動態產線重構支持方案

充電樁負載測試系統技術解析

汽車排氣系統點焊技術解析與應用

國外物理服務器詳細解析

基于相變材料的可重構超構表面用于圖像處理

局部放電檢測裝置 局部放電檢測系統

基于EAPR的局部動態自重構系統的實現詳細解析

基于EAPR的局部動態自重構系統的實現詳細解析

評論