引言

近年來(lái),無(wú)線(xiàn)同播系統(tǒng)在民事和警事中的應(yīng)用日益廣泛,其快速搭建和空中接入等優(yōu)勢(shì)在512地震的救災(zāi)調(diào)度中得以充分體現(xiàn)。同播系統(tǒng)工作時(shí),所有發(fā)射站會(huì)在同一時(shí)刻點(diǎn)以相同頻率向外廣播,由于各站的發(fā)射頻率相對(duì)于標(biāo)準(zhǔn)頻率有不同偏差,在功率重疊區(qū)產(chǎn)生頻率疊加,出現(xiàn)同頻干擾。目前,國(guó)內(nèi)外通信廠(chǎng)家的同播發(fā)射機(jī)的發(fā)射頻率偏差大都在1ppm(parts per million)以上,不通過(guò)校準(zhǔn),無(wú)法達(dá)到0.05ppm正常通話(huà)的最低要求。有線(xiàn)同播系統(tǒng)是利用光纖網(wǎng)絡(luò)校準(zhǔn)發(fā)射頻率的。無(wú)線(xiàn)同播系統(tǒng)目前只能通過(guò)兩種方法解決:一是設(shè)置中心站,但系統(tǒng)響應(yīng)速度慢;二是盡量縮小功率重疊區(qū),其建站周期長(zhǎng)而且可靠性低。兩種方法都沒(méi)有從根本上解決無(wú)線(xiàn)同播系統(tǒng)的同頻干擾,發(fā)射頻率的校準(zhǔn)已經(jīng)成為無(wú)線(xiàn)同播系統(tǒng)發(fā)展的瓶頸。因此,本文提出一種基于FPGA技術(shù)的頻率校準(zhǔn)系統(tǒng)的設(shè)計(jì)方案。

1 系統(tǒng)總體設(shè)計(jì)

1.1 同頻干擾的產(chǎn)生和解決方法

一個(gè)無(wú)線(xiàn)同播系統(tǒng)需要架設(shè)若干個(gè)大功率發(fā)射站點(diǎn),才能滿(mǎn)足大區(qū)域的通信需求。站點(diǎn)間硬件和工作環(huán)境各有差異,導(dǎo)致各站的頻率偏差不同。例如兩個(gè)發(fā)射頻率為 350MHz的站點(diǎn),一個(gè)的頻偏為+1ppm,另一個(gè)為-1ppm,在功率重疊區(qū)就會(huì)產(chǎn)生700Hz的頻率差,形成嘯聲,影響通話(huà)質(zhì)量。從理論上講,要保證同頻覆蓋區(qū)的通話(huà)質(zhì)量,必須使各發(fā)射站的頻偏保持在0.05ppm以下。校準(zhǔn)各發(fā)射站頻率的最好方法,是為其提供統(tǒng)一可靠的基準(zhǔn)時(shí)鐘信號(hào)。GPS定位衛(wèi)星信號(hào)精度高,沒(méi)有時(shí)間和地域的限制,可以作為基準(zhǔn)時(shí)鐘信號(hào)同步各站的基準(zhǔn)振蕩器,解決同頻干擾的關(guān)鍵性問(wèn)題。

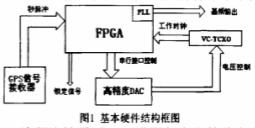

1.2 系統(tǒng)硬件設(shè)計(jì)

頻率校準(zhǔn)系統(tǒng)主要由高精度GPS信號(hào)接收器、FPGA芯片、VC-TC2XO(壓控恒溫晶振)、高精度DAC(數(shù)模轉(zhuǎn)換器)等部分組成。VC-TCXO為 FPGA提供工作時(shí)鐘,也為發(fā)射提供基準(zhǔn)頻率。FPGA通過(guò)GPS秒脈沖信號(hào)計(jì)算標(biāo)準(zhǔn)時(shí)長(zhǎng),記錄下這段時(shí)間內(nèi)VC-TCXO產(chǎn)生的脈沖總數(shù),與標(biāo)準(zhǔn)的脈沖數(shù)進(jìn)行對(duì)比,最后通過(guò)DAC對(duì)VC-TCXO進(jìn)行電壓校正。校準(zhǔn)后的VC-TCXO頻率通過(guò)FPGA內(nèi)部PLL倍頻,成為發(fā)射頻率。基本硬件結(jié)構(gòu)框圖如圖 1所示。

FPGA編程比較靈活,可設(shè)置任意位的片上寄存器,保證了脈沖計(jì)數(shù)的精度,適用于高精度的頻率校準(zhǔn)。本設(shè)計(jì)采用Actel公司Fusion系列的 AFS600,屬于Flash架構(gòu),內(nèi)部集成了60萬(wàn)邏輯門(mén)。以Flash為基礎(chǔ)的FPGA將配置信息儲(chǔ)存在片上Flash單元中,一旦完成編程,配置數(shù)據(jù)就會(huì)成為FPGA結(jié)構(gòu)的固有部分,在系統(tǒng)上電時(shí)無(wú)需通過(guò)外部SRAM載入配置數(shù)據(jù)。AFS600可靠性高、功耗低,節(jié)省外部元件,適合開(kāi)發(fā)手持設(shè)備。

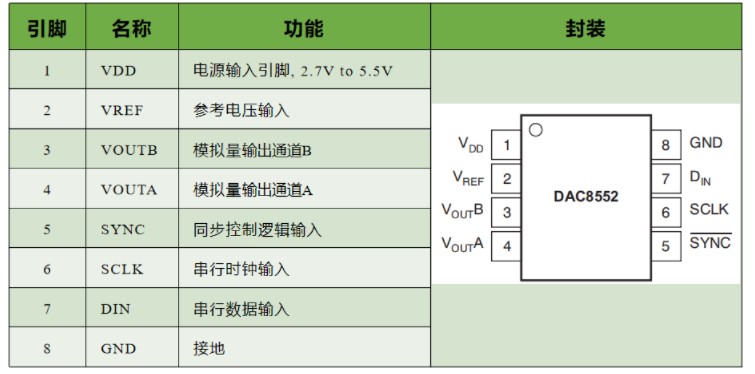

本設(shè)計(jì)采用的GPS接收機(jī)是Motorola公司生產(chǎn)的M12M授時(shí)型OEM模塊,輸出秒脈沖信號(hào)的精度±20ns。壓控恒溫晶振采用華晶達(dá)電子公司的 VC-TCXO(503212.8M),中心頻率12.8MHz,工作電壓3.3V,溫度穩(wěn)定度±1.0ppm,老化率±1.0ppm/年,控制電壓范圍 1.65±1.0v,可調(diào)節(jié)頻率范圍1 2.8MHz±300Hz。高精度DAC采用TI公司的。DAC8552,具有16位精度,可串行SPI控制方式,參考電壓為3.3V。

1.3 分級(jí)控制方案

基于效率和精度的需要,本設(shè)計(jì)采用分級(jí)控制方案。GPS秒脈沖信號(hào)的精度誤差為20ns,折算12.8MHz頻率,最大頻偏為20ppm。若以1秒作為時(shí)長(zhǎng)比較脈沖數(shù),調(diào)整的精度無(wú)法達(dá)到要求,同頻干擾依然存在。由于秒脈沖信號(hào)的精度誤差呈均勻分布,加長(zhǎng)檢測(cè)的時(shí)間可以提高信號(hào)精度,從而提高校準(zhǔn)精度。但校準(zhǔn)效率會(huì)下降,發(fā)射準(zhǔn)備時(shí)間增加。另一方面,DAC的控制方式也影響系統(tǒng)的精度和效率。單次調(diào)整幅度大,效率高但精度低,幅度小則需時(shí)過(guò)長(zhǎng),所以不能以固定的幅度調(diào)整。根據(jù)VC-TCXO和DAC8552的參數(shù),DAC最小的調(diào)整幅度為0.015Hz,DAC數(shù)值與VC-TCXO頻率的關(guān)系是:

f(b)=12.8MHz+ (b-b)×O.015Hz

式中f(b)是當(dāng)前VC-TCXO頻率,b是FPGA寫(xiě)入DAC的數(shù)值,b’是VC-TCXO輸出12.8MHz時(shí)對(duì)應(yīng)的DAC數(shù)值。VC-TCXO的電壓可調(diào)范圍是1.65±1.0V,折算b的有效范圍為12 909~52 627。

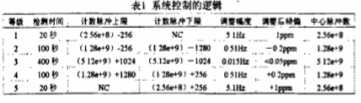

為了平衡精度和效率的需要,系統(tǒng)采用了分級(jí)控制的方案。如表1所示,系統(tǒng)控制的邏輯分為五級(jí)。等級(jí)3的頻偏和調(diào)整幅度最小,檢測(cè)時(shí)間最長(zhǎng)。脈沖數(shù)上下限用于固定時(shí)長(zhǎng)內(nèi)脈沖數(shù)的比較,判斷是否需要調(diào)級(jí)。VC-TCXO的溫度和老化的因素使晶體頻率的上下限改變,所以等級(jí)1沒(méi)有計(jì)數(shù)脈沖下限,等級(jí)5沒(méi)有上限。 FPGA根據(jù)當(dāng)前的級(jí)別設(shè)定檢測(cè)時(shí)間,再通過(guò)收到的脈沖數(shù)判斷升級(jí)、降級(jí)或是調(diào)整電壓值。

2 FPGA設(shè)計(jì)

2.1 FPGA頂層設(shè)計(jì)

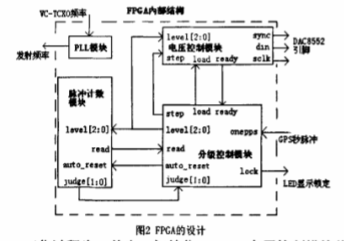

FPGA的設(shè)計(jì)采用自頂向下的設(shè)計(jì)方法,用Verilog HDL語(yǔ)言描述,在Actel公司的開(kāi)發(fā)軟件libero8.0中進(jìn)行綜合、優(yōu)化、仿真和定時(shí)分析。頂層設(shè)計(jì)由PLL、分級(jí)控制、脈沖計(jì)數(shù)模塊以及電壓控制模塊組成,如圖2所示。

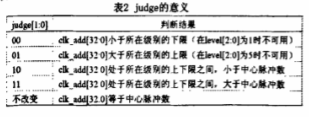

工作過(guò)程為:首先,初始化FPGA,電壓控制模塊將DAC8552的電壓輸出值置于中位(1.65V),分級(jí)控制模塊的開(kāi)始分級(jí)設(shè)定為3,并通過(guò) level[2∶0]連線(xiàn)將級(jí)別賦給脈沖計(jì)數(shù)模塊和電壓控制模塊;分級(jí)控制模塊收到GPS秒脈沖時(shí),通過(guò)auto reset啟動(dòng)脈沖計(jì)數(shù)模塊,收到read信號(hào)時(shí)讀入judge[1∶0],judge[1∶0]的意義如表2所示。如果 judge[1∶0]=00,level[2∶0]不為1,level[2∶0]降級(jí);judge[1∶0]=01,level[2∶0]不為 5,level[2∶0]升級(jí);judge[1∶0]為10或11,通過(guò)step和load引腳調(diào)整電壓控制模塊。

2.2 脈沖計(jì)時(shí)模塊設(shè)計(jì)

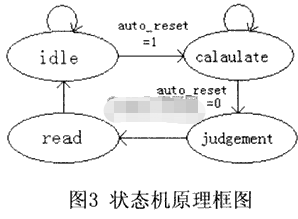

脈沖計(jì)時(shí)模塊接口信號(hào)包括:級(jí)別輸入level[2∶0]、開(kāi)始計(jì)數(shù)輸入auto_reset、判斷輸出judge[1∶0]、讀指令輸出read,還有輸入時(shí)鐘fre_in和復(fù)位使能reset,模塊內(nèi)部設(shè)寄存器clk_add[32∶0],用于脈沖計(jì)數(shù)。模塊的狀態(tài)包括idle、calculate、 judgment和readtime,狀態(tài)機(jī)如圖3所示。

其具體工作過(guò)程為:

(1)狀態(tài)為idle時(shí),read置0,clk add[32∶0]清空,讀入level值。Level是計(jì)數(shù)判斷的基準(zhǔn),必須在計(jì)數(shù)前讀入。

(2)當(dāng)收到auto_reset為高電平,狀態(tài)從idle轉(zhuǎn)至calculate開(kāi)始脈沖計(jì)數(shù)。由于計(jì)數(shù)的頻率同時(shí)是FPGA的工作頻率,所以 clk_add[32∶0]只需在calculate狀態(tài)下每個(gè)時(shí)鐘累加一次。

(3)auto_reset變?yōu)榈蜁r(shí),狀態(tài)轉(zhuǎn)至judgment,將clk_add[32∶0]與所在級(jí)別的上下限對(duì)比,將結(jié)果通過(guò)judge[1∶0] 輸出。

(4)狀態(tài)轉(zhuǎn)至readtime,將read置1,read信號(hào)告知分級(jí)控制模塊judge[1∶0]信號(hào)已經(jīng)更新,要求讀取,當(dāng)clk_add [32∶0]等于中心脈沖數(shù),read不置為1,表示無(wú)需改變電壓值。

(5)狀態(tài)轉(zhuǎn)回idle。

2.3 電壓控制模塊設(shè)計(jì)

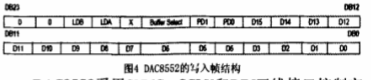

電壓控制模塊的接口信號(hào)包括:級(jí)別輸入level[2∶0]、調(diào)整方向輸入step、調(diào)整輸入load、就緒輸出ready、DAC接口輸出(sync、 SClk和din),還有輸入時(shí)fre_in和復(fù)位使能reset,模塊內(nèi)部設(shè)寄存器data reg[23∶0]用于生成控制DAC的幀,max_24bits[4∶0]用于記錄當(dāng)前是控制幀的第幾位輸出。每幀長(zhǎng)度為24位,控制字包括:LDB、 LDA選擇寫(xiě)入通道,Buffer Select選擇寫(xiě)入的寄存器,PDl、PD0選擇輸出阻抗模式,D15~D0為16位的DAC數(shù)據(jù)。其幀結(jié)構(gòu)如圖4所示。

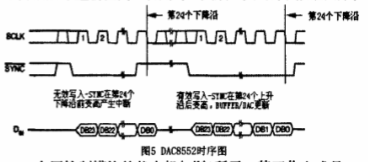

DAC8552采用SYNC、SCLK和DIN三線(xiàn)接口控制方式,從SYNC變低時(shí)開(kāi)始寫(xiě)入,SCLK產(chǎn)生寫(xiě)時(shí)鐘,在SCLK下降沿?cái)?shù)據(jù)被寫(xiě)入 DAC8552,SYNC必須在第24個(gè)下降沿后才重新拉高,否則寫(xiě)入失敗。其時(shí)序圖如圖5所示

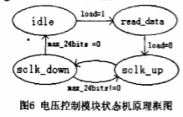

電壓控制模塊的狀態(tài)機(jī)如圖6所示,其工作方式是:

(1)idle狀態(tài)時(shí),ready輸出賦為1,sclk賦為1,sync賦為1,max_24bits賦為24。

(2)當(dāng)load=1時(shí),狀態(tài)轉(zhuǎn)至idle,sync賦為0,data reg通過(guò)level和step引腳的值產(chǎn)生相應(yīng)的控制幀。

(3)當(dāng)load=0時(shí),狀態(tài)轉(zhuǎn)至sclk_up,sclk賦為1,din賦為data_reg[max_24bits-1]。

(4)狀態(tài)轉(zhuǎn)至sclk down,sclk賦為0,max_24bits自減1。當(dāng)max_24bits=0時(shí),狀態(tài)轉(zhuǎn)至idle;否則狀態(tài)轉(zhuǎn)至sclk_up。

狀態(tài)sclk_up和sclk_down的循環(huán)是用于產(chǎn)生控制DAC8552的時(shí)鐘和數(shù)據(jù),din通過(guò)max_24bits這個(gè)寄存器實(shí)現(xiàn)對(duì) data_reg從高到低逐位輸出。

3 實(shí)驗(yàn)結(jié)果

3.1 軟件仿真

利用Libero 8.0開(kāi)發(fā)環(huán)境集成的Modelsim軟件對(duì)電壓控制模塊設(shè)計(jì)進(jìn)行仿真。模擬寫(xiě)入DAC8552的A、B通道數(shù)據(jù)為1010 1111 OO10 1011,十進(jìn)制為44843,折算為電壓值是2.258V。仿真時(shí)序圖如圖7所示,滿(mǎn)足DAC8552接口的時(shí)序要求。

3.2 板上調(diào)試

將程序燒入FPGA運(yùn)行,并通過(guò)頻率計(jì)實(shí)際測(cè)量,測(cè)量結(jié)果如圖8所示。由于頻率計(jì)的精度只達(dá)到1Hz,測(cè)量的數(shù)據(jù)會(huì)有所偏差。考慮到校準(zhǔn)后的頻偏已經(jīng)接近+0.05ppm(+0.64Hz),證明系統(tǒng)功能已經(jīng)實(shí)現(xiàn)。但系統(tǒng)的效率不夠高,需時(shí)過(guò)長(zhǎng),算法有待改善。

4 結(jié)束語(yǔ)

本設(shè)計(jì)通過(guò)FPGA、高精度DAC、壓控恒溫晶振和GPS信號(hào)接收模塊,成功實(shí)現(xiàn)了同播系統(tǒng)發(fā)射設(shè)備的頻率校準(zhǔn)。除了同播系統(tǒng),本設(shè)計(jì)還可應(yīng)用于衛(wèi)星信號(hào)同步、跳頻通信的相關(guān)領(lǐng)域,發(fā)展空間十分廣闊。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1643文章

21983瀏覽量

614630 -

芯片

+關(guān)注

關(guān)注

459文章

52253瀏覽量

437009 -

接收機(jī)

+關(guān)注

關(guān)注

8文章

1219瀏覽量

54261

發(fā)布評(píng)論請(qǐng)先 登錄

DAC8552高精度模數(shù)轉(zhuǎn)換器的驅(qū)動(dòng)設(shè)計(jì)與實(shí)現(xiàn)

利用dac8551/dac8552芯片通過(guò)3伏基準(zhǔn)電壓芯片產(chǎn)生0到150mv的電壓信號(hào),可以強(qiáng)制讓電壓不超過(guò)150mv嗎?

DAC8552 VDD在上電或斷電過(guò)程中,Pin3和Pin4腳有輸出過(guò)沖的原因?

使用DAC8552時(shí),當(dāng)該芯片的SYNC引腳未選中時(shí),請(qǐng)問(wèn)該芯片的兩個(gè)電壓輸出引腳的電壓是多少?

DAC8552主控制器的MISO引腳不接可以嗎?怎么處理?

Cortex M3系列的LPC1768操作DAC8552問(wèn)題

MSP430使用DAC8552的問(wèn)題

如何利用AFS600設(shè)計(jì)太陽(yáng)能熱水器通用控制器?

DAC8552,pdf(16-Bit, Dual Chann

基于AFS600芯片與8051的陽(yáng)能熱水器控制器的設(shè)計(jì)

時(shí)間頻率遠(yuǎn)程校準(zhǔn)系統(tǒng)的設(shè)計(jì)

基于GPS的恒溫晶振頻率校準(zhǔn)系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

DAC8552雙通道、電壓輸出數(shù)模轉(zhuǎn)換器(DAC)數(shù)據(jù)表

基于AFS600和DAC8552芯片實(shí)現(xiàn)頻率校準(zhǔn)系統(tǒng)的設(shè)計(jì)

基于AFS600和DAC8552芯片實(shí)現(xiàn)頻率校準(zhǔn)系統(tǒng)的設(shè)計(jì)

評(píng)論