1. 塊語(yǔ)句有兩種,一種是 begin-end 語(yǔ)句, 通常用來(lái)標(biāo)志()執(zhí)行的語(yǔ)句;一種是 fork-join 語(yǔ)句,通常用來(lái)標(biāo)志()執(zhí)行的語(yǔ)句。

答案:順序,并行

解析:

(1)begin_end順序塊,用于將多條語(yǔ)句組成順序塊,語(yǔ)句按順序一條一條執(zhí)行(除了帶有內(nèi)嵌延遲控制的非阻塞賦值語(yǔ)句),每條語(yǔ)句的延遲時(shí)間是相對(duì)于由上一條語(yǔ)句的仿真時(shí)間而言;

(2)fork-join并行塊,塊內(nèi)語(yǔ)句同時(shí)執(zhí)行。

2. 塊語(yǔ)句,下面這段語(yǔ)句中,第 40 時(shí)刻上,A、B 的值各是多少?

reg A;reg B;initial begin fork begin A = 1; #20 A = 0; #30 A = 1; #50 A = 0; end begin B = 1; #20 B = 0; #30 B = 1; #50 B = 0; end joinend

答案:A = 0,B = 0

解析:

塊語(yǔ)句有兩種,begin...end 和 fork...join,其中 fork...join 是并行塊,begin...end 是順序執(zhí)行塊,可以相互嵌套。

上面,兩個(gè) begin...end 之間是并行的,而各自 begin...end 內(nèi)部是順序執(zhí)行,A 和 B 的賦值邏輯是一樣的,所以要么都是 1,要么都是 0。

按照順序執(zhí)行,A 前 20 個(gè)時(shí)間單位是 1,然后持續(xù) 30 個(gè)時(shí)間單位的 0,所以 40 時(shí)刻是 0,同理 B 也是 0。

原文標(biāo)題:Verilog 的塊語(yǔ)句 fork...join 和 begin...end

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

111987 -

語(yǔ)句表

+關(guān)注

關(guān)注

0文章

8瀏覽量

7282

原文標(biāo)題:Verilog 的塊語(yǔ)句 fork...join 和 begin...end

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

淺談Verilog和VHDL的區(qū)別

AMC1204有兩種封裝,SOIC-8和SOIC-16,功能一樣嗎?為什么要推出兩種封裝?

solidworks正版軟件:永久版權(quán)和訂閱許可 兩種購(gòu)買方式解析和選擇

ADS1292R有 \"1 ch ECG + 1 ch呼吸偵測(cè)\" 或 \"2 ch ECG\" 兩種模式,是否可以在產(chǎn)品上實(shí)現(xiàn)自行切換兩種使用模式?

Verilog HDL的基礎(chǔ)知識(shí)

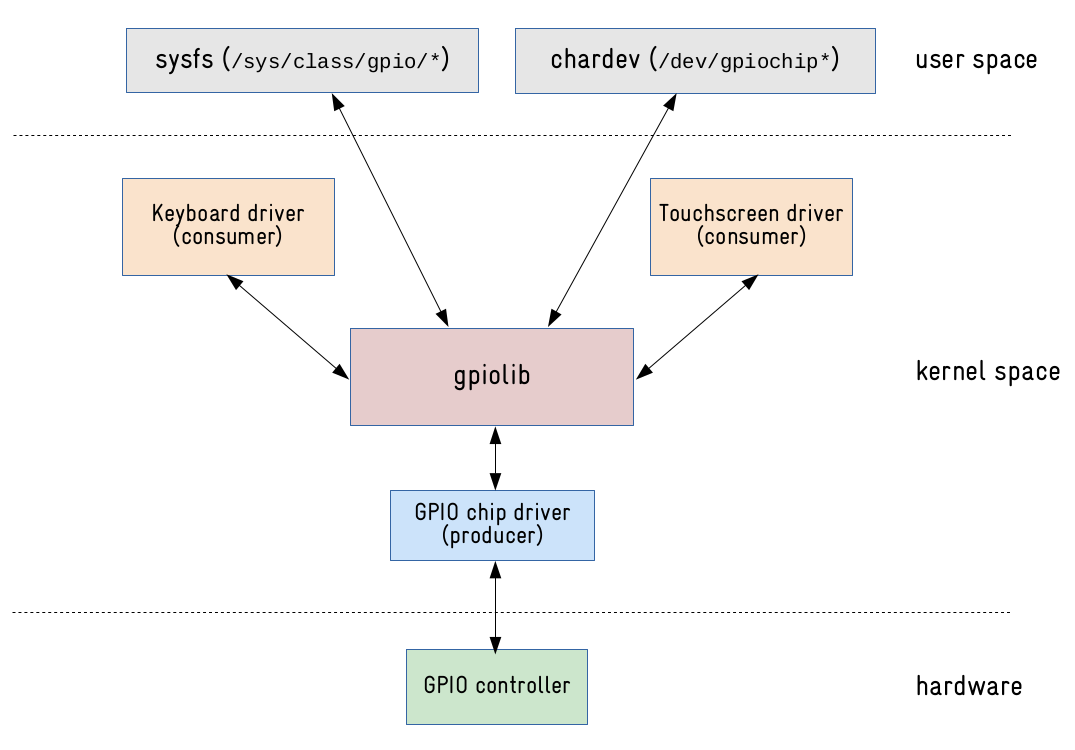

Linux應(yīng)用層控制外設(shè)的兩種不同的方式

比較分析兩種不同的可提高柵極驅(qū)動(dòng)電流的方法

Verilog的兩種塊語(yǔ)句解析

Verilog的兩種塊語(yǔ)句解析

評(píng)論