文章來源:老虎說芯

原文作者:老虎說芯

Verilog和VHDL是兩種廣泛使用的硬件描述語言(HDL),它們用于描述和模擬數(shù)字電路系統(tǒng)的行為和結構。這兩種語言的主要作用是幫助工程師設計、仿真和驗證集成電路(IC)和系統(tǒng)級芯片(SoC)中的硬件模塊。

1. Verilog

Verilog 是一種硬件描述語言,最初由 Gateway Design Automation 公司在 1984 年開發(fā),后由 IEEE 進一步標準化(IEEE 1364)。Verilog 用于描述數(shù)字電路的行為和結構,并且在 FPGA 和 ASIC(專用集成電路)設計中得到了廣泛應用。

Verilog的特點:

結構化和行為描述:Verilog 支持兩種主要的描述方式:

結構化描述:通過連接標準單元或模塊來定義硬件的結構。

行為描述:通過描述硬件的邏輯行為來定義電路,類似編程語言中的算法。

模塊化:Verilog 是模塊化的,電路設計被劃分為多個模塊,每個模塊可以獨立開發(fā)和測試。

并行性:Verilog 支持并行描述,能夠有效地描述并行工作的硬件組件(例如多個邏輯門同時工作)。

Verilog的主要用途:

功能描述:設計者可以使用 Verilog 描述電路的邏輯行為,例如加法器、寄存器、時鐘等。

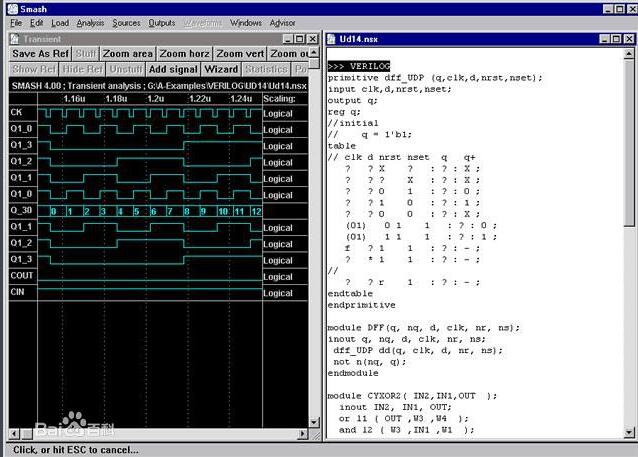

仿真:設計者通過仿真驗證 Verilog 描述的電路是否按預期工作,通常通過仿真工具來運行 Verilog 代碼,檢查電路的功能和時序。

綜合:將 Verilog 代碼轉化為實際的硬件電路,綜合工具根據(jù) Verilog 中的描述生成網(wǎng)表,并為后續(xù)的布局布線過程做準備。

2. VHDL

VHDL(VHSIC Hardware Description Language)是另一種硬件描述語言,最初由美國國防部(DoD)在 1980 年代開發(fā)。它同樣用于描述電子系統(tǒng),特別是在數(shù)字設計中廣泛應用,尤其是對復雜系統(tǒng)(如 SoC 和 FPGA)進行建模和仿真。

VHDL的特點:

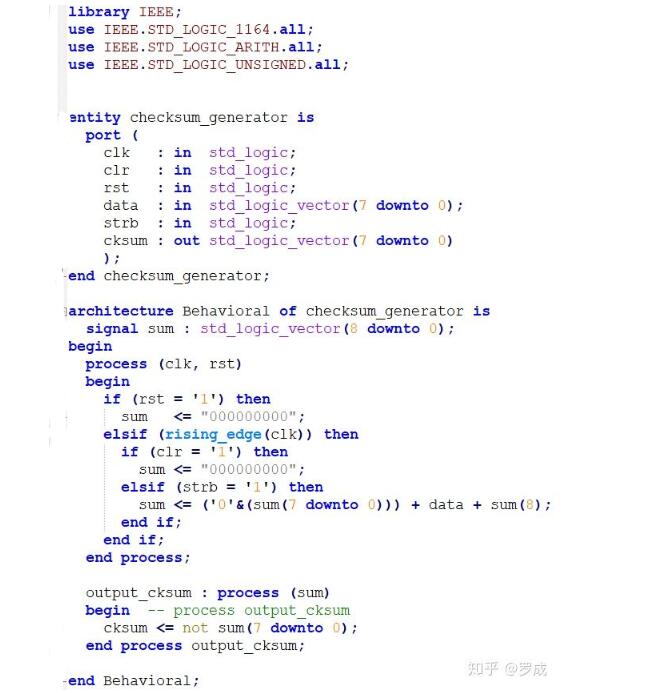

強類型:VHDL 是一種類型非常嚴格的語言,數(shù)據(jù)類型和信號必須明確指定,有助于捕獲設計錯誤。

并行和順序描述:與 Verilog 類似,VHDL 支持并行和順序兩種描述方式。并行描述用于定義多個模塊同時工作的情況,順序描述則模擬邏輯流程。

結構化和行為描述:VHDL 同樣支持結構化和行為描述,結構化描述類似于硬件的模塊化設計,而行為描述則專注于電路的功能實現(xiàn)。

VHDL的主要用途:

電路建模和仿真:設計者可以使用 VHDL 來建模電路的行為和結構,并進行仿真驗證。

綜合與優(yōu)化:VHDL 代碼可以通過綜合工具轉化為實際硬件。與 Verilog 類似,綜合工具根據(jù) VHDL 描述生成門級網(wǎng)表,并進一步進行布局和布線。

驗證和測試:VHDL 還可以用于為硬件模塊編寫測試平臺,進行功能驗證和時序分析。

3. Verilog 和 VHDL 的比較:

4. 選擇 Verilog 或 VHDL:

在實際使用中,Verilog 和 VHDL 都可以完成類似的任務,但它們各自有不同的優(yōu)缺點:

Verilog 通常更適合需要快速開發(fā)和仿真的項目,特別是在較為簡單的設計和硬件驗證過程中,Verilog 的簡潔性使得開發(fā)效率較高。

VHDL 更適合于復雜、龐大的系統(tǒng)設計,特別是對類型和結構要求較高的系統(tǒng)。由于其強類型的特性,VHDL 能更好地捕捉設計中的潛在問題,但其相對復雜的語法也增加了學習曲線。

5. 總結

Verilog 和 VHDL 都是現(xiàn)代集成電路設計中不可或缺的工具,它們提供了強大的功能來描述和仿真數(shù)字系統(tǒng)。兩者的選擇通常取決于設計的復雜度、開發(fā)工具的支持以及團隊的技術背景。Verilog 以簡潔和高效著稱,適合快速迭代的設計,而 VHDL 則以嚴格的類型檢查和結構化設計著稱,適合更復雜的系統(tǒng)設計。

-

集成電路

+關注

關注

5424文章

12044瀏覽量

368381 -

Verilog

+關注

關注

29文章

1367瀏覽量

112253 -

vhdl

+關注

關注

30文章

820瀏覽量

129934 -

硬件描述語言

+關注

關注

0文章

11瀏覽量

12139

原文標題:硬件描述語言Verilog和VHDL的區(qū)別?

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

關于VHDL和verilog的幾點疑問

VHDL和Verilog HDL語言對比

VHDL,Verilog,System verilog比較

vhdl和verilog的區(qū)別_vhdl和verilog哪個好?

Verilog HDL和VHDL的區(qū)別

vhdl轉換為verilog_VHDL和Verilog誰更勝一籌

探討VHDL和Verilog模塊互相調(diào)用的問題

Verilog HDL verilog hdl和vhdl的區(qū)別

Verilog到VHDL轉換的經(jīng)驗與技巧總結

淺談Verilog和VHDL的區(qū)別

淺談Verilog和VHDL的區(qū)別

評論