來(lái)源:木子陳

電阻的測(cè)試分為方塊電阻和接觸電阻,方塊電阻是電路設(shè)計(jì)的重要組成部分,其阻值準(zhǔn)確性嚴(yán)重影響電路的性能,F(xiàn)ab廠通過(guò)WAT參數(shù)方塊電阻Rs監(jiān)測(cè)它們。CMOS工藝中方塊電阻主要類型有:

- NW方塊電阻

- PW方塊電阻

- Poly方塊電阻

- AA方塊電阻

- Metal方塊電阻

目前業(yè)界通用的方塊電阻的測(cè)試方法有三種:一種是電阻條圖形;一種是范德堡圖形;一種是開爾文圖形。這里以電阻條作為例子介紹相關(guān)測(cè)試。

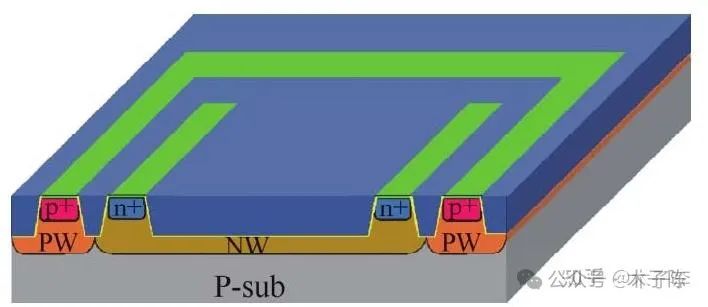

1.NW方塊電阻

NW方塊電阻是三端器件,它的三個(gè)端口分別是電阻的兩端和襯底(P-sub),它們分別連到PAD_N1、PAD_N2和PAD_B,WAT測(cè)試機(jī)器通過(guò)這三個(gè)端口把電壓激勵(lì)信號(hào)加載在電阻的兩端和襯底,從而測(cè)得所需的電性特性參數(shù)數(shù)據(jù)。NW方塊電阻的WAT參數(shù)是Rs_NW。

測(cè)量NW方塊電阻Rs_NW的基本原理是在電阻的一端加載DC電壓1V,另一端和襯底接地,從而測(cè)得電流In,Rs_NW=(1/In)/(L/W),W和L分別是NW方塊電阻的寬度和長(zhǎng)度。

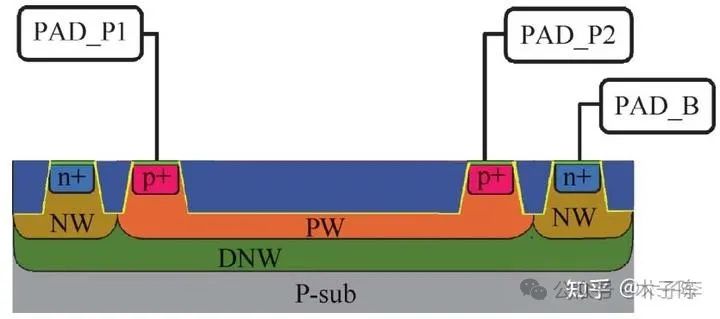

2. PW方塊電阻

與NW電阻不同,在bulk wafer中,PW方塊電阻是通過(guò)DNW隔離襯底(P-sub),如果沒有DNW的隔離,這個(gè)PW方塊電阻會(huì)與P-sub短路。

PW方塊電阻是三端器件,它的三個(gè)端口分別是電阻的兩端和襯底(DNW),它們分別連到PAD_P1、PAD_P2和PAD_B,WAT測(cè)試機(jī)器通過(guò)這三個(gè)端口把電壓激勵(lì)信號(hào)加載在電阻的兩端和襯底,從而測(cè)得所需的電性特性參數(shù)數(shù)據(jù)。PW方塊電阻的WAT參數(shù)是Rs_PW。

測(cè)量PW方塊電阻Rs_PW的基本原理是在電阻的一端和襯底加載電壓DC電壓1V,另一端接地,從而測(cè)得電流Ip,Rs_PW=(1/Ip)/(L/W),W和L分別是PW方塊電阻的寬度和長(zhǎng)度。

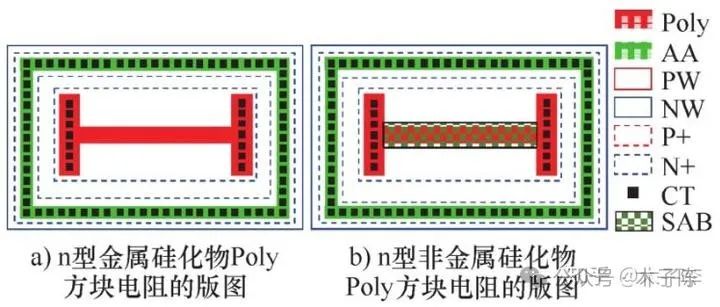

3.Poly方塊電阻

CMOS工藝平臺(tái)的Poly方塊電阻有四種類型的電阻,

n型金屬硅化物Poly方塊電阻

p型金屬硅化物Poly方塊電阻

n型非金屬硅化物Poly方塊電阻

p型非金屬硅化物Poly方塊電阻

Poly方塊電阻的測(cè)試結(jié)構(gòu)主要分為兩種,第一種是狗骨頭狀的測(cè)試結(jié)構(gòu),第二種是蛇形的測(cè)試結(jié)構(gòu),如下圖所示。

Poly方塊電阻是三端器件,它的三個(gè)端口分別是電阻的兩端和襯底(NW),它們分別連到PAD_P1、PAD_P2和PAD_B。WAT測(cè)試機(jī)器通過(guò)電阻兩端的端口把電壓激勵(lì)信號(hào)加載在電阻的兩端,從而測(cè)得所需的電性特性參數(shù)數(shù)據(jù)。襯底的偏置電壓對(duì)Poly的方塊電阻沒有影響,所以測(cè)試時(shí)襯底是懸空的。

測(cè)量這四種Poly方塊電阻的基本原理都是一樣的,在電阻的一端加載DC電壓1V,另一端接地,從而測(cè)得電流Ip,Poly方塊電阻=(1/Ip)/(L/W),W和L分別是Poly方塊電阻的寬度和長(zhǎng)度。

4.AA方塊電阻

AA方塊電CMOS工藝平臺(tái)的AA方塊電阻有四種類型的電阻,

n型金屬硅化物AA方塊電阻

p型金屬硅化物AA方塊電阻

n型非金屬硅化物AA方塊電阻

p型非金屬硅化物AA方塊電阻

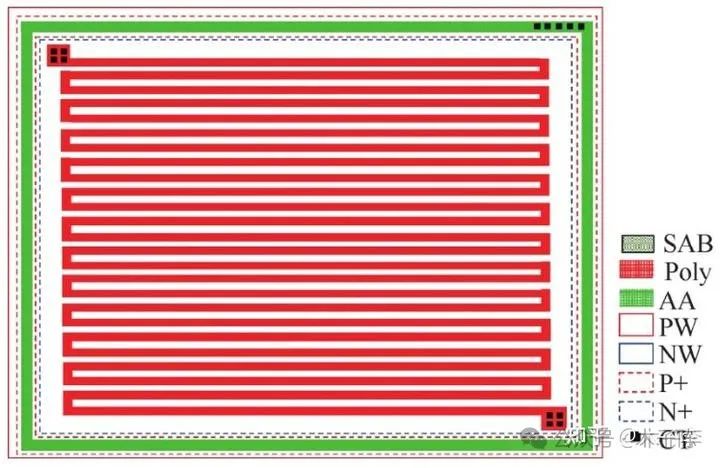

其測(cè)試結(jié)構(gòu)與poly 電阻類似,分為兩種,第一種是狗骨頭狀的測(cè)試結(jié)構(gòu)和蛇形的測(cè)試結(jié)構(gòu)。狗骨頭狀的AA方塊電阻,目的是減小接觸電阻對(duì)AA方塊電阻的影響。n型AA方塊電阻必須設(shè)計(jì)在PW里面,p型AA方塊電阻必須設(shè)計(jì)在NW里面。

蛇形的測(cè)試結(jié)構(gòu)可以增大方塊電阻的個(gè)數(shù),平均化的方塊電阻,可以有效地減小兩端接觸電阻的影響。利用蛇形設(shè)計(jì)的測(cè)試結(jié)構(gòu)的測(cè)試結(jié)果會(huì)比用狗頭狀設(shè)計(jì)的測(cè)試結(jié)構(gòu)更準(zhǔn)確。

測(cè)量n型AA方塊電阻的基本原理是在電阻的一端加載電壓DC電壓1V,另一端和襯底接地,從而測(cè)得電流In,Rs_NAA=(1/I)/(L/W),W和L分別是AA方塊電阻的寬度和長(zhǎng)度。

Metal方塊電阻

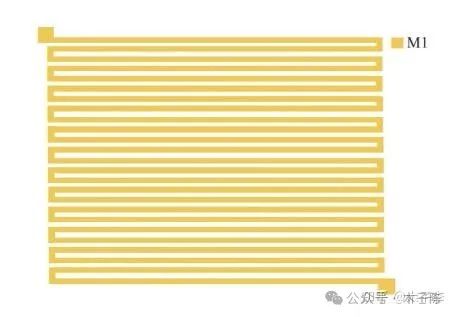

CMOS工藝平臺(tái)的金屬方塊電阻的測(cè)試結(jié)構(gòu)包含該平臺(tái)的所有金屬層,其測(cè)試結(jié)構(gòu)如圖所示:

M1方塊電阻的版圖是蛇形的兩端器件,設(shè)計(jì)成蛇形的目的是盡量增加M1金屬電阻線的長(zhǎng)度,得到更多數(shù)目的M1方塊電阻的整體阻值,對(duì)測(cè)試結(jié)果平均化后,可以減小兩端接觸電阻對(duì)單個(gè)M1方塊電阻的影響。

測(cè)量M1方塊電阻的基本原理是在電阻的一端加載電壓DC電壓1V,另一端接地,從而測(cè)得電流Id,Rs_PW=(1/Id)/(L/W),W和L分別是M1方塊電阻的寬度和長(zhǎng)度。

影響因素:

1) n+和p+離子注入異常;

2)AA刻蝕尺寸異常;

3)Poly刻蝕尺寸異常;

4)硅金屬化(Salicide)相關(guān)工藝。

5)M1刻蝕尺寸異常;

6)淀積金屬層的厚度異常。

-

芯片

+關(guān)注

關(guān)注

459文章

52481瀏覽量

440554 -

CMOS

+關(guān)注

關(guān)注

58文章

6021瀏覽量

238821 -

電阻

+關(guān)注

關(guān)注

87文章

5624瀏覽量

175082 -

電路設(shè)計(jì)

+關(guān)注

關(guān)注

6705文章

2539瀏覽量

214631

原文標(biāo)題:芯片中電阻如何測(cè)試的?

文章出處:【微信號(hào):芯長(zhǎng)征科技,微信公眾號(hào):芯長(zhǎng)征科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

CMOS工藝中方塊電阻的主要類型和測(cè)試方法

CMOS工藝中方塊電阻的主要類型和測(cè)試方法

評(píng)論